概览

设计资源

评估硬件

产品型号带"Z"表示符合RoHS标准。评估此电路需要下列选中的电路板

- EVAL-CN0584-EBZ ($230.00) Fault Protection, Hardware in the Loop Board

- EVAL-CN0585-FMCZ ($747.50) 4-Channel, Simultaneous Sampling, Data Acquisition Platform

器件驱动器

软件(如C代码和/或FPGA代码等)用于与元件的数字接口通信。

FPGA/HDL

优势和特点

- 4个具有可配置电压范围的模拟输入通道

- 4个具有可配置电压范围的模拟输出通道

- ADC测量和DAC建立时间之间的延迟为250 ns

- Rx或Tx路径的模拟前端板建模和仿真与MATLAB和Python兼容

- 由接口连接器提供所有电源和数字连接

参考资料

-

EVAL-CN0584-EBZ User Guide (GitHub)2026/4/16

-

CN0584: Precision Low Latency Development Kit (Rev. 0)2023/5/24PDF1 M

电路功能与优势

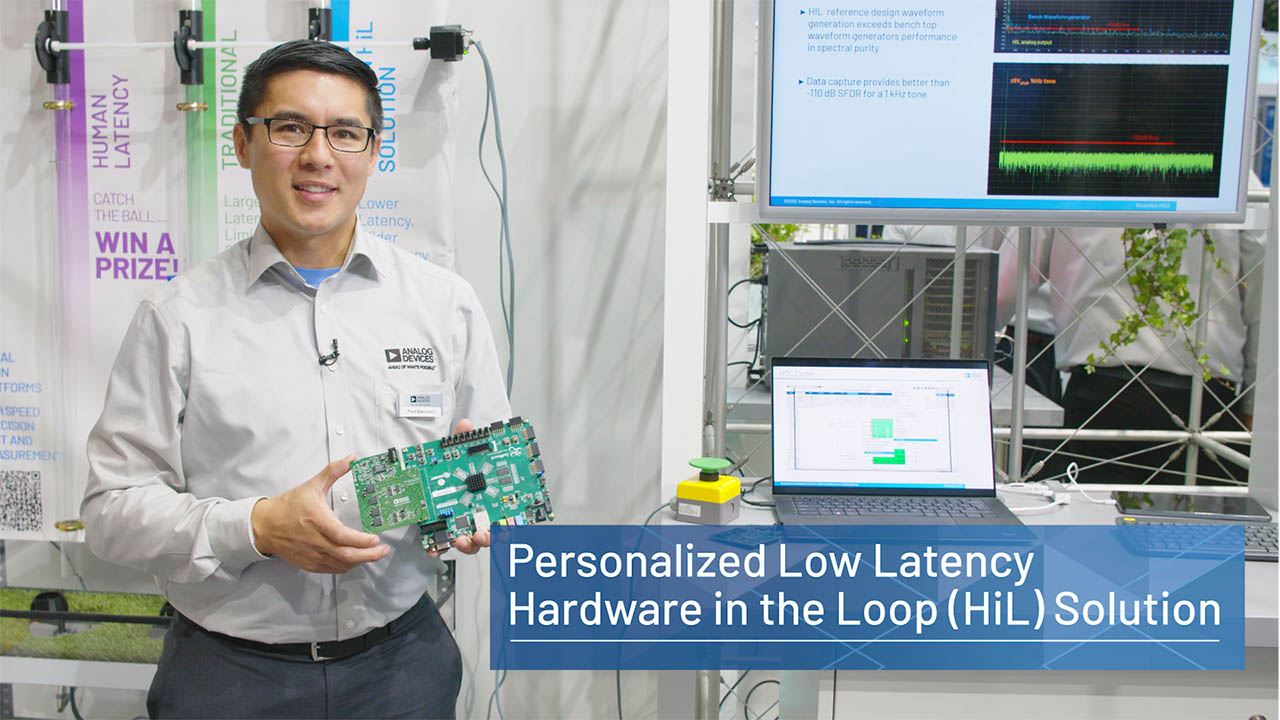

随着现代电子、机电和光电系统的尺寸不断缩小,需要更快的响应时间,并且具有更严格的精度要求,因此仿真、开发和测试这些系统所需的数据采集和硬件在环(HIL)系统的性能也必须与时俱进。对于需要高功率元件的应用尤其重要,例如电机控制器、线性执行器、发电机控制器、电动汽车充电器或汽车和能源行业的电网元件的测试。这些建模组件越来越复杂,导致计算时间增加,需要速度更快的信号采集和生成解决方案。

图1所示电路为一套完整的精密低延迟开发套件,其延迟时间为200 ns,具备高精度输入带宽。该解决方案支持实时HIL仿真和复杂系统的开发,明显简化了数字或混合信号控制回路的设计和测试。它由四个16位模数转换器(ADC)通道和四个16位数模转换器(DAC)通道组成,允许以15 MSPS速率同步采集模拟输入和生成输出波形。

该开发套件提供高达5 MHz的模拟输入带宽以及扩展的模拟和数字连接能力,以简化模拟前端(AFE)设计。模拟输入范围和输出均可通过硬件选择,具有五个双极性输入范围(±1.5 V至±10 V),以及五个输出范围(5 V单极性至±10 V双极性)。

该软件接口可通过Linux工业输入/输出(IIO)框架获得,通过Python、MATLAB®、C、C#和其他语言提供大量调试和开发实用程序以及跨平台应用程序支持。该项目与Simulink®集成,可在其中生成实时模型并将其加载到现场可编程门阵列(FPGA)板中,以便通过外部硬件进行测试。

电路描述

硬件在环

CN0584可对昂贵、复杂或尚未开发的硬件进行硬件在环(HIL)仿真,简化并加速控制系统的开发与测试流程。图2展示了使用CN0584套件的典型HIL设置的总体方框图。

被测器件(DUT)--电子控制单元(ECU)是一种控制器,它能根据其所控制器件的模拟反馈输入,生成数字输出信号。CN0584可对加载了自定义硬件描述语言(HDL)的FPGA板卡所对应的器件进行仿真,从而实现对真实器件性能的实时仿真。

借助CN0584可开展多种HIL仿真,其中之一是对三相电机控制器的负载进行仿真。首先在Simulink®中描述电机的运行特性,再通过该软件生成一个HDL模块,此模块可集成到CN0584的HDL模板中。

将此示例结合图2来看:ECU生成脉宽调制(PWM)控制信号,这些信号由模拟前端板上的三个通道进行调理,再由数据采集与信号生成板上的ADC转换为数字信号。基于这些输入信号,HDL硬件模型会对所模拟电机的各项参数进行仿真,例如电流消耗、转速、转动惯量和位置。这些参数会被转换为模拟信号,并回传至ECU;ECU随后形成闭环,根据该反馈调整其输出的PWM信号。

通过这种方式,可快速评估ECU在以下场景中的表现:正常工作条件、边界情况(例如电机的最大和最小负载)及各类故障模式。上述每种场景都能在仿真中快速实现,且无需额外成本,也不会对物理硬件造成损坏。

模拟测量与信号生成

输入电压范围

CN0584默认支持±10 V的模拟输入电压范围。此外,±5 V、±4.096 V、±2.5 V和±1.5 V这几种输入范围可通过硬件进行选择。

模拟输入保护

CN0584通过采用ADG5421F高压双单刀单掷(SPST)开 关 ,在所有四个ADC和DAC通道上提供模拟输入保护,可实现最高±60 V的过压保护。该保护功能对于存在高功率信号的HIL应用尤为重要,同时也能让用户无需担心接线错误或连接不当问题,从而便捷地调整或修改测试设置。

ADG5421F由+15 V和-15 V电源轨供电,若S1或S2引脚中的任意一个引脚电压超出上述任一电源轨电压VT (0.7 V),该开关将自动关断。对于ADC而言,这些引脚连接至差分输入端口;对于DAC而言,这些引脚则连接至两个DAC通道的输出端口。

ADG5421F还具备故障标志(FF)功能,该故障标志信号会传 输至CN0585,并由MAX7301串行外设接口(SPI) 28端口I/O扩展器读取。该扩展器的SPI端口连接至FMC连接器,最终由FPGA板卡完成读取操作。在正常工作状态下,FF引脚保持高电平;但当检测到过压情况时,FF引脚会变为低电平,以此提示已发生故障。

输出电压范围

CN0584默认支持±10 V的模拟输出电压范围。此外,±5 V、0 V至+2.5 V、0 V至+5 V及0 V至+10 V这几种输出范围可通过硬件进行选择。需注意的是,若要让这些输出范围修改生效,还需更新寄存器设置,寄存器设置可通过提供的软件接口进行控制。

系统性能

延迟

图3展示了用于测量CN0584延迟的测试设置。通过FPGA从存储器中生成1 MHz脉冲正弦波,并将其传输至一个DAC输出通道。借助外部示波器对该DAC输出进行监测,同时通过超小型A型(SMA)线缆将该输出反馈至其中一个ADC通道,作为对应DAC通道的输入信号。使用同一台示波器测量该DAC通道的输出,从而能够对信号经过ADC输入路径、FPGA板卡和DAC输出路径的延迟进行测量。

图4展示了通过示波器捕获的CN0584输出延迟与建立时间。将CN0584的DAC输出设置为ADC输入模式后,向其中一个ADC通道输入施加一个脉冲信号,并对相应DAC通道输出进行监测。从测得的输入信号到DAC输出信号开始上升的延迟约为250 ns;其中,50 ns的延迟源于FPGA内部数据处理,剩余200 ns的延迟则来自ADC数据捕获与DAC更新过程。

模拟输入性能

CN0584的模拟信号采集路径具备极高的无杂散动态范围(SFDR)。图5展示了在采样率为15 MSPS、输入信号为1 kHz ±10 V的正弦波条件下,对ADC数据进行16K点快速傅里叶变换(FFT)的结果。CN0584的SFDR可达105 dB,该指标主要受三次谐波影响;在整个7.5 MHz的输入频率范围内,所有其他杂散信号均低于120 dBc。

图6展示了频率范围扩展至1 MHz的相同频谱图;结果显示,在此范围内不存在其他幅度超过-120 dBm的谐波或杂散信号。

图7展示了ADC的输入频率响应。

输出滤波

每个DAC的输出端均设有一个低通滤波器。图8展示了在将ADC输出作为DAC输入的情况下,该滤波器在7.5 MHz范围内测得的频率响应。

图9展示了输出路径的频率响应;测试时,通过软件生成理想波形,将其加载到循环缓冲区中,再写入DAC。与完整的环回测量相比,本图中的衰减略小,这是因为完整环回测量需将样本传输至FPGA并返回,而本测试的延迟更低。

电源架构

CN0584的所有供电均由CN0585通过模拟前端(AFE)连接器提供。

CN0584使用+15 V和-15 V电源轨,为ADG5421F输入保护开关提供正负供电电压;+12 V和-12 V电源轨为ADA4898-1ADC缓冲放大器提供正负电源电压;+3.3 V电源轨为电可擦可编程只读存储器(EEPROM)电路供电。

软件概述

Python

CN0584可通过pyADI-IIO库与Python进行交互,该库支持器件配置、从ADC捕获输入样本,并可生成需由DAC传输的波形。随后,用户可基于ADC数据对输出波形进行预处理或后处理,从而快速便捷地实现控制回路,或对其他硬件进行仿真。

图10展示了通过Python生成并写入DAC输出的任意波形。 本示例中生成的是峰峰值±10 V、频率5 kHz的正弦波,但也 可实现任意波形的生成。例如在HIL设置中,用户可生成衰 减正弦波、线性调频波、噪声波或失真波形,以仿真存在 故障的硬件。

图11展示了用于分析的实测输入波形,绘制了图10中生成的正弦波。从ADC读取的样本经过处理后,可作为输入传递至用户基于Python实现的算法中,这些算法可用于控制回路、硬件仿真,或其他任何所需的反馈系统。

MATLAB和Simulink

MATLAB®同样可通过高速转换器工具箱与CN0584进行交 互,其支持的功能集与上文所述的Python功能基本一致。除此之外,还能利用Simulink®创建自定义HDL模型,将其加载至FPGA,并通过CN0584实现实时运行。用户可借助现有的Simulink模型或自定义算法,实现控制系统、对实测信号执行数字信号处理(DSP)操作,或仿真硬件功能。

图12展示了在CN0584方框图中,以“接收+发送”双模式插入的Simulink模型的放置。这意味着:ADC捕获的样本会流经该HDL模型并存储到存储器中,而DAC的输出样本也会流经该HDL模型,最终通过CN0584输出。HDL模型也可仅以“接收模式”或“发送模式”插入,两种模式分别仅支持访问ADC输入信号或DAC输出信号。

对于所有插入的接收信号路径模型,经过处理后的样本可通过Python或MATLAB®调用,也可使用IIO示波器软件查看。

常见变化

数据采集与信号生成板及AFE板均支持变体设计。如需了 解信号采集与生成路径的具体变体方案,可参考CN0585电路笔记。

CN0584支持丰富多样的变体设计,能根据特定应用需求定制功能。下文仅列举部分示例(非完整清单),实际应用中还存在更多可能性。通过这些变体设计,可搭建满足HIL测试或其他应用需求的任意系统配置。

对于无需高输入阻抗的应用,可绕过ADA4898输入缓冲放大器。若应用对速度要求较高(放大器带宽至关重要),且可容忍略高的噪声,可改为使用ADA4895;若应用对高带宽要求不高,但需要更宽的输入电压范围,则可选用LTC6373。此外,对于类似应用场景,还可采用自带过压保护功能的ADA4255,它可同时替代ADA4895与ADG5421F。

DAC输出路径同样支持针对特定应用的变体设计。例如,在需要高压工作的场景中,可在输出信号路径中添加ADHV4702,该器件能驱动最高±110 V的输出电压。

电路评估与测试

本节介绍评估EVAL-CN0584-EBZ的相关设置和程序。有关 完整详情和其他重要信息,请访问CN0584用户指南。

设备要求

所需硬件

- EVAL-CN0584-EBZ

- EVAL-CN0585-FMCZ

- Zedboard Xilinx Zinq 开发板

- 16 GB SD卡

- Micro-USB连接线

- USB-C壁式适配器

- 以太网线缆

- 4根SMA线缆

- 4个SMA 50 Ω端接电阻

- 主机PC(Windows/Linux)

软件要求

- 支持115200波特率的UART端口(推荐使用PuTTY)

- IIO示波器

- ADI公司Kuiper Linux镜像

开始操作

- 将ADI公司Kuiper Linux镜像存入SD卡中。

- 为SD卡配置相应的引导文件。

- 通过 AFE 连接器,将 EVAL-CN0584-EBZ 与 EVAL-CN0585-FMCZ 连接。

- 使用FMC连接器,将Zedboard与EVAL-CN0585-FMCZ 连接。

- 为EVAL-CN0585-FMCZ连接电源。

- 将以太网线缆和 UART Micro-USB 连接线连接到Zedboard,另一端均连接至主机。

- 按照图 14 所示,使用 SMA 线缆和端电极,连接EVAL-CN0584-EBZ 的模拟I/O端口。

功能测试设置

- 打开一个PuTTY会话,并连接至Zedboard的COM端口。

- 在 PuTTY 终端中,导航至/boot 文件夹,运行setup_adc.sh 脚本。

- 启动IIO示波器,连接至Zedboard,如图15所示。

- 在IIO示波器中,将AD3552R DAC输出范围设置为±10 V,并将输入源设置为dma_input,如图16所示。

- 切换至IIO示波器的DMM选项卡,确认电压监测值与图17所示数值一致。

- 切换至“DAC数据管理器”,将提供的示例波形加载到目标DAC输出通道,如图18所示。

测试结果

完成电路评估流程后,之前从“DAC数据管理器”选项卡加载的波形必须在IIO示波器的波形窗口中显示,其中会呈现每个ADC通道输入端捕获的信号。图19展示了使用图18中所选示例波形时的示波器显示效果。