TNJ-023:設計開発ストーリー「VGA(可変ゲインアンプ)を使用した広帯域かつ高減衰の可変アッテネータ基板の実現」後編

2016年10月1日公開

はじめに

CQ出版社から、DDS IC AD9834を使用した「すぐ使えるディジタル周波数シンセサイザ基板[DDS搭載]」という本を2012年9月に上梓しました(図1)。私はその執筆・開発プロジェクトの中で、主に94.5dBの減衰量をもつ30MHz広帯域アッテネータ(Attenuator, 以下「ATT」を用います)を担当しました。

この技術ノートでは、前編・後編を通して、製作した94.5dBステップATT回路の実験・試作ネタをご紹介しています。

前編では、構想段階から、周波数特性の改善検討(と言っても、これが「休むに似たり」だったことを、この後編でご説明していきますが)から、パネルdeボードでの試作基板を組み上げたあたりまで説明しました。

後編では、パネルdeボードの試作基板の特性、最終形となる基板のCAD設計と評価、そして特性の最適化などの話題をご説明していきます。

図2は回路全体のブロック・ダイヤグラム(前編の図6の再掲)です。ここで一番の課題は、広い減衰範囲を実現するうえでの飛び込みや迷結合の問題を、どうやって、トラブルを生じさせずに、設計段階から解決していくかということでした。

試作基板(パネルdeボード)で動作と特性を確認してみる

図3は前編でも紹介した、パネルdeボードで作った試作基板に実装したようすです。回路全体の基本動作確認まで完了できました。同図の左側に見えるSMAコネクタが入力で、その上側にAD8369があります。その右側がADG719のATT回路です。減衰した信号が右側のSMAコネクタから出力として出てきます。

試作基板の特性を実測してみる

この試作基板の特性を、ネットワーク・アナライザ(ネットアナ)を用いて測定してみました。図4のプロットは、全体でATT = 0dBとした状態での結果です。30MHzまで問題なく出ています。

図5のプロットは、ADG719により差動固定ATTを有効にして、ATT = 48dBとした状態ですが、図3の写真のような配線ですと信号の飛び込みや迷結合により、高域のフィードスルーが大きくなって、周波数特性が暴れてしまっています。低い周波数ではそれでも-48dBになっているようすがわかります。

最終基板を起こしたときに、迷結合は再チェックです。全体で95dB程度のATT範囲を取るので、以降実施する基板設計も入念にしないといけません!

バッファアンプはADA4891-1を選んだ

AD8369とADG719という役者を使っているというお話をしてきましたが、この基板で出力バッファとして使うオペアンプも決めないといけません。ここではADA4891-1を使うことにしました。

ADA4891-1: オペアンプ、シングル、高速、レールtoレール、低価格

【概要】

ADA4891-1(シングル)はCMOS、高速のオペアンプで、低価格にもかかわらず高性能を提供します。ADA4891-1は真の単電源動作能力を備えており、入力電圧範囲は負側レールの下側300mVまで拡張されています。8ピンのSOICまたは5ピンのSOT-23パッケージを採用しています。

このアンプは-3dB帯域幅が220MHz(G = +1)となっており、今回の用途はG = 2なので十分です。30MHzでもダレが全くない結果が得られています。

しかし周波数が高くなってくると、測定に使用している150 MHzの帯域しかないネットアナも測定限界です…。だれか4395Aあたりを安く譲ってあげるよとかいう、奇特な人などいませんでしょうかね(笑)。ログスイープできるネットアナがいいなぁ。

広いダイナミック・レンジを実現するために基板レイアウトはとても重要

パネルdeボードで基本動作は確認できたので、いよいよ本番用のプリント基板のCAD設計を開始しました。

そのとある日、某社の方がいらっしゃって打ち合わせがあり、その方が「アナログは実装が大事!」とお話されていました。おっしゃるとおりです!この基板もテキトーに(「CAD設計者に丸投げ」ともいいますが)設計すると、思ったような減衰特性が得られません。

ゲインを取る方向なら、「まあ…」、というところかもしれませんが、減衰方向だと、「前編」の技術ノートの最初に示したように、フィードスルー(コモンモードによる飛び込みや迷結合)が高い周波数で出てくるので、簡単ではありません。プリント基板のレイアウトが非常に重要になってきます。

なお、コモンモードは「同相モード」とも呼ばれます。

基板レイアウトはこんなふうに考えた

この問題を考慮した基板レイアウトをご説明します。そのパターン・レイアウトのようすですが、図6(L1…部品面)と図7(L2…半田面)となっています。

スイッチの配線が意外とやっかい

両面基板なので、性能を出すのは結構厄介です。配置の制限で、図6のようにATTレベル設定スイッチが左上、それを読み出すデジタルI/Fが右下になっています。図7のL2を見ていただくとわかるように、この接続配線をアナログ回路のど真ん中を通さないといけません(左側を廻すという考えもありますが、それこそ出力SMAコネクタ側と迷結合しそうです)。

とはいっても設定スイッチなので、レベルが変動するわけでもなく、デジタル的なノイズは考える必要がありません。一番注意すべきはフィードスルーです。入力信号がこのパターンに乗らないように、途中(丁度減衰させる回路の真ん中あたり)に4.7kと0.1uのCR-LPFをそれぞれ配置しました(図6)。最初はこのフィルタを2段配置するような回路だったのですが、「部品が乗りません」ということで、ちょっと心配でしたが1段にしました。

コモンモードの飛び込みや迷結合を避けるための対策回路

さらにコモンモードによる出力への影響を避けるために、図8の回路図のように出力アンプは一旦差動で受けて、シングルエンドに変換する構成にしました。出力アンプとして使っているADA4891-1はCMRR@30MHz = -27dB程度ですので、これに合わせて入力の抵抗4本は絶対精度0.5%(相対マッチングはさらに良いはず)のVISHAYのACASA100121001P100というものを使いました。

また再度図6と図7を参照いただきたいのですが、グラウンドも網目のようにしてビア接続し、できるだけL1-L2間で低いインピーダンスが実現できるように、ベタの配置、ビアでの接続を心がけています。

これらにより、約95dBの減衰特性が30MHzまでの周波数で得られています。

コモンモードの飛び込みや迷結合のしくみはどう考える?

「広い減衰範囲を実現するうえでの、飛び込みや迷結合の問題」ということを、何度もお話させていただきました。「これは具体的にはどう考えるのか?」というのはもっともな疑問と思われます。これについては稿をあらためて、次のTNJ-024で説明してみたいと思います。

正式基板の性能を確認してみる

このプロジェクトの開発も、佳境状態となって、関係者全員で盛り上がっておりました。そのころに私の担当のVGA基板(CAD設計でレイアウトしたもの)も、最終形として出来上がりました。

写真を図9にお見せします。これがマザーボードにピンヘッダで刺さる構成なのですが、マザーボード設計中に「あれ、これ、1ピンの位置、複数のボード間で逆でないですか?」との指摘が。この時点で私のボードは部品実装に入っていたので、びっくり。その後にも「RFINは3 pinではなく、4 pinですよ」とのお言葉。「あ!間違えた!やってしまった!」と完全に動揺してしまいました(笑)。それでも1ピン位置は間違いないことが分かり一安心です。

おもな減衰レベルでの周波数特性を実測してみると…

パネルdeボードで試作していたので、基本動作は一発でうごきました。AD8369に+35dB位のゲインがあるので、これを0dBまで抑え込む必要があり、やっかいでしたが、合計、約95dBのATT可変範囲を30MHz程度まで実現できそうです。

図10からATTなし(本来は0dBですが、-1dBになっています。以降で初段固定ATTの定数を若干調整して補正しました)、図11が48dB差動固定ATTをオンにしてAD8369のATTはナシ、図12が48dB差動固定ATTオンでAD8369のATTもmax(45dB)の状態(合計-93dB-1dB)です。

図12はレベルがかなり低くなるので、ATT出力にプリアンプをつけて、またネットアナはスルー校正時に固定同軸ATTで40dBのゲタをはかせてCAL(校正)を取っています。そのため、このマーカ値に対して-40dBが実際のATT量になります。

図11、図12の「48dB差動固定ATTオン」状態では、30MHz付近が少し盛り上がっています。これは48dB差動固定ATTのアナログスイッチADG719(前編の図8、また本編の図18のIC2, IC5)の端子間容量CDSによるフィードスルーで、周波数特性に暴れができてしまっているからです!

これまでの検討で対策できたかと思ったものですが、シミュレーション結果以外にも要因があるようです。前編の図8(また本編の図18)のR12, R18に直列に接続したインダクタンスL1, L2ではうまく補償ができないようです…。

XL = ωLとXC = 1/ ωCとで、ωに比例と反比例ですからね…。どうやらこれまでの検討は「休むに似たり」だったようです…。

各減衰レベルでの周波数特性を実測してみる

気をとりなおし、精密ではないですが、ぱぱぱっと各ステップでのATTレベルを測定した結果を図13に示します (f = 5MHz)。45dBを超えるところで、AD8369のATTmaxから、差動固定ATTがオンになりAD8369のATTminになるところで1dBちょっとの段差が出ています。

この辺は難しいところで、誤差要因をきちんと見切る必要があり、引き続き検討することにしました。

また図14はステップ間の差分量で、ほぼ3dBずつ変化していることがわかります。若干暴れがありますが、テキトーに測定したので、誤差とも思われますので、これも再測定予定です。

なおこのATT基板は、スイッチで3dBの間を1.5dBずつ可変できるATT回路も用意してあるので、合計64ステップのアッテネータ基板になっています。

「コイツ、出たとこ勝負で運がいいなあ」と思われる人もいるかもしれませんが、回路設計やらレイアウトは相当注意深く行いました。30MHzで-95dB、さて「高い周波数で高減衰」か、はたまた「チョロイ」か…。いかがでしょう。

周波数特性の変動があるが、どうしたら解決できる?!

「48dB差動固定ATTのアナログスイッチADG719(IC2, IC5)の端子間容量CDSによるフィードスルーで周波数特性に暴れが出た」ことで、これまでの検討が「休むに似たり」だったことをお話ししました。

図15の回路図をご覧ください。このように差動ATTとなっていますが、シングルエンドで考えるとR12とR13で分圧するイメージです(下側はR18とR17)。C7で高周波のコモンモードも減衰させるようにもなっています。

ここで周波数特性の暴れの問題、つまりアナログスイッチ(IC2, IC5)のオフ時端子間容量CDSによる影響を軽減するための対策の(付け焼刃的)ストラテジーは2個考えられ、

①図8のR12の大きさを小さくして減衰量を1/2に下げて、2段構成のATTにする

②図8のR12, R13の比率はそのままで、それぞれ大きさを下げる

というものでした。しかし、①はサイズ上の問題があり、また②は、もともとADG719のオン抵抗(typ 2.5Ω)のバラツキが心配なのでR13を少し大きめにしてあり、R12も大きめにせざるをえません。結局は現在のあたりが「落としどころ」です…。

この「30MHzくらいで盛り上がっている問題」の原因であるアナログスイッチ(IC2, IC5)のオフ時端子間容量CDSに対して、まずは図16のようにL1, L2を2.2uHから6.8uHにしてみました。偏差は少なくなっているのですが、うねりがよりややこしくなっています。もともとはL1, L2 = 2.2uHでシミュレーション上ではOKだったのですが、補償不足、なおかつ共振補償(XL = ωLとXC = 1/ ωCで、ωに比例と反比例の関係)なので、結局は局所周波数でしか補償ができません。

あらためてIC2, IC5の端子間容量CDSがいくらか、L1, L2をゼロΩ抵抗にしてみて確認してみました。図17のように、3dB上昇するところが27MHzになっています。これをf = 1/2πCRで計算してみるとCDS = 1.16pF程度と予測されます。もともと7pFくらい?と思われましたが、結構小さいものでした。さて、この補償をどうしたものか???

そうだ!プローブと同じ補償をすればいいんだ

ある朝の寝起きのことですが、「そうだ!オシロのプローブと同じように端子間容量CDSを補償し、改善すればいいのだ」と気がつきました。図18のように、(L1, L2をゼロにしたうえで)R13, R17に並列に補償用コンデンサCaddを接続すればよいのです。

オシロのプローブは、パルス応答を最適にするように、10:1の分圧抵抗に並列にコンデンサが接続されています。これと同じように、図18のIC2およびIC5の5 pin – 6 pin間の容量CDSに対して、補償用コンデンサCaddを選びます。計算上は、

R12×1.16pF = R13×Cadd

とすればいいのですが、実験で確認してみる必要があります。なお1.16pFというのは、図17の3dB上昇ポイントが27MHzで、これをf = 1/2πCRで計算しCDS = 1.16pF程度と予測されたものです。

実際に実験してみる

L = 0Ωのジャンパにしたままで、まずはCadd = 330pFを接続してみました(図19)。フラットにはなりました!でも過補償ぎみです。つぎに150pFを接続してみました(図20)。今度は補償が不足しています。

手持ちのコンデンサが150pFと330pFしかなく、このあいだの180pF, 220pF, 270pFはRSコンポーネンツに注文後のテストになります。でもなんとかなりそうです。

コンデンサを交換しながら最適な点を探し出す

コンデンサ3種類(180pF, 220pF, 270pF)を入手でき、L1, L2の2.2uHをはずし、0Ωのジャンパにしておいたままで、それぞれ順番に接続してみました。図21, 22, 23の順番で、180pF, 220pF, 270pFです。

270pFを追加したとき(図23)がベストなようです。これで一旦クローズにできました!これをもって、その週末に開催する関係者との打ち合わせに安心して望めることとなり、ほっとしました。

ようやく完成!

ということで本プロジェクトの全景が見えてくるような写真を図24にご紹介します。

左がDDS IC AD9834を使用した、書籍に同梱された「ディジタル周波数シンセサイザ基板」です。真ん中が、私が担当したアッテネータ基板です。週末に開催した関係者との打ち合わせでも、「こう見ると壮観ですね!」と関係者とも話をしていました。その後の土日もつづいての佳境状態ゆえ、メールの多かったこと…。

その真ん中の基板にジャンパが見えますが、お気になさらぬように…(汗)。これが先の「RFINが3pinではなく、4pinですよ」とのお言葉どおりのミスでありました(汗)。

全体接続でのフィードスルーなどをチェックする

単体の基板でのフィードスルーが無いことは判りましたが、全体を図24のように接続すると思わぬ迷結合ができてしまうことがあります。そのあたりを最終チェックとしてみました。

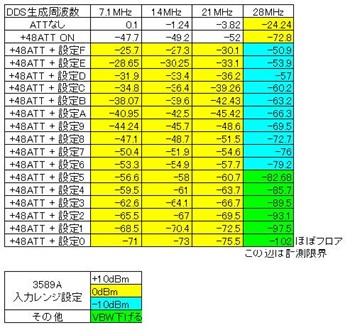

全体を組み合わせてATTの動作を確認してみました。表1をご覧ください。「ディジタル周波数シンセサイザ基板」のAD9834 DDS ICから各周波数の信号を発生させ、各ATTレベルごとの信号レベルをスペクトラム・アナライザで測定したものです。AD9834の信号生成DACの信号出力のしくみにより、sinc関数となる周波数特性となりますので(fDDS = 75MHz)、周波数を高くしていくと、それに応じて(同じATTレベルであっても)信号レベルが低くなっていることがわかります。

全体としてはノイズやら測定誤差により、きちんと3dBステップを踏んで減衰していませんが、最大の28MHzかつATT maxあたりでも3dBの変化量は維持しています。

これは一番危険ともいえるゾーン(一番高い周波数で一番高い減衰量)でも、フィードスルーの問題が無いことを示しています。やれやれです…。

もう一枚、オマケですが、このプロジェクトの核となる、図24右の「ディジタル周波数シンセサイザ基板」のAD9834 DDS ICを7.1MHzで信号生成させ、スパンを10kHzで観測したようすを図25に示します。これもかなり良好な特性ですね。測定はここまでネットワーク・アナライザとして各図での測定プロットをお見せした、150MHzまでの測定レンジである3589Aをスペクトラム・アナライザ・モードにして行いました。3589Aは、帯域は狭いのですが、優れものの測定器です(^_^)

表1. 全体を組み合わせて各周波数、各ATTレベルごとでの信号レベルを測定した

著者について

デジタル回路(FPGAやASIC)からアナログ、高周波回路まで多...