要約

システムエンジニアは、製品開発サイクルの終盤に、電磁干渉(EMI)の適合試験に合格しないのではないかとひどく心配になるものです。不合格となれば、製品の出荷スケジュールが大幅に遅れるだけでなく、多大なコストがかかる電源設計の全面的な見直しが必要になる恐れもあります。このアプリケーションノートでは、適切なフィルタ、低EMIのコンポーネント、低EMIのパワーレギュレータICや低EMIのパワーモジュールを利用する、周到に計画された電源ソリューション設計と、優れたPCBレイアウトやシールド手法によって、EMI試験の初回パスを達成する方法を検討します。

EMIノイズの概要

ある電子機器が電磁干渉(EMI)の発生源となる別の電子機器に接続されているか、そのEMI発生源と同一の電源を共有しているか、またはそのEMI発生源の近くに設置されている場合、EMIによって前者の電子機器の動作が損なわれる可能性があります。EMIには伝導EMIと放射EMIがあり、EMIに関連した問題は、隣接した電子機器が並んで動作することを妨げる場合があります。

EMIの一般的な例は、次のように数多くあります。

- 電子レンジからの干渉が付近のWi-Fi®信号に影響を及ぼす場合がある

- トランスミッタが地元テレビ局からの映像の表示を妨げ、映像を完全に表示不能にするか、またはパターン映像を発生させる場合がある

- 携帯電話と基地局とのハンドシェイクによる通話処理が干渉を引き起こす場合がある(これは航空会社が乗客に対して、飛行中は携帯電話の電源を切るように求める理由です)

- 低高度で飛行する航空機が、ラジオやテレビの音声信号や映像信号を妨害する場合がある

現代の生活では電子機器が至るところに存在することから、電磁適合性(EMC)の問題は重要なトピックの1つとなっています。その結果、標準化団体が組織され、EMIの下でも電子機器が十分な性能を発揮するように保証しています。携帯電話やその他のワイヤレス機器を、ほぼあらゆる電子機器の近くで、ほとんど、またはまったく影響を受けずに運用可能にすることがその目的です。設計者たちは、機器が妨害波を放射しないように、また無線周波数放射の影響を受けにくくなるように対策を講じています。

EMI規格に適合した設計

CISPR 22 EMI規格(欧州ではEN55022と呼ばれることが多い)では、設備、装置、器具を下記の2つのクラスに分類しています。

- クラスB:家庭環境での使用を目的とし、CISPR 22クラスBの放射要件を満たしている設備、装置、器具。

- クラスA:CISPR 22クラスBの放射要件を満たさないものの、そこまで厳格ではないCISPR 22クラスAの放射要件に適合している設備、装置、器具。クラスAの機器には次の警告文を表示する必要があります。「これはクラスA製品です。家庭環境では、この製品は無線干渉を引き起こす恐れがあり、その場合、ユーザーは適切な対策を講じなければならない可能性があります」。

表1、表2、表3、表4は、CISPR 22規格を示しています。

EMI試験は、伝導性放射試験と放射妨害波試験で構成されます。伝導性放射試験は150kHz~30MHzの周波数範囲で実施されます。この範囲でAC電流がラインソースに伝導され、準ピーク値と平均値の2つの方式で測定されます。各方式にはそれぞれ独自の限度があります。

放射妨害波試験は、より高い30MHz~1GHzの無線周波数範囲で実施されます。この範囲は被試験デバイス(DUT)からの放射磁場に相当します。1GHzの試験範囲上限は、内部オシレータ周波数が108MHzまでのDUTに適用されます。表5は、内部オシレータの最大周波数に応じた拡張範囲上限の一覧です。

| Frequency range MHz |

Limits dB (μV) |

|

| Quasi-peak | Average | |

| 0.15 to 0.50 | 66 to 56 | 56 to 46 |

| 0.50 to 5 | 56 | 46 |

| 5 to 30 | 60 | 50 |

| Frequency range MHz |

Limits dB (μV) |

|

| Quasi-peak | Average | |

| 0.15 to 0.50 | 79 | 66 |

| 0.5 to 30 | 73 | 60 |

| Frequency range MHz | Quasi-peak limits dB (μV/m) |

| 30 to 230 | 30 |

| 230 to 1,000 | 37 |

| Frequency range MHz | Quasi-peak limits dB (μV/m) |

| 30 to 230 | 40 |

| 230 to 1,000 | 47 |

| Testing Upper Range | DUT Maximum Internal Oscillator Frequency |

| 1GHz | 108MHz |

| 2GHz | 500MHz |

| 5GHz | 1GHz |

| 6GHz | Higher than 1GHz |

スイッチング電源:ノイズ源はどこにあるのか

スイッチング電源は電磁エネルギーとノイズを生み出すとともに、外部の妨害要因からの電磁ノイズによって影響される場合があります。スイッチング電源が生み出すノイズは、伝導性放射または放射妨害波の形をとります。伝導性放射は電圧または電流の形をとり、これらはそれぞれコモンモードまたは差動モードに分類することができます。さらに、接続線のインピーダンスが有限であるために、電圧伝導が電流伝導を発生させる場合やその逆の場合があります。また、差動モード伝導によってコモンモード伝導が生じる場合やその逆の場合もあります。

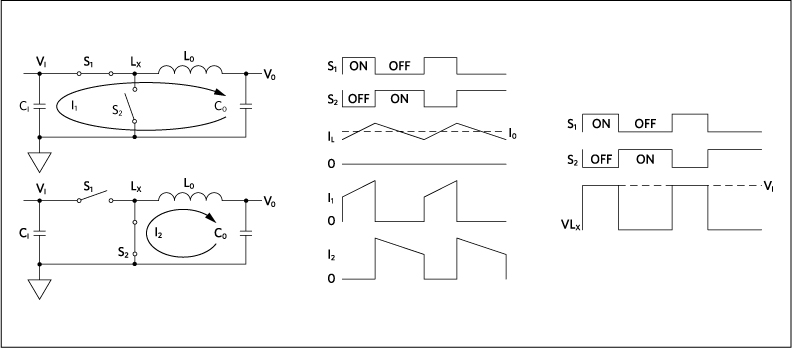

スイッチング電源内のノイズ源を詳しく検討するため、図1にバックレギュレータの簡略回路図を示します。

図1. バックレギュレータの簡略回路図

伝導EMI

図1に示すようなバックレギュレータの入力電流(II)はパルス波形であり、これが放射差動EMIの主な発生源となって電源(VS)に影響を及ぼします。伝導性放射は、主にコンバータの入力における電流波形の急速な変化(di/dt)によって引き起こされます。伝導性放射の値は、ラインインピーダンス安定化ネットワーク(LISN)を使用して、コンバータの入力における電圧(VS)として測定されます。入力コンデンサ(CI)は、AC (パルス)成分を除去します。正味電流(IS)は、IIとICIの差です。ISはDCまたは可能な限り平滑な波形となる必要があります。CIが無限の静電容量を持つ理想的なコンデンサであれば、VIを一定に保ち、実質的にI1のAC成分をすべて除去することにより、一定の(DC)電流をソースVSから流すとともに、ソースインピーダンス(RS)の両端で一定のDC電圧降下を発生させると考えられます。この場合、ISがDC電流であるため、伝導EMIはゼロです。実際には、入力ソースとコンバータの間にπフィルタを使用して、伝導EMIを規制上の限度内に抑え込みます。

伝導性放射は、通常、携帯型のシステムよりも据え置き型のシステムに大きな問題を引き起こします。ポータブル機器はバッテリで動作するため、負荷と電源には伝導性放射を招く外部接続がありません。

放射EMI

放射EMIは、30MHz以上の高周波成分を持つ急速に変化する磁場です。磁場は回路の電流ループによって生み出されます。この磁場の変化は、フィルタやシールドが適切に施されていない場合、付近にある他の回路や機器に影響を及ぼし、放射EMI効果を引き起こします。

図2. バックレギュレータの簡略回路図と高di/dtの電流ループ

図2は、高di/dtの電流ループI1とI2を持つバックコンバータを示しています。電流ループI1は、S1がオンでS2がオフであるオン時間中に導通します。電流ループI2は、S1がオフでS2がオンであるオフ時間中に導通します。電流ループI1とI2のパルス変動に伴い、電流量の変化と伝導ループの面積に比例した磁場強度を持つ磁場の変化が生じます。高di/dtの電流エッジは、レギュレータの放射範囲内で高周波の高調波とEMIを生み出します。これらの電流ループの面積を小さく保つと、磁場強度が最小限に抑えられます。これらの電流エッジを緩やかにすると、スイッチングレギュレータの高周波の高調波成分は減少しますが、緩やかな遷移がエネルギーの浪費を招き、レギュレータの効率に影響を与えます。このアプリケーションノートでは、効率に影響を与えることなくEMI放射を最小限に抑える手法について説明します。

図3. 電流ループが生み出す磁場

電圧ノードLX (ベンダーによってはSWなど別の名称で呼ぶこともある)は、インダクタに接続された矩形波です(寄生リンギングについては差し当たり無視)。LXの高dv/dtの不連続な電圧エッジは、出力インダクタの寄生容量を通じて高周波電流をCOと負荷に結合し、そこからEMIノイズが生み出される場合があります。出力インダクタの寄生容量を極力小さくすると、このノイズ結合の問題を軽減することができます。LXは高周波の寄生リンギングも伴います。これは、LXからGNDへのRCスナバネットワークを使用して低減することが可能です。

上記のEMIノイズ源の原理は、他のスイッチングコンバータトポロジにも同じく当てはまります。ただし、ノイズの重大度は、特定のトポロジの電流および電圧波形によって異なります。連続伝導モードで動作するブーストコンバータを考えましょう。このシナリオでは、入力電流がバックコンバータの場合よりも連続的であるため、コンバータの入力における伝導EMI成分は低減されます。

設計プロセスの当初からEMI適合性を考慮して設計と計画を行うことは、プロジェクトを成功に導く上で不可欠です。対策が遅れると設計プロセスは複雑化し、多大な時間とコストがかかるものとなります。ラインフィルタ、電源設計、適切なPCBレイアウト、シールドなどがEMIを最小限に抑えるための一般的な手法です。

EMIラインフィルタの設計

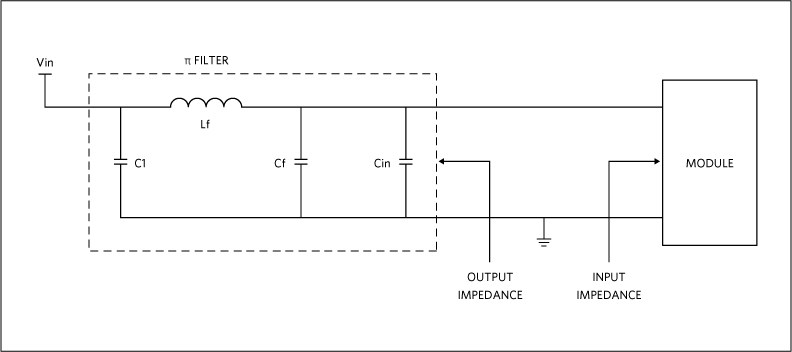

πフィルタを入力ソースとパワーコンバータの間に配置すると、パワーコンバータからの伝導性放射が低減されます。フィルタ部品の選択は、次のような手順で行います。

1. 入力インピーダンスRINを決定します。バックコンバータのワーストケースのクローズドループ入力インピーダンスは、すべての周波数でRIN = RO/D2です。ここで、ROは出力負荷、Dは動作デューティサイクルです。入力インピーダンスが最小になるのは、コンバータが最小入力電源電圧で動作している時です。

例:マキシムのHimalaya SiPパワーモジュールの1つであるMAXM17575を考えましょう。このデバイスは4.5VIN~60VIN、0.9VOUT~54VOUTで最大1.5Aを供給します。MAXM17575の評価キット(EVキット)を例に取ると、最小入力電圧は7.5Vです。出力負荷はRο = Vο/Iο = 5V/1.5A = 3.3Ωです。最大動作デューティサイクルはD = Vο/VINmin = 5V/7.5V = 0.66です。したがって、可能な最小の入力インピーダンスは、RIN = Rο/D2 = 3.3Ω/0.662 = 7.6Ωです。

2. RINより10db以下だけ小さい出力インピーダンスを持つEMIフィルタを設計します。入力フィルタを追加すると、DC-DCコンバータの性能に影響を与える可能性があります。この影響を最小限に抑えるため、フィルタの出力インピーダンスは、コンバータのクロスオーバー周波数までのすべての周波数でパワーコンバータの入力インピーダンスを常に下回る必要があります。

図4. 伝導EMI入力フィルタを入力とパワーモジュールの間に挿入

LCフィルタの共振周波数における出力インピーダンスは最大値であり、次のように求められます。

フィルタの実効インピーダンスは、バックコンバータの入力インピーダンスより10dBだけ小さく、これは入力インピーダンスの3分の1にほぼ等しくなります。MAXM17575の例では、必要なZοは、MAXM17575回路のクロスオーバー周波数(45kHz)までのすべての周波数でRIN/3 = 7.6/3 = 2.5Ω以下です。

EMI適合性を考慮したPCBレイアウトの設計

PCBレイアウトは、EMI適合性に多大な影響を及ぼします。PCBレイアウトに問題があると、パワーコンバータはたとえ電気的設計が完璧でも使い物にならなくなる恐れがあります。ここでは、同じバックコンバータの例に基づいて、EMIノイズ源を最小限に抑えるPCBレイアウトのベストプラクティスをいくつか示します。

- 高di/dtの電流ループを最小化します。

- Lο、Cο、S2を互いの近くに正しく配置して、I2電流ループを最小化します。

- この部品グループ全体をS1とC1の近くに配置して、I1電流ループも最小化します。

- ファラデーシールドを使用します。ファラデーシールドまたはファラデーケージとは、電磁場をブロックするために使用される筺体のことです。一般に、電源システムでファラデーシールドを実装する方法は2つあります。

- 導電材料(銅など)で作られたケージに電源システムや電源装置全体を収めます。電磁場はケージの内部に封じ込められます。しかし、この手法はケージ材料や追加の組立作業にコストがかかるため、高価になるのが普通です。

- PCBの最上層と最下層の両方に備えたシールド用のグランドプレーンをビアで接続したレイアウトにより、ファラデーケージと同様の環境を構成します。高di/dtループはすべてPCBの内層に配置されるため、このファラデーケージの外に磁場が放射されることはありません。この方式(図6)はより低コストであり、通常、EMIの封じ込めには十分です。

バックレギュレータIC (パワースイッチS1とS2を集積したバックコントローラ)を使用する際は、こうした最小化に好都合なピン配列のICを選択することが重要です。パワーモジュールを使用する場合にも同じ考慮が当てはまります。

図5. バックコンバータの高di/dt電流ループ

図6. 多層プリント基板で構成したファラデーシールド

こうしたPCBレイアウトのベストプラクティスに従うことは、EMI規制への適合を達成するための妥当な方法といえます。スイッチングのエッジを緩やかにする場合のように、パワーコンバータの効率を損なうこともありません。

マキシムのHimalaya広入力IC、MAX17502を考えましょう。このデバイスは4.5VIN~60VIN、0.9VOUT~54VOUTで動作し、1Aの電流を供給します。下記の図は、ファラデーシールドの手法(b)を利用したMAX17502のEMI評価キットのPCBレイアウトです。図7aは、ファラデーシールドとして使用される最上層と最下層を示しています。図7bは、配線用の第2層と第3層の内層を示しています。第2層は追加のシールドとして使用されますが、トレースの配線にも使用可能です。このレイアウトでは、高di/dtの電流ループI1とI2は第3層で配線され、この層はファラデーシールド内に完全に収められます。

図7a. ファラデーシールドとして使用される最上層と最下層

図7b. 第2層と第3層(内層)、高di/dtループは第3層で配線

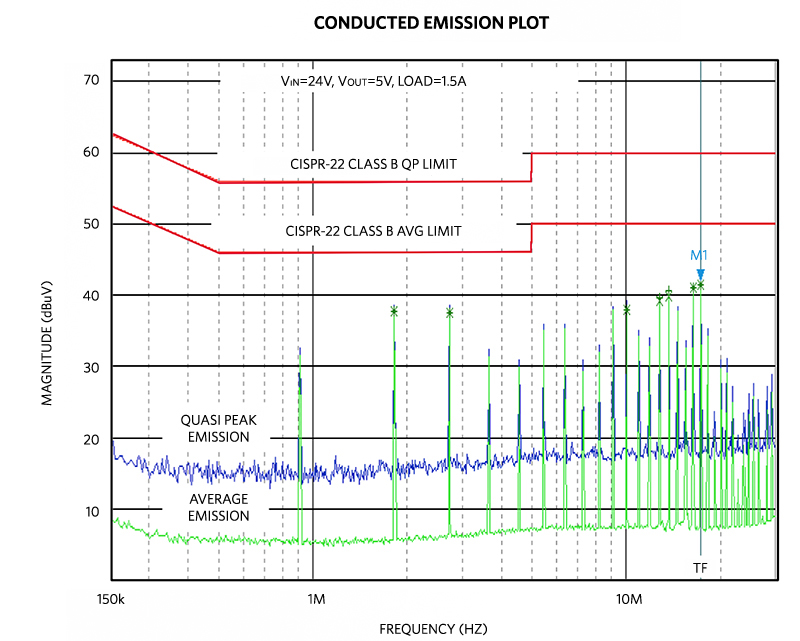

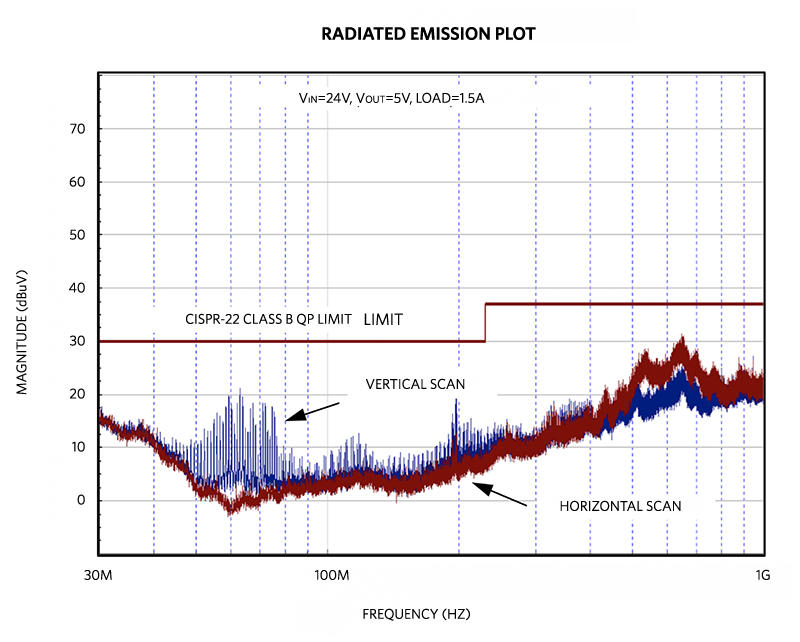

図8と図9は、このMAX17502のEMI評価キットのEMI試験結果を示しています。CISPR 22クラスBを満たしてなお十分に余りある結果です。

図8. MAX17502のEMI評価キットの伝導EMI試験結果。左:準ピーク、右:平均

図9. MAX17502のEMI評価キットの放射EMI試験結果

低EMIのパワー部品

出力インダクタからの磁場も放射され、EMIの問題を引き起こす可能性があるため、低EMIのインダクタを使用すると放射EMIが低減されます。磁場がインダクタ構造内にシールドされ、封じ込められるため、シールドインダクタが推奨されます。磁気エネルギーが自由に放射されるようなタイプのインダクタは避けてください。シールドインダクタを使用し、優れたPCBレイアウト手法を採用したパワーモジュールは、良好なEMI性能を示します。

低EMIのパワーレギュレータとパワーモジュール

マキシムのHimalayaレギュレータおよびパワーモジュールファミリは、低EMIのパワーインダクタや優れたPCBレイアウト手法を採用し、本質的に低EMIの電源ソリューションを実現します。Himalayaソリューションを使用すると、市場にある他の過度に単純なスイッチャを使用する場合とは異なり、適合性について心配する必要がありません。マキシムでは、最適コストでCISPR 22 (EN 55022)を満たすことができるように、IC、モジュール、リファレンスレイアウト例についてあらゆる作業を行っています。以下に、MAXM17575を例としたEMI試験結果、および入力EMIフィルタに関する情報を示します。

| Test Article (EUT) | MAXM17575 | Result | PASS-EN55022 (CISPR 22) CLASS B |

| EUT Revision | REV-P1 | ||

| Input Voltage | 24V-Positive | Output Voltage | 5.0V |

| Switching Frequency | 900KHz | Output Current | 1.5A |

EMIフィルタの構成:伝導EMI試験

図10. MAXM17575のEVキットによる伝導EMI試験用のEMIフィルタ構成

図10. MAXM17575のEVキットによる伝導EMI試験用のEMIフィルタ構成

| Filter Component | Value | Part Number | Manufacturer |

| Inductor-L1 | 10μH | PA4332.103NLT | Pulse Electronics |

| Capacitor-C1 | 0.1μF | GRM188R72A104KA35 | Murata |

| Capacitor-C2, C3 | 1μF | GRM32CR72A105KA35 | Murata |

| Capacitor-C4 | 10μF | EEE-TG2A100P | Panasonic |

| Capacitor-CIN | 2.2μF | GRM32ER72A225KA35 | Murata |

図11. MAXM17575のEVキットによる伝導EMI試験結果。青:準ピーク、緑:平均

EMIフィルタの構成:放射EMI試験

図12. MAXM17575のEVキットによる放射EMI試験用のEMIフィルタ構成

MAXM17575は、放射EMIが本質的に極めて低く抑えられています。伝導EMI試験用に示した入力フィルタは不要であり、放射試験では使用していません。入力フィルタを使用すると、適合性を確保する上で一層の余裕が放射試験結果に追加されます。

| Filter Component | Value | Part Number | Manufacturer |

| Capacitor-C1 | 0.1μF | GRM188R72A104KA35 | Murata |

| Capacitor-C2 | 10μF | EEE-TG2A100P | Panasonic |

| Capacitor-CIN | 2.2μF | GRM32ER72A225KA35 | Murata |

図13. MAXM17575のEVキットによる放射EMI試験結果

結論

設計サイクルの最も早い段階で設計上、EMI適合性を考慮することは、プロジェクトを成功に導く上で非常に重要です。このアプリケーションノートでは、EMIを最小限に抑えるための一般的な手法や、ラインフィルタ設計、優れたPCBレイアウト、およびシールド手法のガイドラインや例について説明しています。適切なフィルタ(低EMIのPMIC、コンポーネントやパワーモジュール)を使用する周到に計画された設計と、優れたPCBレイアウト手法やシールドを適用すれば、EMI試験の初回パスに向けて着実に進むことができます。