概要

設計リソース

評価用ボード

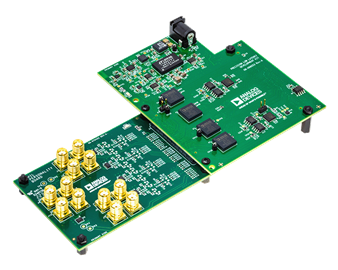

型番に"Z"が付いているものは、RoHS対応製品です。 本回路の評価には以下の評価用ボードが必要です。

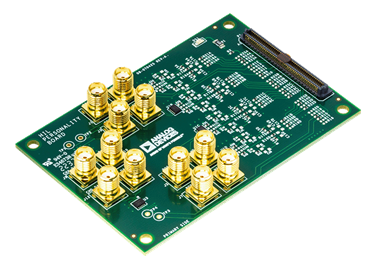

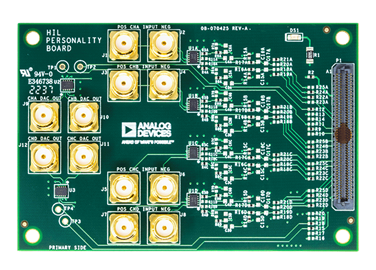

- EVAL-CN0584-EBZ ($230.00) Fault Protection, Hardware in the Loop Board

- EVAL-CN0585-FMCZ ($747.50) 4-Channel, Simultaneous Sampling, Data Acquisition Platform

デバイス・ドライバ

コンポーネントのデジタル・インターフェースとを介して通信するために使用されるCコードやFPGAコードなどのソフトウェアです。

FPGA/HDL

機能と利点

- 電圧レンジを設定可能な4つのアナログ入力チャンネル

- 電圧レンジを設定可能な4つのアナログ出力チャンネル

- ADC測定からDACがセトリングするまでの遅延:250ns

- RxパスまたはTxパスのアナログ・フロント・エンドの基板モデリングおよびシミュレーションはMATLABおよびPythonに対応

- 電源接続およびデジタル接続はすべてインターフェース・コネクタを介して実現

マーケット & テクノロジー

使用されている製品

参考資料

-

EVAL-CN0584-EBZ User Guide (GitHub)2026/04/16

-

CN0584: 高精度低遅延開発キット (Rev. 0)2023/05/24PDF1 M

回路機能とその特長

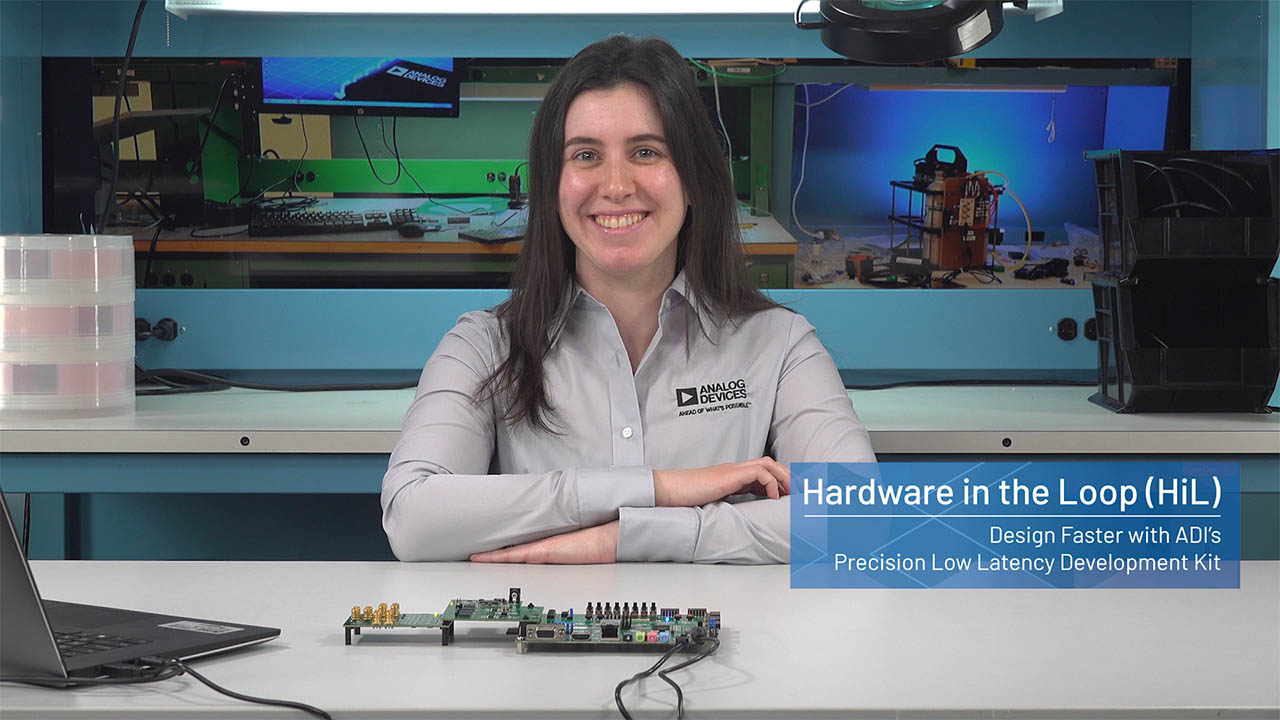

最新の電子システム、電子機械システム、電気光学システムは、ますますサイズが縮小し、応答時間が短縮し、精度条件が厳しくなっていることから、これらのシステムのシミュレーション、開発、テストに必要なデータ・アクイジション性能とハードウェア・イン・ザ・ループ(HIL)システムもこれに見合ったものになる必要があります。このことは特に、モータ・コントローラ、リニア・アクチュエータ、ジェネレータ・コントローラ、電気自動車用チャージャ、あるいは自動車産業やエネルギー産業向けのパワー・グリッド用素子などをテストする場合のように、大電力素子を必要とするアプリケーションに当てはまります。これらのモデル化されたコンポーネントの複雑さが増していることは、計算時間の増加を招き、信号のアクイジションや生成をより高速に行うソリューションが必要となってきます。

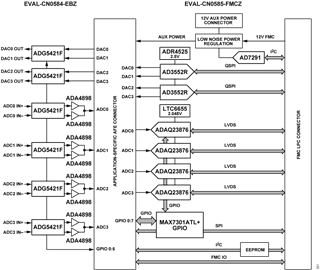

図1に示す回路はフル機能の低遅延開発キットで、遅延時間は200nsです。また、高精度の入力帯域幅を備えています。このソリューションにより、リアルタイムのHILソリューションと複雑なシステムの開発が可能となり、デジタルまたはミックスド・シグナルの制御ループの設計やテストが著しく容易になります。この開発キットは、4個の16ビットA/Dコンバータ(ADC)チャンネルおよび4個の16ビットD/Aコンバータ(DAC)チャンネルを内蔵し、アナログ入力の同期アクイジションや15MSPSの出力波形の生成が可能です。

開発キットは、最大5MHzのアナログ入力帯域幅を備え、アナログおよびデジタルの接続性が向上しているために、アナログ・フロント・エンド(AFE)の設計が簡素化できます。アナログの入力レンジと出力は、どちらも±1.5V~±10Vの5通りのバイポーラ入力レンジと5Vユニポーラ~±10Vバイポーラの5通りの出力レンジをハードウェアにより選択できます。

ソフトウェア・インターフェースは、Linuxの産業用入出力(IIO)フレームワークを通じて使用でき、デバッグ・ユーティリティや開発ユーティリティのホスト機能を提供すると共に、Python、MATLAB®、C、C#、およびその他の言語を通じたクロス・プラットフォーム・アプリケーションをサポートします。プロジェクトはSimulink®を統合化しているため、リアルタイム・モデルを生成してFPGA(フィールド・プログラマブル・ゲート・アレイ)ボードにロードし、外付けハードウェアでテストできます。

回路説明

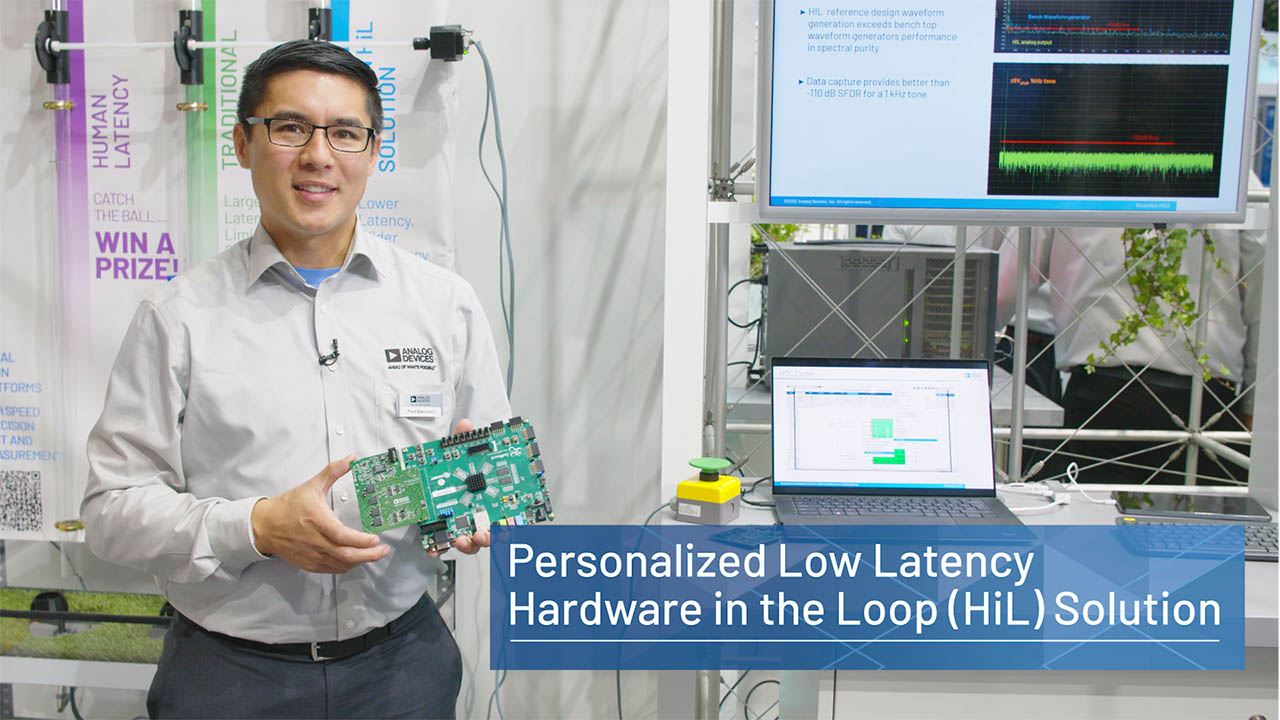

ハードウェア・イン・ザ・ループ

CN0584は、高価な、複雑な、あるいはまだ開発されていないハードウェアのHILエミュレーションを用いて、制御システムの開発およびテスト・プロセスを簡素化し、加速します。図2は、CN0584キットを用いた代表的なHILのセットアップを示すハイレベル・ブロック図です。

テスト対象デバイス(DUT)である電子制御ユニット(ECU)は、制御しているデバイスからのアナログ帰還入力に基づきデジタル出力信号を生成するコントローラです。CN0584はFPGAボードにロードされているカスタムのハードウェア記述言語(HDL)でデバイスをエミュレートし、現実的な性能をリアルタイムでシミュレーションします。

CN0584を用いて実行できるHILシミュレーションの一例は、3相モータ・コントローラの負荷をエミュレートすることです。モータの動作は、まずSimulink®に記述されます。これを用いることで、CN0584 HDLテンプレートに統合できるHDLモジュールを生成します。

この例を図2に適用すると、ECUはパルス幅変調(PWM)制御信号を生成し、この信号に対しアナログ・フロント・エンド・ボードの3つのチャンネルによってコンディショニングが行われ、データ・アクイジションと信号発生ボードのADCによってデジタル化されます。HDLハードウェア・モデルは、これらの入力に基づき、モデリング対象のモータの電流量、速度、慣性、位置などのパラメータをシミュレーションします。これらのパラメータは、アナログ信号に変換され、ECUに戻されます。その後ECUはループを閉じてこの帰還信号に基づき出力PWM信号を調整します。

ECUは、公称動作条件、コーナ・ケース(例えば最大および最小のモータ負荷)、様々な不具合モードなどについて短時間で評価され、その各々は、関連コストが追加されたり物理的ハードウェアが損傷したりすることなく、シミュレーションに手早く組み込むことができます。

アナログ測定と信号発生

入力電圧レンジ

CN0584はデフォルトで、±10Vのアナログ入力電圧レンジに対応します。その他の入力レンジは±5V、±4.096V、±2.5V、±1.5Vで、これらはハードウェアにより選択できます。

アナログ入力保護

CN0584は、ADG5421F高電圧デュアル単極単投(SPST)スイッチを用いて4つのADCチャンネルおよびDACチャンネルすべてにアナログ入力保護機能を備えており、最大±60Vの過電圧保護を行います。この保護は、高電圧信号が存在する可能性があるHILアプリケーションで特に重要です。また、この保護により、ユーザは、誤配線や不適切な接続を心配することなく、セットアップを適応させたり変更したりできます。

ADG5421Fは、+15Vおよび−15Vの電源レールで給電され、S1ピンまたはS2ピンのどちらかがこれらの電圧レベルをVT(0.7V)だけ超えた場合、スイッチは自動的にオフになります。ADCの場合、これらのピンは作動入力ポートに接続されます。DACの場合はこれらのピンは2つのDACチャンネル出力ポートに接続されます。

また、ADG5421Fにはフォルト・フラグ(FF)もあり、これはCN0585に伝送され、MAX7301シリアル・ペリフェラル・インターフェース(SPI)、28ポートI/Oエキスパンダによって読み出されます。このエキスパンダのSPIポートはFMCのコネクタに接続されFPGAボードで読み出されます。通常動作ではFFピンはハイにプルアップされています。ただし、過電圧状態が検出されると、FFピンはローにプルダウンされてフォルトが発生したことを通知します。

出力電圧レンジ

CN0584はデフォルトで、±10Vのアナログ出力電圧レンジに対応します。その他の出力レンジは±5V、0V~+2.5V、0V~+5V、0V~+10Vで、これらはハードウェアにより選択できます。なお、レジスタ設定は、提供されたソフトウェア・インターフェースを用いて制御され、これらの出力レンジの変更が生じた場合にはこの設定も更新する必要がある点に注意してください。

システム性能

遅延

図3に、CN0584の遅延を測定するために用いたテスト・セットアップを示します。FPGAを用いて1MHzのパルス・サイン波がメモリから生成され、1つのDAC出力チャンネルに送られます。このDAC出力は、外付けのオシロスコープでモニタされ、サブミニチュア・バージョンA(SMA)ケーブルを介していずれかのADCチャンネルへの入力として帰還されます。このADCチャンネルでは対応するDACチャンネルへの入力信号として用いられます。このDACチャンネルの出力が同じオシロスコープを用いて測定され、ADC入力パス、FPGAボード、DAC出力パスを通じた信号遅延の測定が可能になります。

図4に、CN0584の出力の遅延とセトリング・タイムのオシロスコープ画像を示します。CN0584のDAC出力をADC入力モードに設定し、パルスをいずれかのADCチャンネル入力に印加して、対応するDACチャンネルの出力をモニタしたものです。入力信号が測定されてからDAC出力信号が立上がり始めるまでの遅延は、約250nsです。この遅延のうち50nsは内蔵FPGAのデータ処理が原因で、残りの200nsの遅延はADCのデータ取得とDAC更新に起因します。

アナログ入力性能

CN0584のアナログ入力アクイジション・パスは、非常に高いスプリアスフリー・ダイナミック・レンジ(SFDR)を示します。図5に、1kHzで±10Vのサイン波信号を入力し、サンプリング・レートを15MSPSとした場合のADCデータについて、16,000ポイントのFFTを示します。CN0584は105dBのSFDRを実現し、3次高調波が支配的となっています。その他のスプリアスはすべて、7.5MHzの入力周波数範囲全域にわたり120dBc未満です。

図6に、同じスペクトル・プロットの周波数範囲を1MHzまで拡張したものを示します。−120dBmを上回るその他の高調波やスプリアスは存在しないことが示されています。

図7に、ADCの入力周波数応答を示します。

出力フィルタリング

各DAC出力には、ローパス・フィルタがあります。図8に、ADC出力をDAC入力として用い7.5MHzまで測定した場合のフィルタの周波数応答を示します。

図9に、理想的な波形をソフトウェアで生成し、循環バッファにロードしてDACに書き込んだ場合の、出力パスの周波数応答を示します。このグラフでは、サンプルをFPGAに送り再度戻す必要のある完全なループバック測定の場合と比べ、低遅延であるためにわずかに減衰が小さくなっています。

電源アーキテクチャ

CN0584の電力はすべて、AFEコネクタを通じてCN0585によって供給されます。

CN0584は+15Vと−15Vのレールを用いてADG5421F入力保護スイッチに正負の電源電圧を供給します。+12Vおよび−12Vのレールは、ADA4898-1 ADCバッファ・アンプに正負の電源電圧を供給します。+3.3VのレールはEEPROM回路に給電します。

ソフトウェアの概要

Python

CN0584は、pyADI-IIOライブラリを用いてPythonとインターフェースでき、それによって、デバイス設定、ADCからの入力サンプルのキャプチャ、DACによって送信される波形の生成を行うことができます。その後、出力波形はADCのデータに基づき前処理または後処理が可能であるため、ユーザは制御ループや他のハードウェアのシミュレーションを手早く簡単に実行できます。任意波形をPythonで生成しDAC出力に書き込む例を図10に示します。この例は、ピークtoピーク電圧が±10Vで5kHzのサイン波の生成を示すものですが、任意の波形を生成できます。例えば、HILのセットアップに対し、減衰のあるサイン波のチャープ波形、ノイズ波形、あるいは歪み波形を生成して、欠陥のあるハードウェアをシミュレーションできます。

図11に、測定した入力波形を解析用に示します。これは図10で生成したサイン波をプロットしたものです。ADCから読み出したサンプルは、制御ループ、ハードウェア・エミュレーション、あるいはその他必要な帰還システムを実装しているユーザ実装Pythonアルゴリズムへの入力として処理し使用できます。

MATLABおよびSimulink

MATLAB®を使用してもCN0584とインターフェースすることができ、High Speed Converter Toolboxを使用して、上述のPythonについての説明とほとんど同じ機能セットが利用できます。これに加え、Simulink®を用いると、CN0584を使ってFPGAに読み込みリアルタイムで実行できる、カスタムHDLモデルを作成できます。また、既存のSimulinkモデルやカスタム・アルゴリズムを使用して制御システムを実装し、測定した信号にデジタル信号処理(DSP)を施したりハードウェア機能をエミュレートしたりできます。受信モードと送信モードの両方に挿入したSimulinkモデルのCN0584のブロック図における配置を、図12に示します。これは、ADCサンプルがHDLモデルを通じて渡されメモリに保存されること、また、DACサンプルがHDLモデルを通じて渡されCN0584に出力されることを意味します。HDLモデルは、ADC入力にのみアクセスできる受信専用モード、またはDAC出力にのみアクセスできる送信専用モードに挿入することもできます。

挿入されたどの受信信号パスモデルについても、その変更されたサンプルには、PythonまたはMATLAB®を用いてアクセスしたり、IIO Oscilloscopeソフトウェアを用いて表示したりできます。

バリエーション回路

データ・アクイジションおよび信号発生ボードとAFEボードのどちらについてもバリエーションが可能です。信号のアクイジション・パスと発生パスのバリエーションについては、CN0585回路ノートを参照してください。

CN0584では、機能を特定のアプリケーションに合わせて調整できるよう、幅広いバリエーションが可能です。すべての例が網羅されているわけではありませんが、追加して実行可能なものが多数あり、HIL試験やその他のアプリケーションに必要な任意のセットアップを作成できます。

高入力インピーダンスを必要としないアプリケーションでは、ADA4898入力バッファ・アンプをバイパスするができます。アンプの帯域幅が重要でノイズが若干高くても許容できる高速アプリケーションでは、ADA4895を代わりに使用できます。広帯域幅はそれほど重要でなくても入力電圧の範囲が広いことが必要なアプリケーションでは、LTC6373を使用できます。または、過電圧保護機能を持つADA4255を同じアプリケーションに使用すると、ADA4895とADG5421Fの両方を置き換えることができます。

アプリケーション固有のバリエーションは、DAC出力パスについても可能です。例えば、高電圧での動作には、出力を±110Vまで駆動できるADHV4702を出力信号パスに追加できます。

回路の評価とテスト

このセクションでは、EVAL-CN0584-EBZを評価するためのセットアップと手順を説明します。詳細およびその他の情報については、CN0584ユーザ・ガイドを参照してください。

必要な機器

必要なハードウェア

- EVAL-CN0584-EBZ

- EVAL-CN0585-FMCZ

- Zedboard Xilinx Zinq開発ボード

- 16GBのSDカード

- Micro-USBケーブル

- USB-C電源アダプタ

- イーサネット・ケーブル

- SMAケーブル4本

- SMA 50Ω終端4個

- ホストPC(Windows/Linux)

必要なソフトウェア

- 115200のボー・レートが可能なUART端子ケーブル(PuTTYを推奨)

- IIO Oscilloscope

- アナログ・デバイセズのKuiper Linuxイメージ

開始にあたって

- SDカードにアナログ・デバイセズのLinux Kuiperイメージを書き込みます。

- 適切なブート・ファイルでSDカードを設定します。

- AFEコネクタを介してEVAL-CN0584-EBZをEVAL-CN0585-FMCZに取り付けます。

- FMCコネクタを用いてZedboardをEVAL-CN0585-FMCZに接続します。

- 電源をEVAL-CN0585-FMCZに接続します。

- イーサネット・ケーブルとUART micro-USBケーブルをZedboardに接続し、他端をホストPCに接続します。

- SMAケーブルと終端を用いて図14に示すようにEVAL-CN0584-EBZのアナログI/Oポートを接続します。

機能テストのセットアップ

- ZedboardのCOMポートへのPuTTYセッションを開きます。

- PuTTYのターミナルで、/bootフォルダに移動し、setup_adc.shスクリプトを実行します。

- 図15に示すように、IIO Oscilloscopeを起動しZedboardに接続します。

- 図16に示すように、IIO Oscilloscopeで、AD3552RのDAC出力レンジを±10Vに設定し、入力源をdma_inputに設定します。

- IIO Oscilloscopeの[DMM]タブに移動し、電圧モニタ値が図17に示したものと一致していることを確認します。

- 図18に示すように、[DAC Data Manager]に移動し、得られたサンプル波形を目的のDAC出力チャンネルにロードします。

テスト結果

回路評価手順に従った後、[DAC Data Manager]タブで読み込んだ波形は、IIO Oscilloscopeの波形ウィンドウに表示されるはずです。これには各ADC入力チャンネルでキャプチャされた信号が表示されています。図19に、図18で選択した波形の例を用いた場合の表示例を示します。