概要

設計リソース

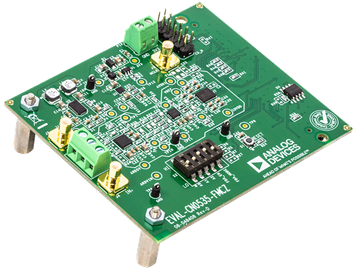

評価用ボード

型番に"Z"が付いているものは、RoHS対応製品です。 本回路の評価には以下の評価用ボードが必要です。

- EVAL-CN0535-FMCZ ($203.03) High Performance, Alias Free Data Acquisition Board

- EVAL-SDP-CH1Z ($458.85) System Demonstration Platform

デバイス・ドライバ

コンポーネントのデジタル・インターフェースとを介して通信するために使用されるCコードやFPGAコードなどのソフトウェアです。

機能と利点

- エイリアス・フリー測定システム

- AC性能とDC性能を最適化

- 広いアナログ入力電圧範囲(+/-12V)

- FMC互換のフォーム・ファクタ

マーケット & テクノロジー

使用されている製品

参考資料

-

CN-0535 User Guide2021/02/03WIKI

-

CN-0535: 柔軟なデータ・アクイジション・システムを実現するための高性能エイリアス・フリー測定プラットフォーム (Rev. 0)2021/02/04PDF281 K

-

CN0535 Mbed Example Program Setup2025/09/05

CN0535 Mbed Example Program Setup2025/09/05 -

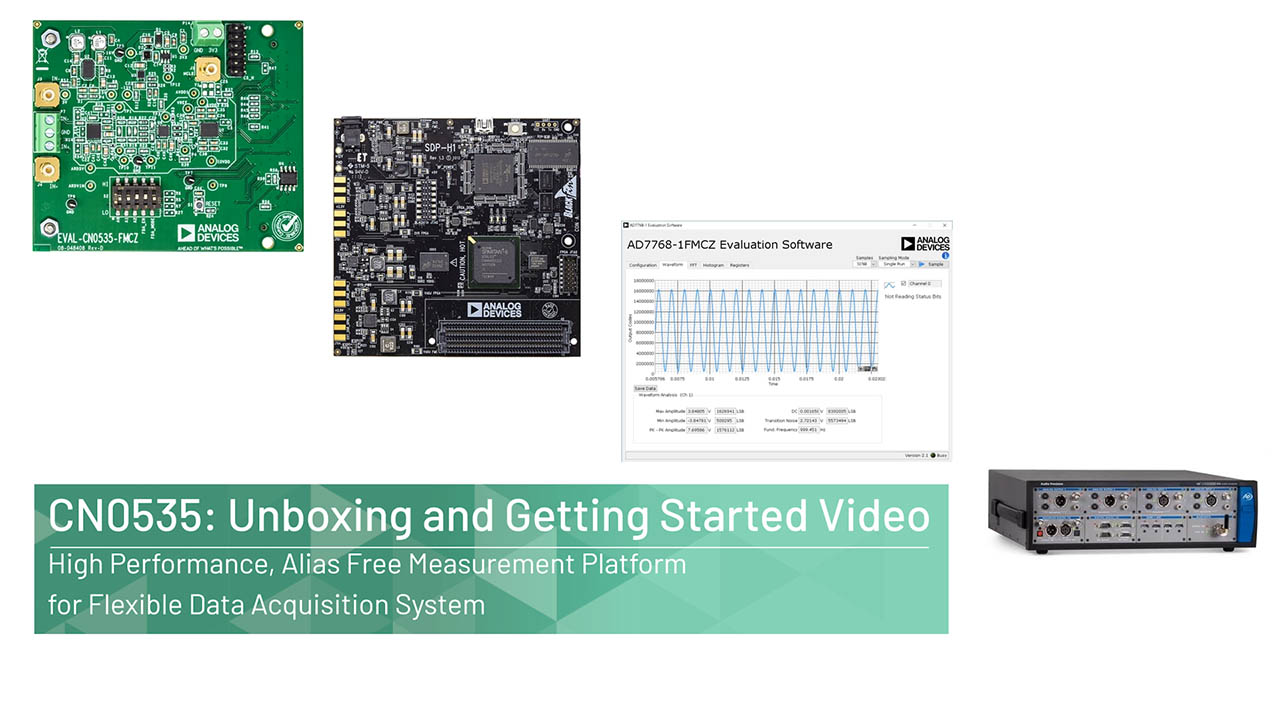

CN0535 Unboxing and Getting Started Video2025/09/05

CN0535 Unboxing and Getting Started Video2025/09/05

回路機能とその特長

データ・アクイジション(DAQ)システムでは、温度、力、加速度、振動などの実世界の物理現象が測定され、これらの測定値はデジタル値に変換されてデータ処理が行われたり、保存されたり、遠隔地に伝送されたりします。代表的な DAQ システムは、センサー、アナログ・フィルタリング/シグナル・コンディショニング回路、A/D コンバータ(ADC)、およびデジタル・コントローラで構成されています。DAQ ソリューション用の構成要素は、アプリケーションごとに選択されます。DAQ システムの中には、制御ループやマルチプレクス・アプリケーション向けに高速のセトリング・フィルタを使用して、システム全体でセンサーからの DC 誤差を最小限に抑えるように設計されるシステムもあります。また一方で、歪みを低く抑えると共に周波数応答を平坦にして、優れた AC 性能を実現するように設計されるシステムもあります。

図 1 に示す DAQ システムは、これらの設計課題の多くを 1 つの柔軟な DAQ プラットフォーム内に簡素化したもので、広範なAC アプリケーションと DC アプリケーションで使用できます。

入力電圧範囲が広く、入力インピーダンスが高く、しかも入力コモンモード電圧が高いため、シグナル・コンディショニングを付加することなしに、ほとんどのセンサーや信号源を入力に直接接続できます。ADC の入力範囲を最適に利用できるよう、システムには入力信号を減衰または増幅するプログラマブルなゲイン・ブロックが備わっています。

このシステムでは DC 性能と AC 性能が最適化されているため、アナログ入力帯域幅全体にわたって極めて高い性能を発揮することができます。入力バイアス電流が低いため、センサーの出力インピーダンスに起因する DC 誤差が最小限に抑えられます。また、同相ノイズ除去比(CMRR)が高いため、特にセンサーが DAQ システムから離れている場合に、周囲から侵入する同相ノイズの影響が最小限に抑えられます。これらの効果により、コンバータの AC 性能を犠牲にすることなく、DC 誤差が最小に保たれます。

ADC には帯域幅とデータ・レートを調整できる完全にプログラマブルなデジタル・フィルタが備えられているため、特定のシステム条件に適合することができます。システムのアナログ・フィルタによって、サンプリング周波数の倍数の周波数が除去されるため、エイリアシングの問題が解消されます。

回路説明

ADC

このソリューションの心臓部であるAD7768-1は低消費電力、高性能の Σ-Δ ADC で、AC信号と DC 信号の両方を正確に変換するための Σ-Δ 変調器とデジタル・フィルタを内蔵しています。AD7768-1 では、入力帯域幅、出力データ・レート(ODR)、および消費電力の間の設定と最適化を柔軟に行うことができます。

ODR は、アプリケーション条件ごとにプログラム可能です。AD7768-1 の ODR を計算するには、次式を使用します。

ODR =(FMOD/DEC RATE)

ここで、

FMOD は、AD7768-1 の変調器の周波数です。

DEC_RATE は、デシメーション・レートです。

FMOD を計算するには、次式を使用します。

FMOD =(MCLK/MCLK DIV)

ここで、

MCLK は、マスタ・クロックの周波数です。

MCLK_DIV は、印加された MCLK と、ADC の変調器が使用するクロックとの比です。

AD7768-1 は、広範なシステム条件を満たす幅広いデジタル・フィルタ処理機能を備えています。このフィルタ・オプションによって、周波数範囲全域でゲイン誤差条件の厳しい周波数領域測定、線形位相応答条件(広帯域、低リップル、有限インパルス応答(FIR)フィルタ)、制御ループ・アプリケーションで使用される低遅延経路(sinc5 または sinc3)、50Hz または 60Hzのライン周波数を除去する sinc3 フィルタを設定可能な DC 入力測定などの構成が可能になります。すべてのフィルタで、デシメーションのプログラムが可能です。

システム全体の帯域幅はデジタル・フィルタによって決まります。代表的なデジタル・フィルタの設定値については、入力信号の帯域幅を記載した表 1 を参照してください。また、選択されたデジタル・フィルタの−3dB 帯域幅は、次式を使用して計算できます。

広帯域低リップル FIR フィルタ = 0.433 × ODR

Sinc5 低遅延フィルタ = 0.204 × ODR

Sinc3 低遅延フィルタ = 0.2617 × ODR

| Digital Filter | Decimation Rate | ODR (kSPS) | Input Signal Bandwidth (kHz) |

| Low Ripple FIR | 32 | 250 | 108.2 |

| Sinc5 | 8 | 1000 | 204 |

| Sinc3 | 32 | 250 | 65.425 |

アプリケーションで用いるフィルタの条件が、デフォルトのフィルタ・オプションと合わない場合には、特別仕様のデジタル・フィルタを設計してメモリにアップロードするオプションがあります。このアップロードを行うと、デフォルトの低リップル FIR フィルタの係数は書き換えられます。

AD7768-1 はキャリブレーション・レジスタを内蔵しており、このレジスタによって、センサーから入力信号コンディショニングを経由して ADC に至る全入力経路に対して、オフセットとゲインの補正を実行するためのプログラミングが可能です。

キャリブレーション・レジスタに書込みを行う前と、書込みを行った後での誤差の例を表 2 に示します。

| Error | Before Calibration | After Calibration |

| Offset | −420.3μV | 2.319μV |

| Gain | 3010 ppm | 10 ppm |

入力信号コンディショニング

入力信号は、いくつかのコンディショニングを行ってから ADCに入力する必要があります。これは、ADC の入力範囲を最大限に拡大することと不要な情報を除去することが目的です。シグナル・コンディショニングは 2 つの段で行います。初段のプログラマブルなゲイン計装アンプ(PGIA)は、信号の減衰または増幅が可能で、次段のアンチエイリアシング・フィルタ(AAF)は、信号の完全性を劣化させる可能性のある折返しノイズの除去が可能です。

PGIA

LTC6373 は完全差動 PGIA で、様々な入力信号の振幅を 0.25 倍~16 倍の範囲で減衰および増幅します。LTC6373 におけるゲイン・ピンの設定値とそれに対応するゲインを表 3 に示します。

| A2 | A1 | A0 | Gain |

| Logic High | Logic High | Logic High | Shutdown |

| Logic High | Logic High | Logic Low | 0.25 |

| Logic High | Logic Low | Logic High | 0.5 |

| Logic High | Logic Low | Logic Low | 1 |

| Logic Low | Logic High | Logic High | 2 |

| Logic Low | Logic High | Logic Low | 4 |

| Logic Low | Logic Low | Logic High | 8 |

| Logic Low | Logic Low | Logic Low | 16 |

LTC6373は最大入力バイアス電流が20pAと低く、入力インピーダンスが 1000GΩ と高いため、センサー回路や H ブリッジ回路によって、このソリューションを容易に駆動できます。

LTC6373 では、出力電圧を ADC ドライバと ADC 入力に使用するのと同じ電源電圧に限定することで、ADC と ADC ドライバを過電圧から保護することができます。この機能は、LTC6373の V+OUT ピン、ADA4945-1 の+VS ピン、および AD7768-1 のAVDD1 ピンに対して同じ電源を使用することで実現できます。

LTC6373 のゲイン帯域幅積(GB積)は、ゲインを上げると増加するため、ゲイン設定範囲にわたって広い帯域幅を確保しながら位相変化を最小限に抑えることができます。この機能は、ゲイン設定値ごとに専用の周波数補償が必要なため、ディスクリートの PGIA 設計には実装が困難です。LTC6373 のゲインと周波数性能の関係を図 2 に示します。

AAF

AAF は、変調器のサンプル・レート(FS)を中心とするフィルタ特性で周波数を減衰させるように設計されています。このサンプル・レートは、高速モードで 8MHz、中速モードで 4MHz、および低速モードで 1MHz になっています。AAF はカットオフ周波数が 330kHz に設定された 4 次のローパス・フィルタ(LPF)で、125kHz の信号帯域幅にわたって平坦な応答を維持します。このカットオフ周波数に設定すると、高速モードでサンプル・レートが 8MHz の場合は、減衰が 105dB になります。変調器のサンプル・レートを下げた場合は、サンプル・レートに応じてAAF のカットオフ周波数を下げる必要があります。

ADA4945-1 は AAF の一部であるだけでなく、AD7768-1 ADC のドライバとしても機能します。ADA4945-1 は、優れた DC 性能と AC 性能を備えた完全差動アンプです。AAF の通過帯域は、1.3kΩ の帰還抵抗と、249Ω、249Ω、および 499Ω の抵抗の合計との比で設定されているため、ゲインが 1.3 倍になっています。

ノイズの影響

モードが混在したシグナル・チェーンの分析は複雑です。これは、アナログ・シグナル・チェーンで発生するノイズは必ずしも一様であるとは限らず、また、アナログ・フィルタとデジタル・フィルタによる応答全体を数値的に解く必要があるためです。高精度 ADC ドライバ・ツールを使用すると、ADC ドライバ、フィルタ、および ADC のフロント・エンドにおけるノイズの影響をシミュレートして評価することができ、設計工程を大幅に簡素化できます。

高精度 ADC ドライバ・ツールにおいて、ADC、ドライバ、RCフィルタ、および入力信号の設定値は以下のようになります。

- ADC には、MCLK = 16.38MHz、MCLK_DIV = 2 分の 1、電源モード = 高速、フィルタ・タイプ = FIR、デシメーション = 32、リファレンス電圧(VREF)= 4.096V、プリチャージ・モードはイネーブル。

- ADC ドライバには、反転構成、ゲイン = 1.3V/V、RF = 1.3kΩ、+VS = 5V、−VS = 0V。

- RC フィルタには、外付け抵抗(REXT)= 82Ω、外付けコンデンサ(CEXT)= 100pF。

- 入力信号には、差動入力タイプ、周波数= 1kHz、コモンモード出力電圧(VOCM)= 2.5V。

各部におけるノイズの影響は、ADC と ADC ドライバのデータシートの仕様から得られます。ADC 全体のノイズは、S/N 比仕様から得られ、また、ADC ドライバ全体のノイズは、電圧ノイズ密度仕様と電流ノイズ密度仕様に ADC フィルタの等価ノイズ帯域幅を掛けることで算出されます。

全体の実効値ノイズは、各ノイズ源に対して 2 乗和の平方根(RSS)を取ることで算出されます。全体の実効値ノイズを計算するには、次式を使用します。

全体の実効値ノイズ = √(ドライバ 2 + RC フィルタ2 + ADC2)

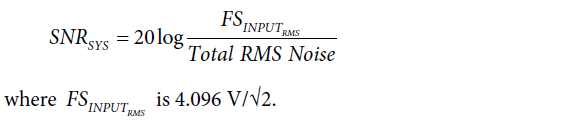

高精度 ADC ドライバ・ツールは、以下のようにシステムの S/N比(SNRSYS)を計算します。

ADC、ADC ドライバ、およびシステム全体の S/N 比について、ノイズの影響を計算した結果を表 4 に示します。

| Section | Noise (V rms) | Noise (%) | SNR (dB) |

| ADC Driver | 7.15 μ | 27 | 112.2 |

| Voltage Noise of the Amplifier (VN) | 2.45 μ | ||

| Positive Bias Current (IB+) | 866 n | ||

| Negative Bias Current (IB−) | 866 n | ||

| Feedback Resistor (RF) | 4.35 μ | ||

| Gain Resistor (RG) | 4.96 μ | ||

| RC Filter | 1.09 μ | 1 | |

| ADC | 11.7 μ | 72 | 107.9 |

| Total | 13.7 μ | Not applicable | 106.5 |

ADA4945-1 は、また、広い帯域幅と高いスルー・レートを実現できるため、サンプリング中に ADC からの電荷のキックバックを抑圧でき、次の変換サイクルの前に入力を完全に安定させることができます。61ns のサンプリング期間に入力が完全に安定する様子を図 5 に示します。

このソリューションにおけるシステム全体のゲインと、対応する入力電圧範囲を表 5 に示します。

| PGIA Gain | AAF + ADC Driver Gain | Overall System Gain | Input Voltage Range (V) |

| 0.25 | 1.3 | 0.325 | ±12.603 |

| 0.5 | 1.3 | 0.65 | ±6.302 |

| 1 | 1.3 | 1.3 | ±3.151 |

| 2 | 1.3 | 2.6 | ±1.575 |

| 4 | 1.3 | 5.2 | ±0.788 |

| 8 | 1.3 | 10.4 | ±0.394 |

| 16 | 1.3 | 20.8 | ±0.197 |

AC 性能の測定結果

CN-0535 において、1kHz の入力信号を加えたときの S/N 比の測定結果を図 6 と図 7 に示します。これらの測定結果は、表 4の高精度 ADC ドライバ・ツールによる全体の S/N 比の計算結果に近いものとなっています。ただし、測定結果は、高精度 ADC ドライバ・ツールの計算結果とは、わずかに異なっています。これは、CN-0535 ボードでの測定結果には、PGIA、電圧リファレンス、電源部品などが搭載された、システム全体の性能が含まれているためです。

CN-0535 の信号/ノイズ + 歪み(SINAD)の測定結果を図 8 と図 9 に示します。

CN-0535の全高調波歪み(THD)の測定結果を図10と図11に示します。

DC 性能の測定結果

DAQ システムでは、直線性が入力信号を ADC 出力の等価なコードに正確に変換するための重要な要素となります。オフセット誤差やゲイン誤差などの直線性誤差は、ADC のキャリブレーション・レジスタまたはマイクロコントローラのルックアップ・テーブルを使用することにより、測定システムで容易に補正できます。周辺温度に対し、オフセット電圧と DC 入力電圧がどのように変化するかを図 12 と図 13 に示します。以前にADC キャリブレーションのセクションで言及したように、これらの測定値はシステムのオフセット誤差とゲイン誤差を補正するために使用できます。

ボックス法を使用すると、システムのオフセット・ドリフトは1.8μV/ºC になり、ゲイン・ドリフトは 7μV/ºC になります。オフセット・ドリフトとゲイン・ドリフトの式は、以下のようになります。

オフセット・ドリフト =(VOSMAX − VOSMIN)/(TMAX − TMIN)

ゲイン・ドリフト =(VGAINMAX − VGAINMIN)/(TMAX − TMIN)

積分非直線性(INL)などの非直線性誤差に対して、同様な補正はできません。なぜなら、これらの誤差を予測するのが難しいためです。システムに必要なキャリブレーションを減らす最善の策は、非直線性誤差が最小のシステムを設計することです。

シグナル・チェーンにおける代表的な INL誤差(±5LSB 以内)を図 14 に示します。

電圧リファレンスおよびバッファ

ADR444 と AD8628 は、ADC 用のリファレンス電圧を生成します。ADR444は超低ノイズの 4.096V電圧リファレンス、AD8628はゼロ・ドリフト・アンプで、いずれも ADC のアナログ部と同じ単電源を使用して動作できます。この構成にすると、リファレンス・チップとリファレンス・バッファの両方に十分なヘッドルームを確保しながら、少ない電源レールでリファレンスを生成できるため、パワー・ツリーの設計を簡素化できます。

ADC へのリファレンス入力電流は、変調器のクロック・レートに比例します。リファレンス入力には、バッファなしで 80μA/Vで流れ込み、プリチャージ・バッファがイネーブルされている場合に 4μA/V で流れ込みます。リファレンス・ブロックは、これら両方の条件で駆動できなければなりません。したがって、リファレンス電圧が4.096Vの場合、ADCに流れ込むリファレンス電流は以下のようになります。

- プリチャージ・バッファがオフの場合は、流入電流(IDRAWN)= 4.096V × 80μA/V = 328.68μA

- プリチャージ・バッファがオンの場合は、IDRAWN = 4.096V × 4μA/V = 16.384μA

これらの概算値を考慮すると、AD8628 には 10mA の駆動能力があるため、リファレンス入力ピンを容易に駆動できます。

パワー・アーキテクチャ

図 15 に示すように、CN-0535 全体のパワー・アーキテクチャは、シグナル・チェーン全体が 3.3V 単電源から供給できるように設計されています。

3.3Vは、ホスト・ボードから FMC コネクタを介して供給されます。CN-0535 の起動中にコンデンサの突入電流のために必要な250mA は、フィールド・プログラマブル・ゲート・アレイ(FPGA)メザニン・カード(FMC)のホスト・プラットフォームから必ず供給できるようにしてください。この供給ができない場合は、外部電源を使用して CN-0535 に供給できます。

LT3095 は、3.3V 電源からシステム用に+15V レールと+5V レールを生成します。LT3095 は小型の電源ソリューションで、1 チップに独立した DC/DC 昇圧レギュレータを 2 個と、各出力にリニア電圧レギュレータを各 1 個搭載しています。

ADP2300 レギュレータと ADP7182 レギュレータの組み合わせによって、負電源を生成します。ADP2300 が降圧/昇圧レギュレータとして設定されて−16V 出力を生成し、後段に接続されたADP7182 リニア電圧レギュレータが−15V を生成します。

ADC のデジタル電源用の 3.3V は、3.3V 電源に直接接続されています。なぜなら、このレールはノイズの影響を受けないためです。

一方、シグナル・チェーンにおけるアナログ電源ピンについては、電源ノイズがシステムの性能に大きな影響を及ぼす可能性があるため、ノイズに関して細心の注意を払う必要があります。低ドロップアウト(LDO)レギュレータで構成される電源を除去すると、昇圧レギュレータや降圧/昇圧レギュレータで生じたスイッチング・ノイズを、システム侵入前に抑圧できます。

シグナル・チェーンの各電源で必要な消費電力を図 16 に示します。

バリエーション回路

チャンネル数の多いシステムでは、AD7768-1 の代わりに、マルチチャンネルの AD7768 および AD7768-4 の使用が適しています。これらのデバイスでは、ADCのノイズと直線性は、AD7768-1と同等ですが、1 チップで最大 8 チャンネルを同時に使用できるという利点があるため、マルチチャンネル DAQ設計を簡素化できます。

DAQ のシグナル・チェーン用に検討可能な ADC として、この他にも AD4000、AD4002、AD7380 などがあります。

ADAQ7768-1 は、24 ビット、シングル・チャンネルの高精度µModule® DAQ システムで、ADC、ADC ドライバ段、およびPGIA 段だけでなく、最も重要なパッシブ・コンポーネントもシステム・イン・パッケージ(SiP)デザインに統合されています。このオプションは、実装のサイズや簡素化が重要となる場合に推奨されます。

回路の評価とテスト

以下のセクションでは、CN-0535 の回路設計におけるテスト手順と結果の収集について概説します。ハードウェアとソフトウェアのセットアップの詳細については、CN-0535 ユーザ・ガイドを参照してください。

必要な装置

以下の装置類が必要になります。

- EVAL-CN0535-FMCZ リファレンス設計ボード

- EVAL-SDP-CH1Z(SDP-H1)システム・デモンストレーション・プラットフォーム・ボード

- オーディオ・プレシジョン AP2700 または同等の装置

- Bayonet Neill–Concelman(BNC)端子および Subminiature Version B(SMB)端子付きの同軸ケーブル

テストの開始にあたって

ハードウェア構成を図 17 に示します。

リファレンス設計ボードを使用する際には、以下の手順に従ってください。

- EVAL-SDP-CH1Z が PC から取り外されていることを確認します。AD7768-1 評価用ボード・ソフトウェアをインストールし、ソフトウェアのインストールが完了した後に PC を再起動します。

- EVAL-SDP-CH1Z を EVAL-CN0535-FMCZ リファレンス設計ボードに接続します。EVAL-SDP-CH1Z のコネクタ J4 をEVAL-CN0535-FMCZ 上の受けソケット P1 に接続します。

- EVAL-SDP-CH1Z と EVAL-CN0535-FMCZ を互いにねじ止めし、2 枚のボードが互いにしっかりと接続されていることを確認します。

- 12V の DC 電源を EVAL-SDP-CH1Z に接続し、次に付属のUSB ケーブルを使用して EVAL-SDP-CH1Z を PC 接続します。オペレーティング・システムによって指示された場合は、EVAL-SDP-CH1Z 用のドライバを自動的に検索するように選択します。

- プログラム・メニュー内のアナログ・デバイセズ・サブフォルダから AD7768-1 評価用ボード・ソフトウェアを起動します。

- サイン波発生器または任意波形発生器を以下のようにパワーオンします。

- 差動 AC 源を EVAL-CN0535-FMCZ の入力(J3 およびJ4)に接続します。

- 信号タイプをサイン波に設定し、1kHz でのレベルを5.9V p-p に設定します。

- 出力をイネーブルします。

- ソフトウェアを実行し、算出された ADC データおよびFFT データを取得します。

図 18と図 19の 2 つのプロットは、前述の手順に従って設定を行った場合に、EVAL-CN0535-FMCZから予想される代表的な取得データを示しています。図 18 は ADC 取得データの時間領域表示で、多数のサンプルにわたって予想される ADC 出力コードを図示したものです。

図 19 は、同じデータを周波数領域の FFT プロットとして処理し表示したものです。AD7768-1 ソフトウェアのユーザ・インターフェースは、32,768 サンプルを取得するように設定されており、窓関数として 7 項ブラックマン・ハリスが使用されています。