概要

設計リソース

評価用ボード

型番に"Z"が付いているものは、RoHS対応製品です。 本回路の評価には以下の評価用ボードが必要です。

- ADL5380-EVALZ ($141.51) ADL5380 Eval Board

- EVAL-AD7903SDZ ($134.00) AD7903 Eval Board

- EVAL-SDP-CB1Z ($134.00) Eval Control Board

機能と利点

- 6GHzまでの高精度な振幅および位相測定

- 小型PCBフットプリント

マーケット & テクノロジー

使用されている製品

参考資料

-

CN0374: RF-to-Bitsソリューションが6GHzまで高精度の位相および振幅データを提供2017/03/10PDF369 K

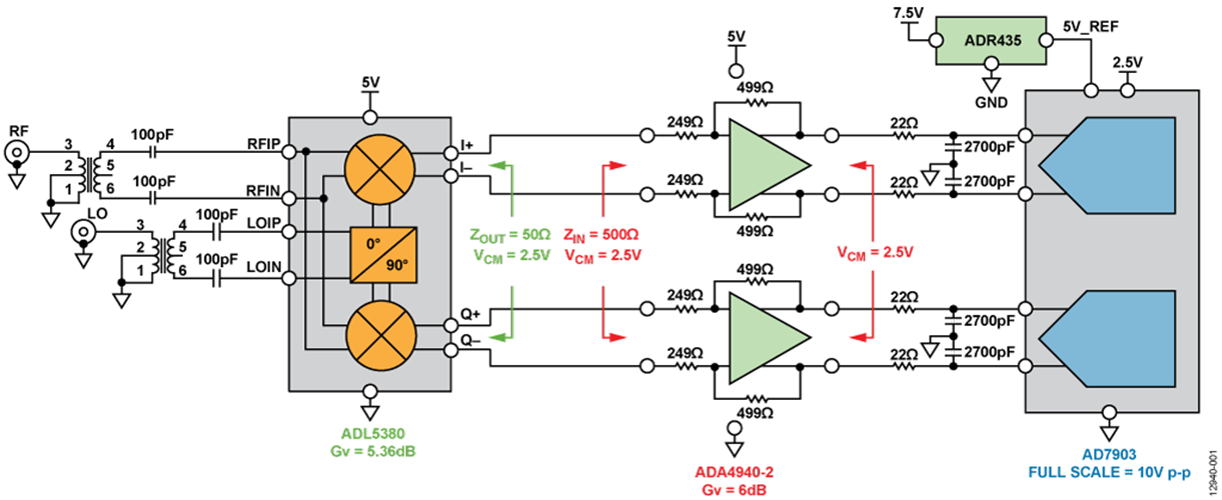

回路機能とその特長

図1に示す回路は、400MHz~6GHzのRF入力信号を、それらの信号に対応するデジタルの振幅および位相に高精度で変換します。シグナル・チェーンは、900MHzにおける0°~360°の位相測定を1°の精度で行います。回路には、高性能直交復調器、デュアル差動アンプ、およびデュアルの16ビット1MSPS差動逐次比較型A/Dコンバータ(SAR ADC)が使われています。

回路説明

直交復調器

直交復調器は、位相差がちょうど90°の同相(I)信号と直交(Q)信号を生成します。I信号とQ信号はベクトル量なので、受信信号の振幅と位相シフトは、図2に示すように三角関数の恒等式を使用して計算できます。局部発振器(LO)の入力がオリジナルの送信信号で、RF入力が受信信号です。復調器は合計および差分の項を生成します。RF信号もLO信号も周波数はまったく同じ(ωLO = ωRF)なので、高周波の合計項は除去されますが、DCに差分項が存在します。受信信号の位相(φRF)と送信信号の位相(φLO)は異なり、この位相シフトはφLO − φRFとして表すことができます。

実際のI/Q復調器には、直交位相誤差、ゲインのアンバランス、LOからRFへのリークなど多くの不完全性があり、これらはすべて、復調信号の品質を低下させる原因となり得ます。復調器を選ぶ際には、まず、RF入力周波数範囲、振幅精度、および位相精度に関する条件を決定します。5V単電源を使用するADL5380復調器は、400MHz~6GHzのRFまたはIF入力周波数を受け入れることができるので、レシーバのシグナル・チェーン用に最適です。5.36dBの電圧変換ゲインが得られるように構成されたADL5380のI出力とQ出力は、500Ω負荷で2.5Vp-p差動信号をドライブすることができます。900MHzで、10.9dBのノイズ指数(NF)、11.6dBmの1次インターセプト・ポイント(IP1)、29.7dBmの3次インターセプト・ポイント(IP3)という性能が優れたダイナミックレンジを提供し、その0.07dBという振幅バランスと0.2°の位相バランスが高い復調精度を実現します。先進的なSiGeバイポーラ・プロセスを使用して製造されるADL5380は、4mm×4mmの小型24ピンLFCSPパッケージで提供されます。

ADCドライバと高分解能高精度ADC

ADA4940-2 完全差動デュアル・アンプは、その優れたダイナミック性能と調整可能な出力同相電圧によって、高分解能デュアルSAR ADCのドライブに最適なデバイスとなっています。5V単電源を使用するADA4940-2は、2.5Vの同相電圧で±5Vの差動出力を生成します。ゲイン2(6dB)を実現できるように構成されたこのデバイスは、ADC入力をフルスケールまでドライブします。RCフィルタ(22Ω/2.7nF)がノイズを制限し、ADC入力の容量性D/Aコンバータ(DAC)から生じるキックバックを軽減します。独自のSiGe相補型バイポーラ・プロセスを使用して製造されるADA4940-2は、4mm×4mmの小型24ピンLFCSPパッケージで提供されます。

AD7903デュアル16ビット1MSPS SAR ADCは優れた精度を備えており、ゲイン誤差は±0.006% FS、オフセット誤差は±0.015mVです。2.5V単電源で動作するAD7903の1MSPSにおける消費電力は、わずか12mWです。高分解能のADCを使用する主な目的は、特に入力信号のDC振幅が小さい場合などに、±1°の位相精度を実現することにあります。ADCに必要な5Vリファレンスは、ADR435低ノイズ・リファレンスによって生成されます。

回路の評価とテスト

図3に示すように、レシーバ・サブシステムは、ADL5380-EVALZ、ADA4940-2ACP-EBZ、EVAL-AD7903SDZ、およびEVAL-SDP-CB1Z評価キットを使用して実装できます。これらの回路コンポーネントはサブシステム内での相互接続用に最適化されており、2つの高周波フェーズロック入力ソースがRFおよびLOの入力信号を生成します。

レシーバ・サブシステムの各コンポーネントの入力および出力電圧レベルの概要を表1に示します。復調器のRF入力における11.6dBmの信号は、ADCフルスケール・レンジの-1dB以内の入力を生成します。表1は、ADL5380の負荷が500Ω、変換ゲインが5.3573dB、電源ゲインが−4.643 dB、ADA4940-2のゲインが6dBであることを前提としています。このレシーバ・サブシステムの校正ルーチンと性能から得られる結果について、以下の項で説明します。

| RF Input | ADL5380 Output | AD7903 Input | |

| +11.6 dBm | +6.957 dBm | 4.455 V p-p | -1.022 dBFS |

| 0 dBm | -4.643 dBm | 1.172 V p-p | -12.622 dBFS |

| -20 dBm | -24.643 dBm | 0.117 V p-p | -32.622 dBFS |

| -40 dBm | -44.643 dBm | 0.012 V p-p |

-52.622 dBFS |

| -68 dBm | -72.643 dBm | 466 µV p-p | -80.622 dBFS |

レシーバ・サブシステムの誤差校正

レシーバ・サブシステムには、オフセット、ゲイン、位相という3つの主要な誤差源が含まれています。

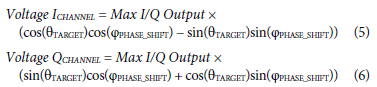

IおよびQチャンネルのそれぞれの差動DC値は、RFおよびLO信号の相対位相に関して正弦関数の関係にあります。結果として、IおよびQチャンネルの理想DC値は、以下の式で計算できます。

位相が極座標グリッド上を移動していくと、理論的にはいくつかの位置で同じ電圧が生じます。たとえば、I(余弦)チャンネルの電圧は+90°または-90°の位相シフトで同じになるはずです。しかし、位相シフト誤差がRFおよびLOの相対位相に関係なく一定だとすると、サブシステム・チャンネルは、同じDC値となるはずの入力位相に対して異なる結果を生成します。これを図4と図5に示します。これらの図では、入力が0Vとなるべき時に2つの異なる出力コードが生成されています。この場合の-37°の位相シフトは、フェーズロックループを含む実際のシステムにおける予想よりはるかに大きい値です。結果は+90°が実際には+53°、-90°が-127°として現れています。

| Input Phase RF to LO | Average I Channel Output Code | Average Q Channel Output Code | I Channel Voltage | Q Channel Voltage | Measured Phase | Measured Receiver Subsystem Phase Shift |

| -180° | -5851.294 | +4524.038 | -0.893 V | +0.690 V | +142.29° | -37.71° |

| -90° | -4471.731 | -5842.293 | -0.682 V | -0.891 V | -127.43° | -37.43° |

| 0° | +5909.982 | -4396.769 | +0.902 V | -0.671 V | -36.65° | -36.65° |

| +90° | +4470.072 | +5858.444 | +0.682 V | +0.894 V | +52.66° | -37.34° |

| +180° | -5924.423 | +4429.286 | -0.904 V | +0.676 V | +143.22° | -36.78° |

結果は10°ステップで-180°から+180°まで収集したもので、その未補正データは図4と図5に示す楕円形状を描きます。この誤差は、システム内に存在する追加位相シフトの大きさを求めることによって表せます。表2は、システムの位相シフト誤差が、伝達関数全体を通じて一定であることを示しています。

システム位相誤差の校正

図3に示すシステムで、10°ステップでの平均測定位相シフト誤差は-37.32°でした。この追加位相シフトが分かれば、調整されたサブシステムのDC電圧を計算できます。変数φPHASE_SHIFTは、平均測定追加システム位相シフトとして定義されます。位相補正されたシグナル・チェーンで生成されるDC電圧は、次式で計算できます。

式5と式6は、所定の位相設定に対するターゲット入力電圧を与えます。これでサブシステムが直線化されたので、オフセット誤差とゲイン誤差を補正できます。直線化されたIおよびQチャンネルの結果は、図4と図5にも示されています。データセットに対して線形回帰を行うと、図に示す最適直線が得られます。この直線が、各変換シグナル・チェーンについて測定されたサブシステムの伝達関数です。

システム・オフセットとゲイン誤差の校正

レシーバ・サブシステム内の各シグナル・チェーンのオフセットは理論的には0LSBですが、IチャンネルとQチャンネルの測定オフセットは、それぞれ−12.546LSBと+22.599LSBでした。最適直線の勾配は、サブシステムの勾配を表わしています。理想的なサブシステムの勾配は次式で計算できます。

図4と図5の結果は、IチャンネルとQチャンネルの測定スロープがそれぞれ6315.5と6273.1だったことを示しています。これらのスロープは、システムのゲイン誤差を補正するために調整する必要があります。ゲイン誤差とオフセット誤差を補正すれば、式1を使って計算した信号振幅が理想信号振幅に一致します。オフセット補正値は測定オフセット誤差の反数です。

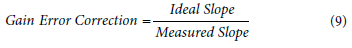

ゲイン誤差補正係数は次式で表されます。

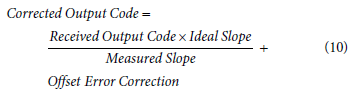

受け取った変換結果は次式で補正できます。

サブシステムの校正DC入力電圧は、次式で計算できます。

IチャンネルとQチャンネルの両方に式11を使用して、各サブシステム・シグナル・チェーンの測定アナログ入力電圧を計算します。これら完全調整済みのIおよびQチャンネルの電圧は、個々のDC信号値によって定義されるRF信号振幅を計算するために使われます。完全校正ルーチンの精度を評価するには、収集した結果を、位相シフト誤差が無いものとして、復調器の出力に生成される理想サブシステム電圧に変換します。各トライアルにおける測定位相の正弦波部分から計算した位相シフト誤差を除去して、先に計算した平均DC値に乗じてください。計算は次のようになります。

ここで、

φPHASE_SHIFTは先に計算した位相誤差です。平均校正後振幅は、オフセット誤差とゲイン誤差について補正した式1から得たDC値です。

0dBm RF入力振幅時のさまざまなターゲット位相入力における校正ルーチンの結果を表3に示します。式12と式13において行われる計算が、この回路ノートに示す方法で位相と振幅を検出しようとするあらゆるシステムに組み込まれる補正係数です。

| Target Phase | I Channel Fully Corrected Input Voltage | Q Channel Fully Corrected Input Voltage | Fully Corrected Phase Result | Absolute Measured Phase Error |

| -180° | -1.172 V | +0.00789 V | -180.386° | 0.386° |

| -90° | -0.00218 V | -1.172 V | -90.107° | 0.107° |

| 0° | +1.172 V | +0.0138 V | +0.677° | 0.676° |

| +90° | +0.000409 V | +1.171 V | +89.98° | 0.020° |

| +180° | -1.172 V | -0.0111 V | +180.542° | 0.541° |

図6は、測定された絶対位相誤差のヒストグラムで、-180°から+180°まで10°ステップでの測定誤差は1°未満です。

あらゆる入力レベルで正確な位相測定を行うには、LOを基準とするRFの測定位相シフト誤差(φPHASE_SHIFT)が一定でなければなりません。測定位相シフト誤差がターゲット位相ステップ(θTARGET)または振幅の関数として変化し始めると、この項に示す校正ルーチンの精度も低下し始めます。室温における評価結果は、900MHzでのRF振幅範囲が最大11.6dBmから約-20dBmまでの範囲で、位相シフト誤差が比較的一定であることを示しています。

レシーバ・サブシステムのダイナミック・レンジと、これに対応する振幅起因の追加位相誤差を図7に示します。入力振幅が-20dBmを超えて減少すると、位相誤差校正精度が低下し始めます。システム・ユーザーは、最小許容信号振幅を決定するために、シグナル・チェーン誤差の許容レベルを決定しなければなりません。

図7に示す結果は、5V ADCリファレンスを使用して収集したものです。ADCリファレンスの振幅はシステムの量子化レベルを小さくすれば減らすことができ、これによって小信号の位相誤差精度が段階的に改善されますが、システムが飽和する可能性が大きくなります。システムのダイナミック・レンジを増加させるもうひとつの方法は、ADCのノイズフリー・ビット分解能を向上させるオーバーサンプリング方式を採用することです。平均するサンプル数を2倍にするごとに、システム分解能は1/2LSBずつ向上します。所定の分解能の増加に対するオーバーサンプリング比は次式で計算できます。

ここで、Nはビット増加数です。

ノイズ振幅がサンプル間のADC出力コードをランダムに変更するのに十分でなくなると、オーバーサンプリングは限界点に達します。この点に達すると、システムの有効分解能を上げることができなくなります。システムは大きさがゆっくりと変化する信号を測定するので、オーバーサンプリングによる帯域幅減少が大きな問題となることはありません。

AD7903評価用ソフトウェアは、ADCの出力結果の3つの誤差源(位相、ゲイン、オフセット)をユーザーが補正できる校正ルーチンを備えています。この回路ノートで計算した校正係数を求めるには、そのシステムにおける未補正結果を収集する必要があります。校正係数部分をマークしたGUIの Amp/Phase Panel タブを図8に示します。係数が決まれば、このタブを使用して復調器からの位相および振幅結果を示すこともできます。極座標グラフは、測定されたRF入力信号を視覚的に示しています。振幅と位相の計算は、式1と式2を使って行われます。オーバーサンプリング比は、Num Samples ドロップダウン・ボックスを使い、キャプチャごとのサンプリング数を調整することによって制御できます。

必要な装置

回路の評価には以下の装置を使用します。

- USBポート付きのWindows® XP、Windows Vista(32ビット)、またはWindows® 7(32ビット)搭載PC

- ADL5380-EVALZ、ADA4940-2ACP-EBZ、EVAL-AD7903SDZ、およびEVAL-SDP-CB1Z評価ボード

- 2台の位相制御機能付きRF信号発生器(R&S SMT06など)

- デジタル・マルチメータ

- 5Vおよび9V電源

- AD7903評価用ソフトウェア(得られる振幅情報と位相情報のデジタル処理に使用)

テスト・セットアップのブロック図を図9に示します。