概要

設計リソース

設計/統合ファイル

- Schematic

- Bill of Materials

- Gerber Files

- Allegro Layout Files

- Assembly Drawing

評価用ボード

型番に"Z"が付いているものは、RoHS対応製品です。 本回路の評価には以下の評価用ボードが必要です。

- EVAL-CN0314-EB1Z ($87.99) Configurable 4-20 mA Loop Powered Transmitter/Receiver using a Micropower Instrumentation Amplifier

機能と利点

- 4-20mA トランスミッタ / レシーバ

- ループ駆動

- 設定可能

製品カテゴリ

マーケット & テクノロジー

使用されている製品

参考資料

-

MT-066: In-Amp Bridge Circuit Error Budget Analysis2015/02/14PDF35 kB

-

MT-035: Op Amp Inputs, Outputs, Single-Supply, and Rail-to-Rail Issues2015/02/14PDF115 kB

-

MT-031: データ・コンバータのグラウンディングと、「AGND」および「DGND」に関する疑問の解消2009/03/20PDF144 kB

-

CN0314: マイクロパワー計装アンプを使用した設定可能な 4-20 mA ループ駆動トランスミッタ/レシーバ2014/03/20PDF522K

回路機能とその特長

図 1に示す回路は業界をリードするマイクロパワー計装アンプを使用した4 mA to 20 mAループ駆動トランスミッタです。無調整合計誤差は1%以下です。この回路は差動入力電圧を電流出力に変換するトランスミッタ(図 1)として、あるいは4 mA to 20 mA 電流入力を電圧出力に変換するレシーバ(図 5)としてスイッチ1個で設定する事ができます。

回路設計は高精度、低ノイズ、低消費電力のプロセス・コントロール・アプリケーションに最適化されています。回路のトランスミッタとしての入力範囲は0 V ~ 5V 又は0 V ~ 10 Vです。回路のレシーバとしての出力範囲は2.5 V 又は5 Vリファレンスを使うADCと互換性のある0.2 V ~ 2.3 V 又は0.2 V ~ 4.8 Vです。トランスミッタとしての電源電圧の範囲は12 V ~ 36 Vで、レシーバとしては7 V ~ 36 Vです。

回路構成は設定可能なので、1つのハードウェア設計を同時にトランスミッタとレシーバそれぞれのバックアップとし使用でき、在庫要求を最小限に抑える事ができます。

回路説明

回路は間接的電流フィードバック・アーキテクチャを採用した計装アンプ AD8420 を特徴としています。AD8420 はこのアーキテクチャにより、優れた入力/出力特性になっています。従来の計装アンプとは異なり、AD8420 は両電源がなくてもグラウンドあるいはグラウンドより少し低い信号も簡単に増幅する事ができます。AD8420の出力はレールtoレールで、出力電圧振幅は入力同相電圧に対して完全に独立しております。従ってAD8420は大部分の従来型計装アンプのアーキテクチャに伴う入力同相電圧と出力電圧間の相互作用によって生ずる制限から開放されます。AD8420の入力出力特性は柔軟性あり、マイクロパワーレベルの消費電力(0 V入力時80 μA max)で、広い電源範囲になっているので低消費電力の工業用アプリケーションに理想的です。

トランスミッタ回路

図 1は、4mA to 20mAトランスミッタ回路の簡略化した図です。回路は約1 mAしか電流を消費しないのでループ駆動のアプリケーションに適しています。トランスミッタの入力範囲には0 V ~ 5 V と0 V ~ 10 Vがあり、ジャンパ P3を使用して選択できます。しかしAD8420の差動入力電圧は最大1 Vに制限されるので、入力電圧範囲は0.195 V ~ 0.990 V の範囲にスケールダウンされます。

検出抵抗R9を通して流れる電流には回路の電流とQ1電流が含まれますが、AD8420の電流(IAMP)は含まれません。

AD8420の独特なアーキテクチャは電源電流の予測を可能にし、+IN と−INの間に印加される電圧が0.195 V ~ 0.990 Vの場合100 μA ~ 200 μAです。この電源電流がR9を通して流れる電流に加算され、合計出力ループ電流4 mA to 20 mAとなります。従って、ループの合計電流は次の式で与えられます:

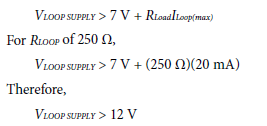

回路が適切に動作するためには、回路全体の電源電圧を7 V以上にし、電圧リファレンス ADR02 が十分なヘッドルームを得られるようにする必要があります。

ループ電源電圧も36 V maxに制限されます。

AD8420の利点はその高インピーダンス・リファレンス・ピンで、それを駆動する追加のオペアンプが必要ないので、トランスミッタ回路の電力、コスト、スペースを削減できます。

適切なループ動作のためには、検出抵抗R9(50 Ω)を除き、回路ボードのグラウンドとループのグラウンドを接続しない事が重要です。

スケーリング用抵抗の選択

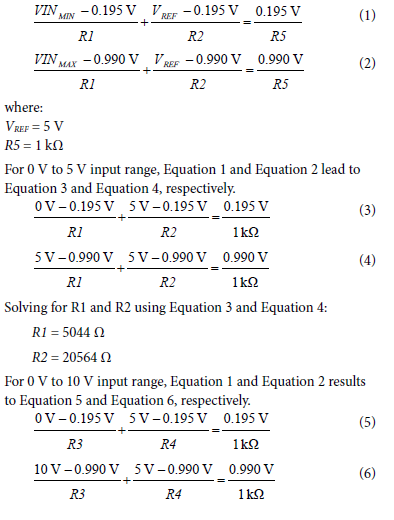

AD8420の差動入力電圧範囲は最大±1Vに制限されています。 従って、工業用機器の高い入力電圧範囲を受信できるように、回路ではスケーリング抵抗網を使用して、0 V ~ 5 V あるいは0 V ~ 10 V入力を0.195 V ~ 0.990 Vに変換します。次の式では回路の中のR1、R2、R3、R4の値を得るために節点解析を使います。

同じように、相当するスケーリング抵抗について解きます:

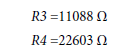

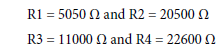

実際の回路では、EIA標準0.1%抵抗値の最も近い値を使用しなければならないので一定のオフセット誤差を招く結果になります:EVAL-CN0314-EB1Zボードとともに供給される抵抗を下に示します:

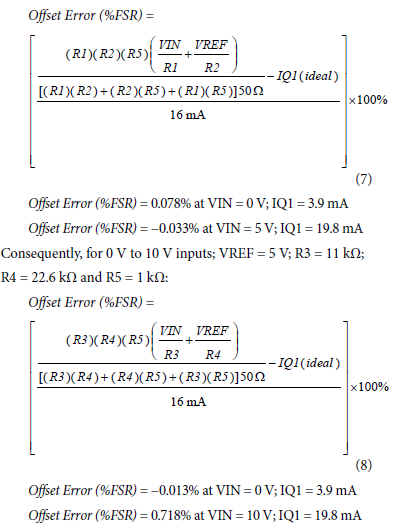

ボードとともに供給されるこれらの抵抗の値によるオフセット誤差は次の式を使って計算する事ができます:

0 V ~ 5 V入力の場合、VREF = 5 V、R1 = 5.05 kΩ、R2 = 20.5 kΩ、R5 = 1 kΩ。

このオフセット誤差を最小限にするために、計算された抵抗値により近くなるように2個の0.1%抵抗値を組み合わせて使用する事もできます。

トランスミッタ回路全体の精度

抵抗の許容誤差の影響で生じる合計誤差の良い近似は影響を及ぼす抵抗が合計誤差に均等に影響すると仮定する事です。4個の影響を及ぼす抵抗はR1又はR3、R2又はR3そしてR5とR9です。許容誤差0.1%抵抗の積み重ねによるワーストケースは0.4% maxの合計抵抗誤差なります。二乗和平方根誤差を想定すると、合計二乗和平方根誤差は0.1√4 = 0.2%になります。

AD8420のAグレードとADR02のBグレードを使用したシステムの能動部品による最大誤差と二乗和平方根誤差を下の表に示します。

| Error Component | Error | Error Value | Error %FSR |

| AD8420-A | Offset | 250 µV | 0.03% |

| ADR02-B | Offset | 0.06% | 0.015% |

| RSS FS Error | 0.034% | ||

| Max FS Error | 0.045% |

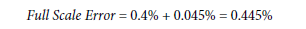

能動部品のオフセットによるワーストケース誤差に0.4%のワーストケース抵抗許容誤差を加えると次の値になります:

これらの誤差は理想的な抵抗が選択され、誤差はそれらの許容誤差の結果生じたものと想定します。

ループ電源= 25 Vでの回路の実際の誤差データを図 3と図 4に示します。合計出力誤差(%FSR)は実測出力電流と理想出力電流の差をとり、FSR(16 mA)で除算し、結果に100を乗算する事により計算されます。

レシーバ回路

図4に簡略化したレシーバ回路を示します。レシーバ回路は電流信号を2.5 V又は5 Vリファレンスで動作する多くのシングル・エンド入力ADCと互換性のある電圧レベルに変換します。

抵抗R6を使用して4 mA to 20 mA信号を検出し、アンプへの入力電圧0.2 V ~ 1 Vに変換します。アンプのFBピンとREFピンの間の電圧は入力電圧に等しくなります。出力範囲が1 V ~ 5 Vのほとんどのダイレクト・ゲインのレシーバとは異なり、この回路ではADR02とともにゲイン抵抗とスケーリング抵抗を使用して0.2 V ~ 4.8 Vを出力します。これは5Vリファレンスを使用したADCの入力ダイナミック・レンジを最大限にします。ヘッドルームを追加する事により入力信号範囲全体にわたり直線性が確実に得られます。レシーバ回路は、2.5 Vリファレンスを使用するADCのために0.2 V ~ 2.3 Vが出力するようにジャンパP4を使って設定する事もできます。

このアプリケーションに対するAD8420の主な利点は入力範囲を超える事無しに、あるいは多くの他の単電源計装アンプとは異なり、コモン・モードの制限に陥る事なしにグラウンド近くの電流を検出する事ができることです。さらに、AD8420にはゲインとレベルシフトの機能があるので、簡単な抵抗分割を使った場合のようにADCの入力範囲を無駄にする事はありません。

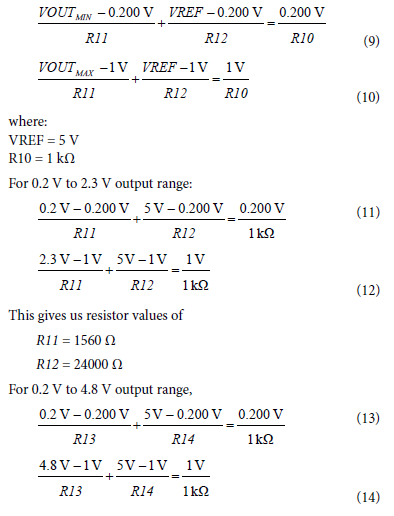

ゲイン用抵抗とスケーリング用抵抗の選択

AD8420のゲインは通常2個の抵抗(R11 とR10)の比で設定されます。しかし、ダイレクト・ゲインでは低電圧側で無駄になる余分の20%の範囲を利用するために回路ではADR02を使用します。下の式は必要な出力電圧範囲に設定するためのゲイン用抵抗とスケーリング用抵抗の値を求める方法を示します。

従って

回路ボード上で供給される抵抗はサプライヤから入手可能で市販されているEIA標準0.1%抵抗の最も近い値です。そこで、ボード上に供給される抵抗の実際の値は次の通りです:

ボードとともに供給されるこれらの抵抗の値によるオフセット誤差は次の式を使って計算する事ができます:

このオフセット誤差を最小限にするために、計算された抵抗値により近くなるように2個の0.1%抵抗値を組み合わせて使用する事もできます。

レシーバ回路全体の精度

抵抗の許容誤差の影響で生じる合計誤差の良い近似は影響を及ぼす抵抗が合計誤差に均等に影響すると仮定する事です。4個の影響を及ぼす抵抗はR11又はR13、R12又はR14そしてR6とR10です。許容誤差0.1%抵抗の積み重ねによるワーストケースは0.4% maxの合計抵抗誤差になります。二乗和平方根誤差を想定すると、合計二乗和平方根誤差は0.1√4 = 0.2%になります。

AD8420のAグレードとADR02のBグレードを使用したシステムの能動部品による最大誤差と二乗和平方根誤差を下の表に示します。

| Error Component | Error | Error Value | Error % FSR |

| ADR02-B | Offset | 0.06% | 0.01% |

| AD8420-A | Offset | 250 µV | 0.01% |

| AD8420-A |

Gain | 0.05% | 0.05% |

| RSS FS Offset | 0.014% | ||

| RSS FS Gain | 0.05% | ||

| RSS FS Error | 0.064% | ||

| Max FS Offset | 0.02% | ||

| Max FS Gain | 0.05% | ||

| Max FS Error | 0.07% |

能動部品によるワーストケース誤差に0.4%のワーストケース抵抗許容誤差を加えると次の値になります:

フルスケール誤差 = 0.4% + 0.07% = 0.47%

これらの誤差は理想的な抵抗が選択され、誤差はそれらの許容誤差の結果生じたものと想定します。

VCC = 25 Vでのレシーバ回路の実際の誤差データを図 5と図 6に示します。合計出力誤差(%FSR)は実測出力電流と理想出力電流の差をとり、出力電圧のFSRで除算し、結果に100を乗算する事により計算されます。

回路図、部品表、レイアウト・ファイルを含むトランスミッタ/レシーバ・ボードEVAL-CN0314-EB1Z の設計支援パッケージは https://www.analog.com/CN0314-DesignSupport に載っております。

回路の評価とテスト

評価に必要な装置

- EVAL-CN0314-EB1Z 評価ボード

- デュアルDC電源Agilent E3631又は同等品

- 高精度DC電源Yokogawa 2000 又は同等品

- 高精度マルチメータアジデント 3458 又は同等品

テスト・セットアップの構成とテスト

回路は図 7 と 図 8に示したテスト・セットアップを使用してテストしました。Agilent 3631Aを25 Vに設定してボードの電源として供給しました。評価ボードの実際の電流出力あるいは電圧出力はAgilent3458のマルチメータを使用して測定しました。EVAL-CN0314-EB1Z の写真を図 9に示します。

トランスミッタ回路のテスト・セットアップ(図 8)のために、高精度DC源(Yokogawa 2000)を使用して0 V ~ 5 V あるいは0 V ~ 10 Vの差動入力を生成しました。回路をトランスミッタとして設定するためにスイッチS1を “V-I”の位置にする必要があります。

レシーバ回路のテストセットアップ(図 9)のために、2番目のEVAL-CN0314-EB1Zを使用して入力電流4 mA to 20 mAを生成しました。必要であれば高精度電流源を使用する事もできます。回路をレシーバとして設定するためにスイッチS1を“I-V”の位置にする必要があります。

スイッチとジャンパの4 mA to 20 mAトランスミッタ向け設定

図 1に示すトランスミッタ回路の場合、スイッチS1を“V-I”の位置にする必要があります。入力範囲0 V ~ 10 Vの場合はジャンパP3を“0–10V”の位置に、そして入力範囲0 V ~ 5 Vの場合は“0-5V”の位置にする必要があります。図 9の評価ボードの写真もご覧ください。

スイッチとジャンパの4 mA to 20 mAレシーバ向け設定

図 4に示すレシーバ回路の場合、スイッチS1を“I-V”の位置にする必要があります。出力範囲0.2 V ~ 2.3 Vの場合はジャンパP4を“0.2-2.3V”の位置に、そして出力範囲0.2 V ~ 4.8 Vの場合は“0.2-4.8V”の位置にする必要があります。図 9の評価ボードの写真もご覧ください。