レーダー用RFフロント・エンド・システム

アナログ・デバイセズは、レーダー・アプリケーションおよびフェーズド・アレイ・アンテナ向けの完全なRFフロント・エンド・ソリューションを提供します。アナログ・デバイセズのGaNおよびGaAs技術に基づくパワー・アンプ、ロー・ノイズ・アンプ(主にGaAs技術)、そしてGaAs、シリコンSOI、GaN技術を用いたスイッチ技術からなる幅広いポートフォリオは、レーダー・アプリケーションにおける送信/受信機能を構成します。これらすべての機能を単一パッケージに集積したフロント・エンドも提供しています。

価値と利点

- 完全なRFフロントエンド:GaN、GaAs、SOI技術がレーダーおよびフェーズド・アレイ向け送受信機能を提供します。

- 高性能チェーン:PA、LNA、スイッチが低ノイズと電力効率を確保します。

- 集積度の高いビームフォーミング:シングル・パッケージの送受信モジュールが設計と制御を簡素化します。

- 作業負荷の軽減:効率化された導入により実装が加速されます。

Apollo MxFE:16Tx / 16Rx Xバンド・レーダー・プラットフォーム

単一基板上の4つのApollo MxFE™デジタイザICが、マルチチップ同期とマルチチャンネル・キャリブレーション手法をどのように改善するかをご覧ください。

ADTR1107

ADTR1107は、パワー・アンプ、ロー・ノイズ・アンプ(LNA)、および反射単極双投(SPDT)スイッチを内蔵した、コンパクトな6GHz~18GHzフロント・エンドICです。

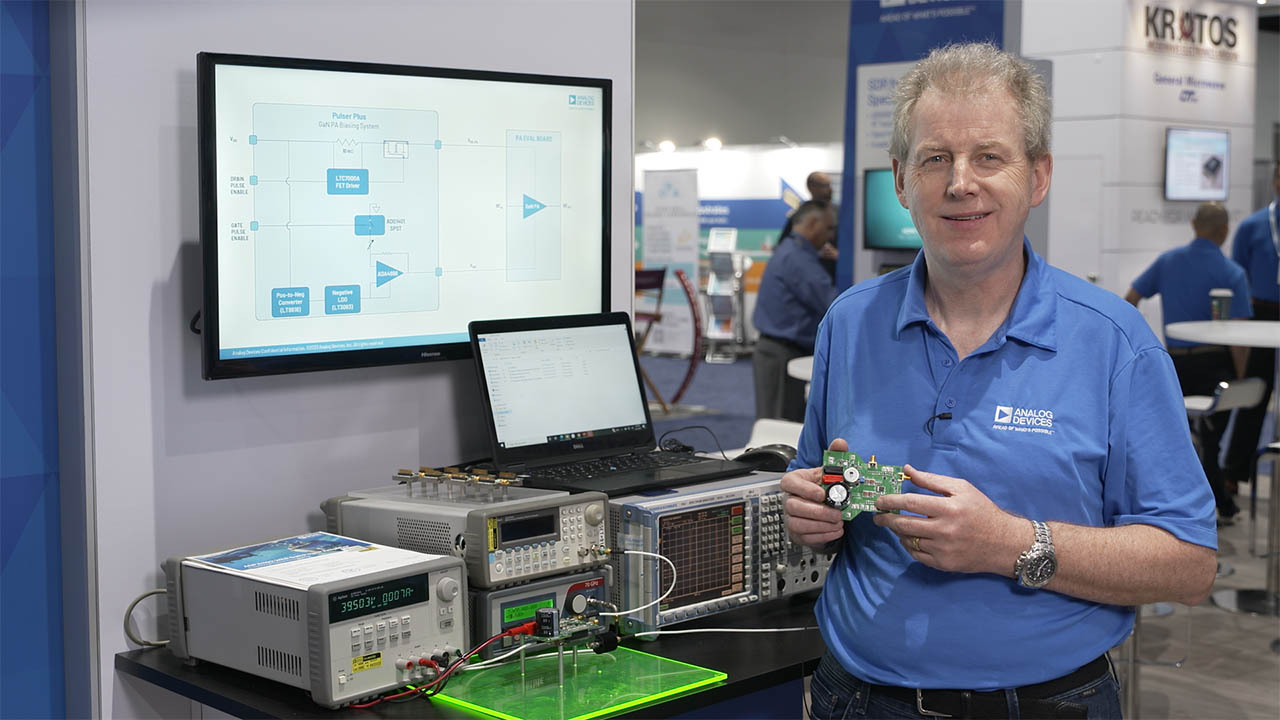

フェーズド・アレイ・レーダーの給電

アナログ・デバイセズのGaN PAで実現した高出力、高効率AESA。ADPA1122 20W GaNパワー・アンプをご覧ください。

評価用ボード

EVAL-ADTR1107

ADTR1107(6GHz~18GHz、フロントエンドIC)の性能評価

EVAL-ADPA1106

46dBm(40W)、2.7GHz〜3.5GHzのGaNパワーアンプADPA1106の評価

EVAL-AD9081

AD9081評価用ボード

X-Band Phased Array Platform

スケーラブルな32素子のハイブリッド・ビームフォーミング・フェーズド・アレイ・レーダー開発プラットフォーム

{{modalTitle}}

{{modalDescription}}

{{dropdownTitle}}

- {{defaultSelectedText}} {{#each projectNames}}

- {{name}} {{/each}} {{#if newProjectText}}

-

{{newProjectText}}

{{/if}}

{{newProjectTitle}}

{{projectNameErrorText}}