Digital PFC Control: Adding Value to Motor Control System Monitoring

Digital PFC Control: Adding Value to Motor Control System Monitoring

Jun 1 2015

Power factor correction (PFC) is increasingly important for industrial motor drives in the main due to increased regulation of harmonic content on the utility side with additional side benefits related to efficiency, voltage quality, and conductor rating. Digital PFC controllers are more costly and can be more complex than their analog counterparts. However, they can provide significant value and add to the context of the overall system design when considered in tandem with the functionality of the main motor control processor. This article highlights the system level benefits provided by a digital PFC controller in the context of overall system monitoring, protection, and sequencing for engineers. The implementation of this in a real motor control system platform is shown with figures and/or graphs in terms of hardware and software frameworks, with experimental validation.

Power factor correction (PFC) is becoming increasingly important for industrial motor drives. This is in the main due to increased regulation on harmonic content on the utility side. However, there are also good reasons to implement PFC from the perspectives of overall system efficiency improvement, conductor rating, and improved distribution voltage quality, which may be important for other loads within the industrial environment, such as direct online induction motors and transformers. PFC can be implemented by means of an active circuit topology, such as a single-phase [1] or 3-phase boost rectifier [2] or through a passive approach, which involves the judicious use of low frequency inductors and capacitors to shape the ac line current envelope. Both forms of PFC attempt to reproduce a sinusoidal or approximately sinusoidal line current, in phase with the line voltage—thus, minimizing loss producing harmonic currents and reactive power flow from the utility. The trade-offs between active and passive PFC are related to cost, passive component weight, volume, and PFC related losses.

In single-phase motor drives, active PFC is generally fairly accepted. For 3-phase systems, passive harmonic corrections are currently more popular, and typically involve large 50 Hz to 60 Hz inductors in the 3-phase lines, or a single inductor on the dc side of the rectifier. However, there are advantages in moving to active PFC at higher powers. Active PFC solutions (dc or ac side) offer the best solutions in terms of inductor size, lower power loss, less weight, and best power factor.

In single-phase applications, such as low power motor drives, the rectifier input boost converter, shown in Figure 1, is the default.

Figure 1. Single-phase boost PFC circuit.

These typically switch at frequencies in the 50 kHz to 100 kHz range, and consequently require a much smaller dc side inductor than a passive solution. For 3-phase systems, single switch topologies involving either ac side or dc side high frequency inductors are possible.

One of the obstacles to implementation of PFC control is the additional cost associated with the PFC circuit and the PFC controller. This is particularly the case in a system where the processor is on the safety extra low voltage (SELV) side of the isolation barrier. In this instance, implementation of the PFC control from within the main motor control processor can carry additional complexity and cost due to the need to isolate the ac side measurement and control signals from the processor I/O and ADCs. Moreover, implementation of 50 kHz to 100 kHz PWM control from a processor typically optimized to service motor control applications with PWM frequencies of 10 kHz to 20 kHz can be a difficult match.

An option in this case is to use a cheap analog PFC controller, such as the UC3854 [3], and have it operate completely independently from the main system controller. Added value can be achieved, however, by using a digital PFC controller, such as the ADP1047 [4], in conjunction with the motor control processor and a digital isolator. The processor can then offload some of the sequencing, monitoring, and protection functionality to the PFC controller and enhance the total system capability at a reduced cost. This arrangement can be useful for the following:

- Start-up and shutdown sequencing

- System-level status information

- User interface display information

- Monitoring of unusual conditions

- Minimizing sensor requirements

- Backup measurements/redundancy

- Acting as part of overall system fault protection

- Controller optimization (via efficiency)

The potential system monitoring, protection, and sequencing coverage of a typical digital PFC controller part is shown in Figure 2. The advantage from a system design perspective of utilizing the integrated functionality of a part, such as the ADP1047, under the control and supervision of the main processor is evident. Overall system cost, complexity, and sensor count can be reduced, even though the PFC controller itself may be more costly than its analog counterparts.

Figure 2. Digital PFC controller coverage in a motor control system.

Hardware Platform

Analog Devices provides an experimental platform to validate its signal chain components and software tools in a real motor control system. The circuit architecture for this platform is shown in Figure 3, with the platform hardware itself shown in Figure 4.

Figure 3. Universal ac input motor control platform.

Figure 4. Motor control platform hardware.

This system represents a fully functional PMSM mains input motor drive with power factor correction, full control, communication signal isolation, and optical encoder feedback. At the core of the system is the ARM®Cortex®-M4 mixed-signal control processor from ADI, the ADSP-CM408. The PFC front-end control is performed by the ADP1047, with accurate input power metering capability and inrush current control. The ADP1047 is designed for single-phase PFC applications; the ADP1048 is designed especially for interleaved and bridgeless PFC applications. The digital PFC function is based on a conventional boost PFC with multiplication of the output voltage feedback combined with the input current and voltage to provide optimum harmonic correction and power factor for ac/dc systems. All signals are converted into the digital domain to provide maximum flexibility; all key parameters can be reported and adjusted via the PMBus™ interface. The ADP1047/ADP1048 allows users to optimize system performance, maximize efficiency across the load range, and reduce design time to market. The combination of a flexible, digitally controlled PFC engine and accurate input power metering facilitates the adoption of intelligent power management systems that are capable of making decisions to improve end user system efficiency. The device supports additional efficiency improvements through programmable frequency reduction at light load and the capability to reduce the output voltage at light load. The ADP1047/ADP1048 provides enhanced integrated features and functions; the inrush current and soft start control functions provide significant component count reduction with easy design optimization. The devices are designed for high reliability, redundant power supply applications, and have extensive and robust protection circuitry. They also have independent overvoltage protection (OVP) and overcurrent protection (OCP), ground continuity monitoring, and ac sensing. Internal overtemperature protection (OTP) is provided whereby the external temperature can be recorded via an external sensing device.

System Operation

Communication between the processor and the PFC controller is over the I2C/PMBus interface, with an I2C digital isolator providing the interface between the domains. This is shown in Figure 5. The processor is located in the SELV electrical domain, with the PFC controller being referenced to the dc bus common rail in the high voltage domain. Gate driver switching signals for the 3-phase inverter are routed from the processor PWM block via a 2-channel isolator. The data and clock signals for the I2C interface and the general-purpose digital signals are also routed through digital isolators.

Figure 5. Isolation of digital signals.

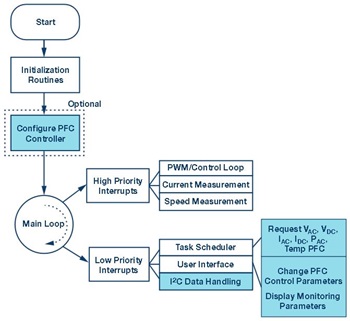

The PFC controller manages the control and monitoring of the boost PFC circuit. These tasks are offloaded from the main motor control software workflow into low priority routines as shown in Figure 6. The PFC controller parameters are configured during startup. This step can typically be skipped by writing the configuration parameters to EEPROM memory on the controller IC, if such a feature is available. As shown in Figure 6, in a typical motor control system, the speed and current measurements along with the PWM controller updates will be handled within high priority interrupts, in which the current measurement is synchronized with the PWM signal. The PFC controller can be set up to handle the input side measurements, such as input ac line voltage and current, dc bus voltage, input power, and PFC circuit temperature. These measurements are not critical to the motor control algorithm, with the possible exception of the dc bus voltage measurement in a sensorless algorithm. They are, however, important to the overall system-level monitoring and controller optimization. Thus, they can be requested and handled within a low priority I2C data handling task or interrupt routine, and at a scheduling rate matched to the system monitoring time constant.

Figure 6. Main motor control program structure.

A Micrium Probe™ user interface for the platform is shown in Figure 7, in which the dc bus reference voltage has been set to 250 V. The monitoring of the ac and dc side variables in conjunction with the motor control is clearly seen.

Figure 7. User interface.

Conclusion

The consequent savings in additional sensors, digital I/O, and analog pins on the processor, as well as the software overhead in scaling and interpretation of the measured variables, can potentially mean a reduction in processor cost by being able to choose a lower performance variant, or freeing up processor hardware and software footprint for other, higher priority or system enhancing functions.

In this example, start-up sequencing of the system with respect to the ac line voltage, protection from dc bus undervoltage, overvoltage, and ac side overcurrent, are all handled by the PFC controller. However, caution must be exercised in the overall system design in this regard, since the main control processor should always be made aware of control or protection actions being taken by the PFC controller, so that it does not take independent action as a result of a secondary effect. A good example of this is the case in which the PFC controller may exercise a global disable on the PWM signals due to a transient overvoltage on the dc bus, for instance, to a motor braking event. If the controller is not made aware of this, it will keep attempting to unsuccessfully adjust the PWM output to maintain its operating point. If the PFC controller reenables PWM once the overvoltage transient disappears, the system may progress to a secondary fault due to a sudden, large increase in PWM duty cycle. Thus, care must be taken in managing communication of protection and sequencing between the PFC controller and motor control processor.

In summary, the potential trade-offs between selection of a lower cost analog PFC controller and a more expensive digital controller, should not only be assessed on the basis of the PFC circuit itself but should also take into account the potential system-level functionality, enhancements, and cost reductions that can be leveraged by the more advanced capabilities of the digital controller. This article has attempted to highlight some of those key system-level enhancements, using the example of the ADP1047 with a single-phase motor drive system.

About the Authors

Dara O’Sullivan is a system applications director with the Industrial Edge, Motion, and Robotics business unit at Analog Devices. His area of expertise is power conversion, control, and monitoring in industrial motion cont...