概览

设计资源

设计与集成文件

• Schematic• Bill of Materials

• Assembly Drawing

• Allegro Layout Files

• Gerber Files 下载设计文件 925.21 K

评估硬件

产品型号带"Z"表示符合RoHS标准。评估此电路需要下列选中的电路板

- EVAL-CFTL-LVDT ($112.34) Measurement Specialties LVDT Sensor

- EVAL-CN0371-SDPZ ($60.92) Low Power LVDT Signal Conditioner with Synchronous Demodulation

- EVAL-SDP-CB1Z ($134.00) Eval Control Board

器件驱动器

软件(如C代码和/或FPGA代码等)用于与元件的数字接口通信。

AD719x GitHub no-OS Driver Source Code

AD7192 IIO High Precision ADC GitHub Linux Driver Source Code

优势和特点

- LVDT信号调理器

- 低功耗

- 同步探测

产品类别

领域和技术

所用产品

参考资料

-

UG-277: SDP-B Controller Board2010/12/8PDF605 kB

-

CN-0371:集成同步解调功能的低功耗 LVDT 信号调理器2015/3/23PDF1 M

电路功能与优势

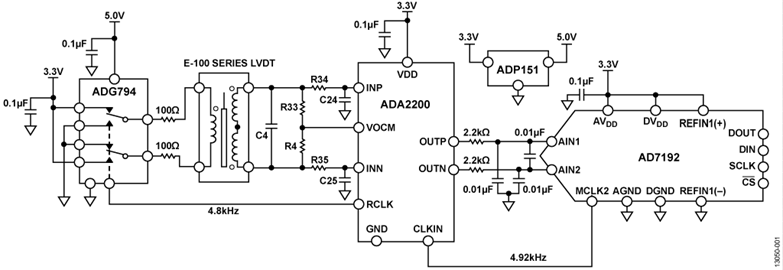

图 1 所示电路是一款完整的线性可变差分变压器 (LVDT) 信 号调理电路,可精确测量距离机械参考点的线性位置或线 性位移。模拟域中的同步解调用于提取位置信息并抑制外 部噪声。 24 位、 Σ-△ 模数转换器 (ADC) 可数字化位置输出信 息,以实现高精度。

LV D T 在活动核心和线圈组件之间采用电磁耦合。这种非 接触式 ( 因而是无摩擦的 ) 工作方式是它们广泛用于航空航 天、过程控制、机器人、核、化学工厂、液压、动力涡轮 以及其他恶劣工作环境和要求具备长工作寿命与高可靠性 应用的主要原因。

包括 LV D T 激励信号在内的整个电路功耗仅为 10 mW 。电路 激励频率和输出数据速率均为 SPI 可编程。该系统允许在可 编程带宽和动态范围之间进行权衡取舍, 支持 1 kHz 以上的 带宽,且在 20 Hz 带宽时具有 100 dB 动态范围,是精密工业 位置和计量应用的理想之选。

电路描述

ADA2200 同步解调器可在信号解调至与LVDT核心位移成比例的低频输出电压之前对LVDT次级信号进行滤波,从而提取位置信息。 ADA2200 驱动 AD7192 24位Σ-Δ ADC, 后者对输出进行数字化和滤波处理。ADA2200 生同步LVDT激励信号,而ADG794 开关将CMOS电平激励信号转换为精密3.3 V方波信号,驱动LVDT初级绕组。

LVDT是绝对位移传感器,可将线性位移转换为比例电信号。LVDT是特殊的绕线变压器,具有活动核心,其位置与待测位置贴合。激励信号施加于初级绕组。随着核心的移动,次级绕组上的电压成比例发生变化;根据该电压即可计算位置。

LVDT的类型有很多,此外提取位置信息的方法也各不相同。图1中的电路采用4线模式LVDT。将两个LVDT的次级输出相连使其电压相反,从而执行减法。当LVDT核心位于零点位置时,这两个次级端上的电压相等,两个绕组上的电压差为零。随着核心从零点位置开始移动,次级绕组上的电压差也随之增加。LVDT输出电压相位根据方向而改变。

该电路的主时钟由AD7192ADC产生。ADA2200接受主时钟并产生其内部所有时钟,包括用作LV D T激励信号的参考时钟。ADA2200上的时钟分频器配置为产生4.8 kHz激励信号。ADG794将激励信号转换为精密±3.3 V方波信号,该+3.3 V来自于ADC电源电压。3.3 V电源也用作ADC基准电压;因此,激励信号与ADC基准电压之间的比例关系可以改善电路的噪声性能和稳定性。系统的3.3 V电源由ADP151 低压差调节器提供;后者由5 V电源驱动。

LVDT次级绕组和ADA2200输入之间的耦合电路用来限制信号带宽,并调节RCLK和ADA2200输入之间的相对相位。该电路配置为具有最大正交(相位= 90°)响应以及最小同相(相位= 0°)响应。这使得可以仅通过测量正交输出就能确定位置,进而使ADA2200输出电压对电路中相位的变化不甚敏感。LVDT的温度变化导致有效串联电阻和电感发生改变,是相位变化的主要来源。

ADA2200输出端的抗混叠滤波器保持ADC所支持的信号带宽。AD7192内部数字滤波器的输出带宽约等于0.27乘以输出数据速率。为了将输出带宽保持在4.8 kHz最大输出数据速率,输出抗混叠滤波器的−3 dB转折频率可以设为2 kHz左右。对于要求较低输出数据速率的系统,可相应降低抗混叠滤波器的转折频率。

集成式同步解调器

ADA2200集成式同步解调器组成电路核心。它采用独特的电荷共享技术来执行模拟域内的离散时间信号处理。ADA2200具有全差分信号路径。它由高阻抗输入缓冲器后 接一个固定低通滤波器(FIR抽取滤波器)、一个可编程IIR滤波器、一个解调器和一个差分输出缓冲器组成。它的输入和输出共模电压等于1.65 V(3.3 V电源电压的½)。

ADA2200接受来自AD7192ADC的4.92 MHz时钟信号,然后产生其内部所有时钟,以及用作LVDT激励信号的4.8 kHz参考时钟。ADA2200集成可配置时钟分频器,可编程支持很多不同的激励频率。

CMOS开关

选择ADG794CMOS开关是因为它具有低导通电阻、快速开关时间、先开后合式开关动作以及低成本等特点。

ADG794将ADA2200的低压CMOS电平RCLK输出转换为低阻抗差分输出方波源,然后驱动LVDT。为使开关留有裕量以便驱动正3.3 V信号,ADG794 VDD输入采用5 V电源供电。

LVDT

图1中的电路只需略作改动即可支持各种LVDT。MeasurementSpecialties, Inc. E-100 LVDT采用四线式模式,以便演示电路的主要特点。E-100冲程范围为±2.54 mm,冲程端输出灵敏度为240 mV/V,满量程范围最大线性度误差为±0.5%,工作频率范围为100 Hz至10 kHz。完整详情请参见E-Series LVDT数据手册。

ADA2200输入耦合网络

可调谐ADA2200输入耦合网络以支持不同的LVDT。LVDT次级绕组电感和分流电容(C4)组成振荡电路。R4和R33电阻降低了振荡电路的Q值,使该电路不易受LVDT绕组电感和电阻的变化影响,但功耗有所上升。R34/C24和R35/C25组成的RC滤波器对可降低信号带宽,同时提供调节电路相对相位所需的额外自由度。ADA2200内部相位敏感检测器(PSD)的最大输出发生在0°或180°相对相移处。

对于采用4.8 kHz方波激励信号的E-100 LVDT而言,采用下列元件值可获得最大输出条件下的最优相位:

- R4 = R33 = 2.2 kΩ

- R34 = R35 = 1 kΩ

- C24 = C25 = 3300 pF

- C4 = 0.01 μF

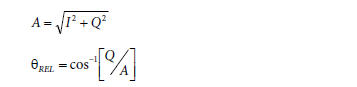

如需调谐该电路,则可通过放置LVDT核心以产生接近满量程输出信号的方式测量相位;然后,测量同相(I)和正交(Q)输出信号。采用这些测量结果便可计算相对相位:

调节网络元件,直到θREL绝对值低于约±3°;这样可以改善电路对于LVDT电气参数变化的灵敏度。

ADC选择和同步

选择AD7192Σ-型ADC,因为该器件支持可配置输出数据速率,并具有各种不同的数字滤波器输出选项,从而允许在带宽和噪声之间进行权衡取舍。主时钟输出功能可轻松实现ADC采样时钟频率与ADA2200输出信号的锁定。这对于优化数字滤波器性能而言是必须的。由LVDT信号确定位置所需的数值是一次激励时钟周期的平均值。因此,当AD7192输出数据速率设为4.8 kHz时,即设为一个激励时钟周期时,可获得所需的平均值。如果激励时钟周期和ADC采样频率未锁定,则恢复的位置测量信息中包含错误。除以输出数据速率便可有效求取多个激励时钟周期的平均值。

ADA2200输出信号哪怕在LVDT核心位置固定的情况下亦含有电能,数值为激励信号频率的倍数。还可在频率域中分析数字滤波器性能。AD7192具有sinc3或sinc4传递函数,该传递函数在输出数据速率的倍数处归零。这些频率分量是杂散误差的来源。通过将ADC的输出数据速率设为激励信号频率(或激励频率的约数)便可抑制输出杂散。如果激励时钟周期和ADC采样频率未锁定,则杂散将不会落在传递函数的零点。

如需获得包括原理图、布局布线和物料清单在内的完整电路文档,请参阅www.analog.com/CN0371-DesignSupport.

用于性能分析的用户软件

该电路支持图形用户界面,可方便地进行板上的器件配置,并评估电路性能。该软件的选项卡可执行电路校准和器件配置,以及显示噪声性能、线性度性能和实时位置测量。 有关软件包的完整描述,请参见CN-0371 软件用户指南。

噪声分析

该电路的输出噪声是ADC输出数据速率的函数。表1显示数字化数据相对于ADC采样速率的有效位数(ENOB),假设满量程输出电压为2.5 V。该电路的噪声性能与 LVDT核心位置无关。

| ADC数据速率 (SPS) | 输出带宽 (Hz) | ENOB (RMS) | ENOB (P-P) |

| 4800 | 1300 | 14.0 | 11.5 |

| 1200 | 325 | 14.9 | 12.4 |

| 300 | 80 | 15.8 | 13.3 |

| 75 | 20 | 16.2 | 13.6 |

如果ADA2200输出噪声与频率无关,则预计有效位数将在输出数据速率每4次折叠下降时增加一位。ENOB在较低输出数据速率下的增加放缓是由于输出驱动器的1/f噪声所导致的;该噪声在较低的输出数据速率下成为噪底的主要成分。

线性度测试结果

首先在±2.0 mm核心位移处执行一次两点校准即可测量线性度结果。由这两次测量结果可确定斜率和失调,从而实现预期直线拟合。然后,在±2.5 mm满量程范围内测量核心位移。从预期直线拟合数据中减去测量数据即可确定线性度误差。

测得的数据显示电路性能优于E-Series LVDT数据手册中指定的线性度性能。

多LVDT同步工作

很多应用都会近距离使用多个LVDT。若这些LVDT以相似的载波频率运行,杂散磁耦合可能导致拍频。产生的拍频可能会影响这些条件下的测量精度。为避免这种情况,所 有LVDT必须同步工作。

通过让器件同时退出复位状态,可同步多个ADA2200器件。ADA2200在RST引脚解除置位之后的第一个CLKIN上升沿时退出复位模式。因此,从单一源驱动所有ADA2200 CLKIN引脚以及所有RESETB线路便足以确保器件同步工作。避免在CLKIN上升沿附近对RESETB解除置位,以防器件在不同时钟沿上复位。可监控ADA2200器件的RCLK输出,确保ADA2200器件正确同步。

常见变化

在某些系统中,可能需要使用 SAR ADC ,而非 Σ- 型转换 器。这些情况下, ADC 转换时钟必须与 ADA2200 更新速率 同步。如前所述, ADA2200 输出会在激励频率的倍数处含 有杂散。这些杂散可通过移动平均滤波器或级联多个移动 平均滤波器加以抑制。移动平均滤波器易于实现,且具有 出色的时域特性。若要完全抑制杂散,则移动平均样本大 小必须等于 8 个样本的整数倍。

图 4 显示了 ADA2200 连接至 AD7091R-2 ,后者是一个超低功 耗、双通道、 12 位 SAR ADC 。使用一个双通道 ADC ,因而 ADA2200 的 OUTP 和 OUTN 输出可顺序采样。由于 ADA2200 输出为分立式时间样本,通过对两个顺序输出样本执行减 法操作(即VOUTP − VOUTN)便可实现差分测量。

SYNCO 信号在每个 ADA2200 输出采样周期内变为有效。 SYNCO 可用来中断微控制器,以便获取一对 ADC 样本 ( 对 OUTP 和 OUTN 采样 ) 。在上述示例中,采样周期等于激励时 钟频率乘以 8( 或 38.4 kHz) ;因此, ADC 采样速率为 76.8 kSPS 。

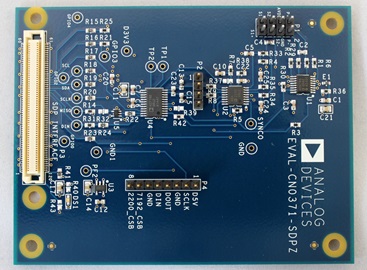

电路评估与测试

CN-0371电路使用EVAL-CN0371-SDPZ电路板和EVAL-SDP-CB1Z SDP-B控制器板。这两片板具有120引脚的对接连接器,可以快速完成设置并评估电路性能。电路板包含待评估电路,SDP-B板配合CN-0371 评估软件使用,捕捉电路板数据。

设备要求

需要以下设备:

- 带USB端口的Windows® XP(32位)、Windows Vista®或Windows 7的PC

- EVAL-CN0371-SDPZ 电路板

- EVAL-SDP-CB1Z SDP-B控制器板

- CN-0371评估软件

- Measurement Specialties, Inc. E-100经济型LVDT(EVAL-CFTL-LVDT)

开始使用

下载CN0371.zip文件,然后运行setup.exe文件。默认情况下,程序安装在Analog Devices目录下。程序名称为CN0371

功能框图

电路框图参见图5。有关完整的电路原理图请参见EVAL-CN0371-SDPZ-Schematic.pdf文件,该文件位于CN-0371设计支持包中。 用于电路板的5 V电源由USB总线通过SDP-B板的120引脚连接器提供。

设置

将EVAL-CN0371-SDPZ电路板上的120引脚连接器连接到 EVAL-SDP-CB1Z SDP-B 板上的CONA连接器。使用尼龙五金配件,通过120引脚连接器两端的孔牢牢固定这两片板。

测试

启动评估软件,并通过USB电缆将PC连接到SDP-B板上的微型USB连接器。

一旦USB通信建立,就可以使用SDP-B板来发送、接收和采集来自电路板的数据

图6显示电路板连接SDP-B板的照片。有关SDP-B板的信息请参阅 UG-277 用户指南。

有关测试设置、校准以及如何使用评估软件来捕捉数据的详细信息,请参阅 CN-0371 软件用户指南。

针对原型开发的连接

EVAL-CN0371-SDPZ电路板设计为搭配EVAL-SDP-CB1Z SDP-B 板使用,但任何微处理器都可与AD7192的SPI接口实现对接。对于另一个搭配EVAL-CN0371-SDPZ电路板使用的控制器而言,第三方必须开发相应软件。

目前已有一些转接板能实现与Altera或Xilinx现场可编程门阵列(FPGAs)的接口。利用Nios驱动器,Altera的BeMicroSDK板能配合BeMicro SDK/SDP转接板一同使用。任何集成FMC连接器的Xilinx评估板均可与FMC-SDP转接板一同使用。

EVAL-CN0371-SDPZ还兼容Digilent、Imod接口规格。

图6显示系统测试设置的照片。包括原理图、布局布线、Gerber文件和物料清单在内的完整文档可参考CN0371设计支持包,网址: www.analog.com/CN0371-DesignSupport .