次世代電子戦用レシーバーの実現を可能にする28nmプロセスのADC

はじめに

シギント(SIGINT:Signal Intelligence)とは、各種信号の傍受によって行われる諜報活動のことです。このシギントに使われる装置は、電子戦(EW:Electronic Warfare)用システム(EWシステム)と呼ばれています。そして、EWシステムで使用されるレシーバーには、帯域幅の拡大とSWaP(サイズ、重量、消費電力)の低減が絶えず求められています。そのことから、EWシステムの設計を担当する技術者は、高速A/Dコンバータ(ADC)技術の進化と改良に常に期待を寄せています。65nmプロセスで製造されるADCは、そのプロセスに関連する本質的な原因により、性能と帯域幅が限界に達しつつあります。それに対し、28nmプロセスを採用したRF対応のADCでは、その限界が打破されています。次世代の広帯域レシーバー・システムでは、この28nmのADCが新たな基盤になるはずです。28nmのプロセス・ノードでは、トランジスタの幅と寄生容量がより小さくなります。このことから、消費電力と全体的なサイズを抑えつつ、より高いサンプル・レートと広いアナログ入力帯域幅、高度なデジタル機能の統合を実現することができます。結果として、レシーバー用の新たなアーキテクチャを実現することが可能になります。

28nmのADCがもたらすメリット

現代の戦場では、広帯域に対応するEWシステムが一般的に使われるようになってきました。その一方で、システム設計者は、次世代のEW用レシーバーに求められる性能の向上とSWaPの削減をいかにして達成するかという面で、多くの課題に直面しています。高速ADCは、広帯域に対応するすべてのEW用レシーバーの設計における主要な検討項目の1つです。選択するADCによって、システムのアーキテクチャと全体的な検知/監視の能力がほぼ決定されるからです。サンプル・レート、帯域幅、分解能など、高速ADCの多くの性能は、アナログ/RFの領域からDSPに至るまでのあらゆる要件を含めて、レシーバーのその他の部分をどのように設計するかを左右する決定的な要因になります。新たな世代のEW用レシーバーの開発を進めるにつれて、ADCに対してはより広い帯域幅とより高い分解能を求める傾向が果てしなく続きます。サンプル・レートと帯域幅が向上すれば、一度にA/D変換できる帯域が広がり、RF領域の設計上の課題が緩和され、掃引時間が減少します。加えて、ビット深度の向上によって性能が高まり、誤認や誤検知を低減できます。このように、高いサンプル・レートと分解能に対する要求はとどまることがありません。高速ADCのメーカーは、デバイスの消費電力を増加させることなく、そうした要件に対応する必要があります。そのために、より微細なトランジスタ・リソグラフィック・ノード(現時点では28nmと16nm)への移行を進めているのです。

広帯域に対応する次世代のEW用レシーバーを実現し、将来のシステムを構築するための新たな基盤を形成する上では、28nmのADCがもたらす基本的なメリットが不可欠です。28nmプロセスのトランジスタは、ゲート容量が小さく、スイッチングの駆動に必要な電力が少なくて済むので、より高速なスイッチングが可能になります。加えて、28nmプロセスではトランジスタのサイズが物理的に小さくなるため、ADCではより高いサンプル・レートを達成できるだけでなく、単位面積当たりに集積可能なトランジスタの数が多くなり、より高度なデジタル機能を集積できます。本質的に消費電力が少ないことからも、28nmのADCは、65nm以上では実現が困難だった性能や能力が求められる次世代EWシステムを実現する上での鍵になります。28nmのADCで達成可能な高いサンプル・レート(数GSPS以上)は、特にシギント、電子防護(EP:Electronic Protect)、電子支援(ES:Electronic Support)を対象とするEWシステムの設計において、最も魅力的な性能の1つとなります。ADCの帯域幅と同等に重要なのが分解能です。分解能が高ければ、より高いS/N比やSFDRを達成し、ターゲットとなる信号を検知、監視、処理する能力を高めることができるからです。アナログ入力帯域幅が広くなると、第1ナイキスト・ゾーン外の信号を対象としたアンダーサンプリングも可能になります。

28nmプロセスへ移行することにより、システムのSWaPを増加させることなく(あるいは低減させつつ)、高速ADCに、信号処理などのデジタル機能をより多く集積できるようになります。例えば、そうしたADCにはNCO(数値制御発振器)やDDC(デジタル・ダウン・コンバータ)などのデジタル機能が集積されます。それにより、ADCの性能の限界が押し上げられ、デジタル・インターフェースをはじめとする高いデータ・レートに依存して消費される多くの電力に関するシステム設計上の課題が緩和されます。28nmという微細プロセスを採用し、ADCに内蔵するDSP機能をより高度なものにすれば、プロセッサの処理負荷と消費電力の大幅な軽減にもつながり、EWシステムのSWaPを更に削減することができます。

従来よりも高速な28nmのADCを使うことで、より広いRF帯域のキャプチャと監視が可能になります。ただ、恐らくは、対象となる信号の帯域幅が、ADCのナイキスト帯域幅と比べて比較的狭いことに変わりはありません。また、GSPSレベルのADCでは、データのスループットが非常に高くなります。それに対して適切なプロセッサを探し出し、ADCに物理的に接続する作業が容易ではなくなる可能性があります。現在、市場で提供されている28nmのADCは、多くの場合、1レーンのレートが10GbpsのJESD204Bをインターフェースとして採用しています。JESD204Bのレーンでは、GbpsレベルのSERDES(Serializer/Deserializer)のルーティングを行うことになります。それに伴う基板レイアウトの問題やシグナル・インテグリティの問題が生じる可能性があります。ただ、NCOやDDC、更にはDSPも内蔵するADCであれば、状況が少し異なります。その種のADCでは、対象となる信号を低い周波数(ベースバンド帯など)までダウン・コンバートし、デジタル・フィルタを適用してデシメーションを行うことによって、デジタル・データの出力レートを下げられます。それにより、キャプチャした帯域に対して、より集中的な処理を実行することができます。チューニングが可能なNCOにより、DDCはA/D変換された帯域全体を掃引できるので、帯域全体の解析が可能になります。加えて、処理利得が得られることから、デジタル・データの出力レートを抑えられます。複数のNCOとDDCを並列に配置しておけば、ユーザはDDCを瞬時に切り替えて高速にホッピングするように事前に設定することができます。NCOをチューニングする必要がなくなるため、掃引時間はより短くなります。DDCを集積することにより、JESD204Bインターフェースの消費電力も大幅に削減されます。JESD204Bに対応するためのSERDESを高いレートで動作させると、システムの消費電力が増加する可能性があります。そのため、デシメーションによってデータ・レートを低下させるのは、非常に有用な手法となります。高速ADCのサンプル・レート、ビット深度、帯域幅の更なる向上に伴い、広帯域に対応するEW用レシーバーのシステム設計者にとって、DDCが統合されたADCはますます魅力的なものになります。そのような構成でない場合、ADCからの膨大な量のデジタル・データを、SWaPの小さいプロセッサで処理することが難しくなる可能性があるからです。DDCについて、またその実用例については、「デジタル・ダウンコンバータを理解する」(著:Jonathan Harris)のPart1とPart2をご覧ください。

レシーバーの新たなアーキテクチャ

レシーバーのヘテロダイン・アーキテクチャについては、十分な研究が行われ、長い年月にわたる実運用によって、有用性が実証されています。従来は、マイクロ波に対応する多くのレシーバーが、デュアル・ダウン・コンバージョンを適用したアーキテクチャによって実装されていました。旧世代のADCでは、ADCへの入力周波数に占める動作帯域周波数の割合が大きく、シングル・ダウン・コンバージョンのアーキテクチャでは、イメージの除去が困難でした。最新のADCは、サンプル・レートとアナログ入力帯域幅の両方が拡張されており、シングル・ダウン・コンバージョンによる高性能で広帯域対応のアーキテクチャを簡単に実現できるようになっています。

図1に、シングル・ダウン・コンバージョンをベースとするレシーバーのアーキテクチャの例を示しました。フロント・エンドのLNA(低ノイズ・アンプ)は、ノイズ指数を基にして選択されます。必要に応じ、LNAの前段にリミッタを配置することで、フロント・エンドの耐電性能を高めることができます。続く動作帯域フィルタは、帯域外の干渉成分を減衰させます。その後段には、必要に応じてゲイン段およびゲイン制御段を追加します。ミキサーの前のローパス・フィルタは、ミキシングに伴うスプリアス出力に加わるRF高調波を低減します。ミキサーは重要な構成要素です。周波数変換の対象となる帯域において、最適な性能が得られるように選択しなければなりません。ミキサーの後段のローパス・フィルタは、次段で増幅を行う前に、上側波帯を除去する役割を果たします。必要に応じ、IF信号を対象とするゲイン段を更に追加します。一般に、ADCの直前には、アンチエイリアシング(折返し誤差防止)フィルタを配置します。同フィルタにより、サンプリング処理によって帯域内に折り返す可能性のあるすべての周波数成分を除去します。続くADCは、このシグナル・チェーンにおける最終段として配置されています。ただ、通常、レシーバーを設計する際に最初に選択されるコンポーネントはADCです。残りの部分はそのADCを基にして選択/構築されます。

図1. シングル・ダウン・コンバージョンをベースとするレシーバーのアーキテクチャ

次は、周波数計画を策定する(周波数プランニング)際の検討事項について説明します。周波数プランニングというのは、周波数変換の方法を選択する作業のことです。合理的なフィルタ設計によってスプリアスを最小化し、入手/採用が可能なコンポーネントを使って実装を行うことになります。実際には、最適に近いレベルの様々な周波数計画の選択肢について、様々な検討を行う必要があります。そのため、このような決断を初めて行うRF技術者にとっては、気の滅入る作業になるかもしれません。幸い、設計支援ツールとコンポーネントの両方が急速に進歩したこともあり、周波数プランニングは、以前よりもはるかに取り組みやすい作業になっています。

一般に、スプリアスの観点からは、IFの値は高く、ADCの第2ナイキスト・ゾーンまたは第3ナイキスト・ゾーンに含まれていることが望ましいと言えます。以下では、まず10GHzを中心とする動作帯域を、3GSPSに対応するADCの第1ナイキスト・ゾーンに変換する周波数計画を示します。続いて、第2ナイキスト・ゾーンで処理を行うことのメリットを示すことにします。

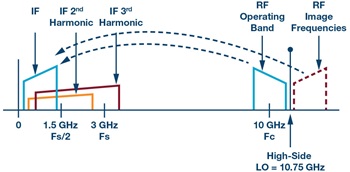

図2は、10GHzを中心とする1GHzの動作帯域を、3GSPSで動作するADCの第1ナイキスト・ゾーンへと周波数変換する様子を示したものです。この図には、2つの重要な問題が現れています。1つは、RF帯のイメージ周波数が動作帯域の近くに存在するため、イメージを抑制するためには実装が非常に困難な高性能のフィルタが必要になるということです。もう1つは、IFアンプによって生成される成分がIFの帯域内にあり、アンチエイリアシング・フィルタでは除去できないことです。

図2. 問題のある周波数計画。IFの高調波がIFの帯域内に生じているので、イメージの除去が困難です。

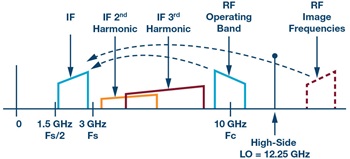

図3に示したのは、同じRF動作帯域がADCの第2ナイキスト・ゾーンに変換されるようにサンプリングした例です。IFの値が先ほどよりも高いので、イメージ周波数が動作帯域から離れた位置にあります。これであれば、イメージを除去するためのフィルタの実装がかなり容易になります。また、IFアンプで生成される高調波は、アンチエイリアシング・フィルタで除去でき、生成されるIFの高調波は、ADCによるものだけとなります。

図3. より優れた周波数計画。IFの高調波はIFの帯域外にあるので、イ メージの除去が可能です。

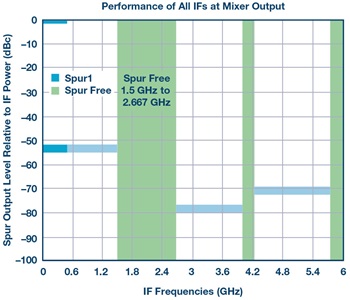

Keysight Technologiesの設計支援ツール「Genesys」によりスプリアス解析を行えば、直ちに同じ結論が導き出されます。図4は、周波数プランニング・ツール「Genesys WhatIF」によって得たものです。同ツールで、動作帯域を10GHz、瞬時帯域幅を1GHzに設定し、ハイサイドLO(局部発振器)を選択して、5次までのスプリアスを検出した結果です。緑色で示されているのがスプリアス・フリーの領域です。3GSPS対応のADCの第2ナイキスト・ゾーンに収まっていることがわかります。

図4. 周波数プランニング・ツールによるスプリアスの解析結果。Keysight TechnologiesのGenesys WhatIFを使用しました。

新たなアーキテクチャを支えるコンポーネント

周波数プランニングにおける解析を行った後は、レシーバーの動作条件の下でミキサーとADCの評価を必ず実施します。それにより、スプリアスとノイズに関する性能を検証しなければなりません。

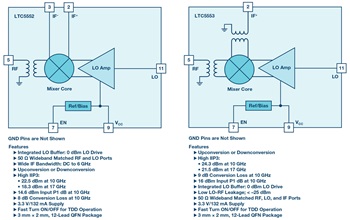

アナログ・デバイセズは、3GHz~20GHzに対応する高性能ミキサー「LTC5552」と「LTC5553」を提供しています。図5に、これらのデバイスの主な特徴を示しました。いずれも、広帯域に対応しつつ、高い直線性を備える最高クラスの広帯域ミキサーであり、広帯域対応のレシーバーのアーキテクチャにそのまま適用できます。LTC5552は差動IF出力を備えていますが、LTC5553はすべてのポートがシングルエンドです。この点が両者の最大の違いです。LTC5552の差動IF出力を使えば、IFのシグナル・チェーン全体を差動で構成できます。そのため、ADCの入力部にバランを適用する必要がなくなります。IFセクションを完全に差動構成にすることにより、差動IFアンプを簡単に実装できます。完全差動のIFセクションは、そのシグナル・チェーンに差動フィルタを追加するだけで実現できます。

図5. 直線性をはじめとする性能が高い広帯域対応のミキサー

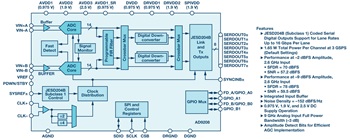

一方のADCについて、アナログ・デバイセズは28nmプロセス品である「AD9208」を発表しています。分解能が14ビット、サンプル・レートが3GSPSのデュアルADCであり、先述した多くの機能や優れた特性を備えています。広い入力帯域幅と高い分解能、そして4個のDDCとNCOをはじめとする内蔵デジタル機能を備えていることから、EW用レシーバーなどのシステム/アプリケーションに最適です。また、9GHzという広いアナログ入力帯域幅に対応しているので、第2ナイキスト・ゾーン、第3ナイキスト・ゾーンでの直接サンプリングが可能です。クリーンで低ジッタのリファレンス・クロックによって、高い入力周波数に対するS/N比の低下を最小限に抑えれば、第4ナイキスト・ゾーンでのサンプリングも可能です。

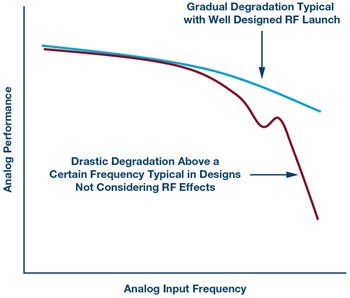

RFレシーバーの設計者を悩ませ続けている課題があります。それは、ADCのあらゆる重要な性能指標は、入力周波数が高くなるに従い低下するという問題です。これは、ノイズについても、スプリアスフリー・ダイナミック・レンジ(SFDR)についても当てはまります。ADCの性能は、チップの設計に大きく依存することは言うまでもありません。それに加えて、GSPSレベルのADCにおいて入力帯域幅を維持するためには、チップからパッケージのラミネートへのRF放射と、パッケージからプリント回路基板へのRF放射を考慮して、慎重にパッケージを設計する必要もあります。

適切に設計されたRF対応のI/O構造では、入力周波数が高くなるに従い、性能が緩やかに低下します。このことを考慮せずに設計すると、ある入力周波数で性能が著しく低下するという状況に陥ります。図7は、この概念を示したものです。アプリケーションで使用するADCを選択する際には、設計を確定する前に、十分に時間をかけて性能を検証する必要があります。ギガヘルツ以上の周波数でサンプリングを行うRF対応のADCの場合、その作業がより重要な意味を持ちます。ADCを選択する前に、周波数に対する性能の変化について、十分に把握しておく必要があります。

まとめ

本稿では、広帯域に対応するアプリケーションで使用するレシーバーを設計する際に検討すべき事柄について説明しました。EWシステムでは、できるだけ広い動作帯域と瞬時帯域幅が求められます。そのため、レシーバーに対する要件が特に厳しくなります。この問題に対し、シングル・ダウン・コンバージョンを適用するレシーバーのアーキテクチャでは、ADCの高次ナイキスト・ゾーンで処理を行うことで、スプリアス性能を高めることができます。その場合、ADCの入力帯域幅と、ミキシング段の性能が重要な意味を持ちます。幸い、現在では、そうした設計上のポイントを重視して設計されたコンポーネントが登場してきています。アナログ・デバイセズは、入力周波数範囲が拡張された28nmプロセスのADCと、高い直線性を備える広帯域対応のミキサーを用意しています。いずれも高速の製品であり、次世代のレシーバーの基盤になり得るものです。

図6. 3GSPSに対応するAD9208。28nmプロセス品であり、性能が高く、入力帯域幅が広いことを特徴とします。

図7. アナログ性能と入力周波数の関係。S/N比、SFDR、信号パワーといったアナログ性能は、いずれも入力周波数が高くなるに従い劣化します。高いIFサンプリングを採用する場合には、選択したADCの性能が、必要な入力周波数に対して大きく低下しないことを検証しなければなりません。また、プリント回路基板の設計においては、RF対応であることを念頭に置いた慎重なレイアウトが求められます。