データ・コンバータのアレイに供給するサンプリング・クロックの同期をとる

概要

通信分野のインフラや計測機器など、多くのアプリケーションでは、システムの帯域幅を広げつつ、分解能を高めることが求められています。その結果、複数のデータ・コンバータ(A/Dコンバータ、D/Aコンバータ)をアレイ状に接続して使用するケースが増えてきました。その種のシステムでは、データ・コンバータ用のインターフェースとしてシリアル方式のJESD204Bがよく使用されます。そして、データ・コンバータの大規模なアレイにクロックを供給するにあたっては、それらすべての同期をとることが重要になります。つまり、そのための低ノイズで高精度のソリューションを見いだすことが設計上の課題になります。

上記の問題に対処するためのものとして、最近では、ジッタの減衰機能、VCO(電圧制御発振器)、多数の出力、多数の同期管理機能を備えるクロック生成デバイスが市場に出回るようになりました。しかし、現実の多くのアプリケーションでは、データ・コンバータのアレイ向けに多数のクロックを用意する必要があります。結果として、単一のICによって対応可能な範囲を超えることになります。そのため、実際の設計では大規模なクロック・ツリーが使用されます。多くの場合、その種のツリーは、複数のクロック生成デバイスとクロック分配デバイスを組み合わせることによって構成されます。

本稿では、柔軟性が高く再プログラムが可能なクロック・ツリーの構築方法を実例に基づいて説明します。拡張が可能なその回路は、優れた位相ノイズ性能とジッタ性能を発揮します。そして、クロック・ツリーの大元のデバイスから末端のデバイスまで、同期に必要な情報をデタミニスティックな制御によって伝達します。

はじめに

ワイヤレス通信システムは、3G/LTE、4G、5Gへと発展を遂げてきました。その流れによって、高速データ変換技術と同期技術の進化も後押しされました。様々な要因が絡み合い、セルラ・システムの基地局に必要なデータ帯域幅は広がり続けています。主な要因としては、契約者数の増加、より豊富なマルチメディア・コンテンツに対する需要、グローバルなセルラ・インフラを使用した新たなマシン間通信アプリケーションの登場といったことが挙げられます。このような状況に対応するために、アクティブ・アンテナ、大規模MIMO(Multi Input, Multi Output)、高度なビームフォーミングといった新たな技術が使われるようになりました。結果として、より多くのチャンネルを備える革新的なRFトランシーバーのアーキテクチャに注目が集まるようになりました。多数の入出力を備えるシステムでは、複数の伝送パスを利用します。そのため、複数のA/Dコンバータ(ADC)とD/Aコンバータ(DAC)を使用することが必須になります。データ変換の規模という観点から要件を考えると、サンプリング・クロックの生成と同期の確立は設計上の大きな課題です。システムによっては、必要なクロック信号の数はわずか数本程度で収まることもあるでしょう。しかし、必要なクロック数は数百本のレベルに簡単に増加する可能性があります(図1)。

図 1. データ・コンバータのアレイに適用されるクロック・ツリー

JESD204Bでは、データ転送用のシリアル・インターフェースの仕様が定められています。その主要な目的は、広帯域に対応するデータ・コンバータと他のシステムICをつなぐ入出力データの信号線の数を削減することです。そうすれば、高速/高分解能のデータ・コンバータを使用する際に生じる問題を緩和できます。信号線の数を減らせれば、プリント基板のレイアウトを簡素化できます。言い換えれば、システム全体の性能に影響を及ぼすことなく、より小さなフォーム・ファクタを実現することが可能になります。こうした改善は、多くのアプリケーションにおいてサイズとコストの制約に対処する上で有用です。例えば、ワイヤレス・システムのインフラ、可搬型の計測機器、防衛分野のシステム、医療用の超音波機器などにおいて大きな意味を持ちます。

システム・レベルで考慮すべき事柄

大規模なデータ・コンバータのアレイを備える複雑なシステムにおいて、処理することが可能なデータ量を増加させるためには何に注意する必要があるのでしょうか。重要なのは、アンテナから処理ユニットまで、一貫して高いS/N比を維持することです。クロックの供給という観点から言えば、S/N比はサンプリング・クロックの位相ノイズによって制限されます。位相ノイズの性能が低ければ、ジッタが発生します。そうするとS/N比が大幅に低下し、EVM(Error Vector Magnitude)が増加してシステムの性能が低下します。一般に、クロック信号の質はジッタで規定されます。ジッタは、対象とする帯域幅にわたって位相ノイズを積分したものとして定義されます。通常、位相ノイズの積分区間は数十kHzから数十MHz程度です。一方で、クロック信号のノイズ・フロアが高い場合にも、システムのS/N比に影響が及びます。そのため、広帯域ノイズも配慮すべき重要な要素です。サンプリング・クロックの質が不十分である場合、スプリアス成分が生じる可能性があります。そうすると、スプリアスフリー・ダイナミック・レンジ(SFDR)が低下します。更に、サンプリング・クロックの質は周波数領域だけで規定すればよいわけではありません。デューティ・サイクルや立上がり時間/立下がり時間などのパラメータを考慮する場合には、時間領域での規定も必要になります。

上述したのは、システムで使用するサンプリング・クロックに求められる基本的な要件です。しかし、大規模なデータ・コンバータのアレイを使用し、各クロックの間で同期を確立する必要がある場合には、もう1つの重要な要件が加わります。それはチャンネル間のスキューです。データ・コンバータのアレイを使用するシステムの性能は、アレイ間でデータの同期がとれているか否かに依存します。つまり、システムの性能は各データ・コンバータ間のスキューに対して敏感であるということです。

この種のシステムでは、もう1つ考慮すべきことがあります。それは消費電力です。消費電力が多いと、システムの効率を高く維持することが難しくなります。そうするとシステムの温度が上昇するので、冷却コストが増加します。加えて故障率が高くなる可能性もあります。更に、商業的な観点から言えば、部品点数と基板面積を低減することも重要な課題になります。

クロック・ツリーの構造

先述したように、大規模なシステムでは、単一のクロックICの出力によってすべてのブランチを駆動するのは難しいケースが多くなります。クロック・ツリーのトポロジを採用して適切な設計を行えば、この問題を克服し、複数の部品、デバイス、あるいは複数のシステムの同期を確立することが可能になります。図2に示したのがクロック・ツリーの例です。

図 2. クロック・ツリーのブロック図

図に示したように、クロック・ツリーでは各レベル(各段)で遅延が発生します。それらの遅延は、固定的な遅延と不確定な遅延から成ります。また、遅延は、電圧や温度の変化、デバイスに固有のプロセスばらつきといった要因からの影響を受ける可能性があります。データ・コンバータに高い周波数で同時にクロックを供給する必要がある場合、誤差の積み重ねによって、許容できないレベルのタイミング変動が生じてしまうかもしれません。今日のシステムでは動作周波数が使用されます。その周波数(クロック)については、セットアップ時間とホールド時間として厳しい要件が定められています。固定の遅延は手間をかければ補償できます。しかし、不確定な遅延はシステム内で補償することはできません。そのため、設計者にとっては、不確定な遅延に関連する要素を何らかの方法で制御することにより、その遅延の値を最小限に抑えるか排除することが目標になります。

現実のアプリケーションでは、上記のような制約に対応しつつ、システムの要件に応じてブランチの数を増加させ、それらを簡単に制御できるようにしなければなりません。したがって、ツリーの構造は柔軟性を備えている必要があります。

クロックをアラインし、チャンネルのスキューを最小限に抑える上では、それをデタミニスティックに行えるようにすることが目標になります。つまり、すべてのデバイスとすべてのパワーアップ・シーケンスに対して、再現性良く繰り返しアライメントを実施できるようにするということです。JESD204Bを採用したシステムでは、デタミニスティックな遅延を実現するためにローカル・マルチフレーム・クロック(LMFC:Local Multiframe Clock)のアラインメントを行う必要があります。このインターフェースにおいては、サブクラス1(SYSREF)またはサブクラス2(SYNC)の定義を使用して、送信デバイス/受信デバイスでLMFCのリセットとアラインメントを実施しなければなりません。しかし、システム全体に不確定な遅延が存在する場合には、LMFCの1周期内に同クロックのアラインメントを実現することが困難になります。そのため、先ほど説明したような高精度のアラインメントが実現されたクロック・ツリー構造の採用が推奨されます。そうすれば、LMFCのアラインメントを実現するのが容易になります。

また、各データ・コンバータに入力されるデバイス・クロックについては、SYSREF信号のセットアップ時間とホールド時間が確実に許容範囲内に入るようにする必要があります。単一のクロックICを使用した設計であれば、セットアップ時間とホールド時間を満たすのは、適切なタイミング・マージンを確保するための簡単なプロセスとなるでしょう。それに対し、単純なクロック・バッファをベースとし、複数のデバイスを使用するクロック・ツリー構造では、セットアップ時間とホールド時間を制御するのは容易ではありません。先ほど提案したクロック・ツリー構造であれば、様々なレイヤにわたってデタミニスティックな同期が実現されます。そのため、すべてのレイヤ間のすべてのSYSREF/デバイス・クロックのペアについて、セットアップ/ホールドのタイミングの要件を満たすことが可能です。このクロック・ツリー構造であれば、同期に関する制約を満たしつつ、異なるレイヤ間のすべてのデータ・コンバータにおいて高速なデバイス・クロックの位相をアライメントすることができます。

クロック・ツリーの設計

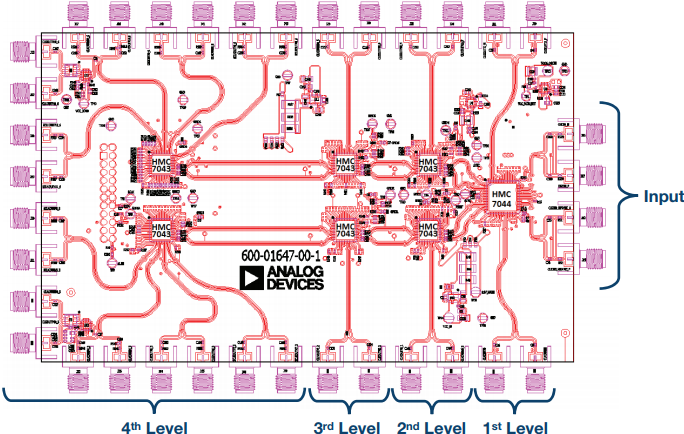

図 3 に示したのは 4レベルのクロック・ツリーの例です。この回路は、 1つのメインのクロック生成部( HMC7044 ) と 3レベルのファンアウト・バッファ( HMC7043 )によって構成されています。それにより、データ・コンバータを実装したボード向けに、同期のとれた複数のクロックを生成することができます。

図 3. 4 レベルのクロック・ツリーの例

1 つだけ使用している HMC7044 は、クロック・ツリーのルートとしての役割を果たします。同 IC は14出力のクロック・ジェネレータであり、 JESD204B の同期の要件に対応するジッタ減衰機能を備えています。一方、 HMC7043 は14出力のファンアウト・バッファであり、ブランチの各レベルで使用しています。これらはコンパチブルな製品であり、プログラミング機能も非常によく似ています。そのため、デバイスのマッチングやクロック分配のレベルの増減を非常に容易に実現できます。つまり、システムの柔軟性を高められるということです。

クロック・ツリーの各レベルについては、各出力の間の同期をとることができます。このシステムにおいて、 HMC7044 の出力の位相は SPI ( Serial Peripheral Interface )ベースのコマンドによってアライメントすることが可能です。 SYNCパルスを使用すれば、より正確に位相のアライメントを実現できます。 SPIベースのコマンドを使用すると、 HMC7044 の SYSREFタイマーがリセットされます。この共通のタイマーを使用することにより、各クロックに対応するすべての出力分周器を制御することができます。すなわち、すべての分周器は、 SYSREFタイマーからのコマンドによって同時にアラインメントされます。 SYNCコマンドからSYSREF タイマーまでの遅延ならびにターンオン時間とターンオフ時間の間の遅延は明確に規定されています。そのため、デタミニスティックな遅延に基づいて出力間の同期を実現することが可能です。また、いずれの出力も、定義された数のパルスを生成するようにプログラムし、システム内で SYSREFパルスとして使用することもできます。

クロック分配部である HMC7043 も、上記のものと非常によく似た SYSREF タイマー構造を採用しています。同 ICは RFSYNC信号を利用してアライメントを実現します。 RFSYNC のパルスにより、 HMC7044 の SYNC信号ベースのプロセスと同様の処理が開始され、すべての出力の同期が高い精度で実現されます。この場合も、出力をパルス・モードに設定し、 SYSREF パルスとして使用することが可能です。

本稿で提案しているクロック・ツリー構造では、基本的に SYSREFを次のレベルの HMC7043への RFSYNC信号として供給することにより、各レベルの出力における位相のアラインメントを実現します。アーキテクチャを慎重に設計することにより、これらすべてのタイミング信号がデタミニスティックになり、厳格なスキュー制御を行えるようになります。また、各デバイスは、アナログ方式の遅延構造を備えています。それを利用することにより、出力間のスキューの差や配線長の不均等をソース側で補償できるようになっています。

最近のRFシステムでは、複雑なデータ・コンバータ・アレイが使用されます。その場合、ADC、DAC、FPGA、局部発振器、ミキサーには周波数の異なるクロックが供給される可能性があります。つまり、様々な周波数が必要になるかもしれないということです。HMC7044とHMC7043はいずれも分周器を内蔵しており、複数種の周波数信号を生成することができます。また、HMC7044は、VCOを備えるデュアルPLL構造を搭載しています。そのため、部品を追加することなく周波数の高いクロックを生成することが可能です。

一般的な通信システムでは、更に複雑な状況になります。そうしたシステムの場合、RFフロント・エンド・ユニットのほとんどは、送信/受信ブロックに対するシリアル・インターフェースに依存しています。そのため、デジタル・プロセッサあるいは FPGAによってデータとクロックをエンベデッド/デエンベデッドしなければなりません。多くの場合、このプロセスによって、リファレンス・クロックに不要なジッタが生じます。したがって、RFクロックの生成/分配デバイスは、HMC7044のようにジッタの減衰機能を備えていなければなりません。

図4に、データ・コンバータ・アレイに適用可能なコンパクトなソリューションを示しました。

図4. 4レベルのクロック・ツリーを実現するコンパクトなソリューション

評価の結果

図5は、全出力の間のスキューを示したものです。黄色とシアン(青緑色)で示した信号は、第4レベルの出力に対応するパルス状のSYSREFと連続クロック信号です。ご覧のように、追加で遅延の調整を行うことなく同期が実現されています。青色で示した信号は、HMC7044からの連続SYSREF信号です。この信号については、アナログ方式の遅延機能を使用することによって第4レベルの出力との同期を実現しています。この例では、トータルのスキューが16ピコ秒未満に抑えられています。

図 5. 4 レベルの出力。時間領域の応答を示しています。

図6に示したのは、4レベルのクロック・ツリーにおける位相ノイズ性能です。クロック・ジェネレータの位相ノイズも薄い青色の線で示してあります。2MHzのオフセット位置までトータルの位相ノイズは悪化していません。ただ、各レベルの付加ノイズ(付加ジッタ)を考慮すると、ノイズ・フロアの悪化は避けられません。実際、このグラフでは6dBのノイズの増加が確認できます。HMC7044とHMC7043の出力ノイズ・フロアは同等(約-154dBc/Hz)であり、4つのデバイスからのノイズは-148dBc/Hzに悪化しています。とはいえ、これはほとんどのシステムで許容できるレベルです。

図 6. 4 レベルの出力の周波数応答

2457.6MHzにおいて12kHzから20MHzの範囲で積分したノイズとしては、52.7フェムト秒というrmsジッタが算出されます。HMC7044の出力について言えば、わずか数フェムト秒rmsしか悪化していません。現実のシステムでは、このレベルの悪化はほぼ間違いなく許容できます。許容できない場合には、最終段のHMC7043をHMC7044で置き換えるとよいでしょう。そうすれば、クロック・ツリー自体の累積ジッタを減衰させることができます。

先述したように、多数のデータ・コンバータを使用するシステムでは、消費電力が非常に重要な問題になります。クロック・ツリーの消費電力について言えば、使用するシグナリング・モードが重要な要因になります。 HMC7044 と HMC7043 の出力シグナリング・モードは、ソフトウェアによって互いに独立した形で制御/変更することができます。それにより、消費電力/駆動能力と周波数の間でトレードオフを実施することが可能になります。一般的なガイドラインとして、低い周波数では LVDS ( Low Voltage Differential Signaling )を使用して消費電力を削減します。一方、高い周波数では LVPECL ( Low Voltage Positive Emitter-Coupled Logic ) や CML ( Current Mode Logic )を使用することによって最高の性能を求めることになるでしょう。

まとめ

本稿で説明した内容は、大規模かつ分散型のデータ・コンバータ・アレイを利用する様々なシステムに当てはまります。例えば、ワイヤレス・システムのインフラや防衛用のレーダー、試験/計測システムなどが該当します。5Gのシステムでは周波数がより高く、帯域幅がより広い変調方式が使われています。そうしたシステムは、複数のRF入出力インターフェースのトレンドに基づいて構築されており、データ変換パスの数を増やすことが必要になります。

また、5Gの一部のアーキテクチャでは、電力を節約しつつ出力容量を増加させる手段として、フェーズド・アレイ・アンテナが使用されています。フェーズド・アレイは、防衛用の通信システムで広く用いられている技術です。この技術には、多数のクロックが必要になります。そして、それらのクロックは正確に同期していなければなりません。

大規模なデータ・コンバータ・アレイにはもう1つ重要なユース・ケースがあります。それは試験/計測システムです。その種のシステムでは、高いサンプリング・レートで大量のデータを取得し、ノイズを可能な限り抑えつつ、同時に処理を実現する必要があります。そのためには、同期のとれた多数のクロックが必要です。同様に、高度な医療用画像診断システムでは、データ処理のスループットを高めなければなりません。そのため、並列のデータ・アクイジション・パスを同期した状態で動作させる必要があります。

本稿で説明したように、 ICメーカーは、そうした高度な設計を実現するために創造的かつ実用的なソリューションを生み出しています。 HMC7044 や HMC7043 などの製品は、システムの課題を念頭に置いて開発されたものです。それらを利用すれば、性能と柔軟性に優れるクロック・ツリーを構築できます。そのようなクロック・ツリーであれば、レベルの拡張に柔軟に対応しつつ、デタミニスティックに位相の精度を維持することが可能になります。