帯域幅が30MHzを超え、SNRが64dBでSFDRが80dBの325MHz IFサンプリング・システムのリファレンス・クロック分配

リファレンス・クロックのバッファ処理と分配によってRFレシーバに生じたクロック・ジッタは、システム性能を制限することがあります。フロントエンド・フィルタ要件緩和の成果を得る目的で比較的高い中間周波数(IF)を使用する場合は、ジッタが小さいという要件がさらに重要となります。この記事では、325MHz IFサンプリング・システムの設計について詳しく説明し、発生するジッタを最小限に抑えつつ、正弦波のリファレンス信号を、高速A/Dコンバータを駆動するのに適した1対の差動LVPECLクロックに変換するクロック・バッファおよび分配器を紹介します。

システムの説明

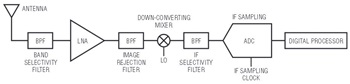

RFレシーバでのダウンコンバージョンの最終段をA/Dコンバータが実行するIFサンプリング(またはアンダーサンプリング)システムでは、IFの周波数が高いほど、RFフロントエンドでのイメージ除去フィルタの特性条件を緩和することができます。このことはフィルタのコスト、サイズ、および挿入損失の低減に役立ち、それによって増幅の必要性が下げられるので、一層の低コスト化および低消費電力化につながります。IFサンプリングを採用している標準的なRFレシーバ・チェーンを図1に示します。

図1.標準的なシングルIF段 RFレシーバのブロック図

比較的高いIFでレシーバを設計することのマイナス面は、高い周波数のアナログ入力信号をサンプリングする際のA/Dコンバータの性能の低下が、システム全体の性能に与える影響がより大きくなることです。たとえば、A/DコンバータのSFDR(スプリアス・フリー・ダイナミックレンジ)は、入力周波数が高くなるほど悪化します。さらに重要なことは、より高い周波数の入力をサンプリングする際に、A/Dコンバータのアパーチャ・ジッタとそのクロック・ジッタの組み合わせによる影響が、信号対ノイズ比(SNR)を低下させ始めることです。

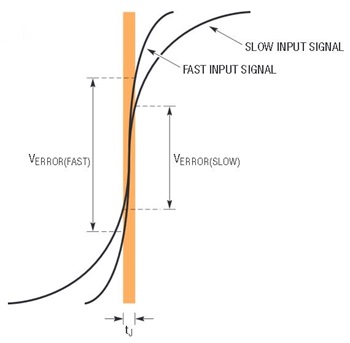

クロック・ジッタの影響を実例で示すには、同じA/Dコンバータと同じクロックを使用し、2つのスルーイング信号(一方は他方より傾斜の高い信号)をサンプリング中、クロック・ジッタに起因する電圧誤差の大きさを比較します。図2に示すように、2つの信号をサンプリングしているとき、このクロックには同じ大きさの時間ジッタ(tJ:単位はs-RMS)が存在します。変動速度が速い信号に対する方が、クロック・ジッタの不確実性の影響が大きいので、アナログ入力に高周波成分が含まれる場合、クロック・ジッタはSNRを低下させる主要な誤差原因の一つになります。したがって、A/Dコンバータのクロックのジッタは、図1のIFサンプリング・クロックに示すように、できるだけ小さくしておくことが重要です。

図2.低速および高速で変化する信号をデジタル化する際のクロック・ジッタの影響

A/Dコンバータのクロック入力でのAM-PMノイズ変換を避けるため、クロックのスルーレートは高くすることが必要であり、方形波が理想です。A/Dコンバータのクロック入力はリミッタの役目を果たし、信号を取り込み、入力信号のゼロ交差(または他の基準)で判定することによって方形にします。AM-PMノイズ変換が行われるのは、低周波または低振幅の正弦波のように、入力信号のスルーレートが低く、方形波と比較するとスロー・モーションのような信号の場合であり、信号がゼロ交差点を通過する時点です。抵抗の熱ノイズ、電源からのノイズなど、何らかの種類のAMノイズが存在すると、入力信号のゼロ交差点はエッジ間で一致しなくなり、結果としてリミッタの出力でジッタが発生することになるので、AMノイズはPMノイズに変換されます。ところが、入力信号がゼロ点を交差する場合でも、LVPECL信号の立ち上がり時間および立ち下がり時間が短いため、クロックに加えられたAMノイズがPMノイズに変換されることほとんどありません。

また、最新のA/Dコンバータは最高の性能を実現するためにクロック入力を差動で駆動することが必要です。クロック信号の送信元と送信先を互いに近づけて配置することは通常ないので、クロック信号の配線は一般にPCB上でかなり長い距離になります。クロック信号を差動形式で送ると、結合の影響を受けなくなり、シングルエンドのクロック配線と比べて全体としてより堅牢な設計になります。

図1に示すLO信号の発生元は、通常はフェーズロック・ループ(PLL)システムです。PLLでは、LOのロック元としてリファレンス・クロックが必要です。従来は10MHz が一般的なリファレンス周波数でした。しかし、現在ではより高周波のリファレンス・クロックが一般的になりつつあります。現に、最近のRF設計では100MHz 以上のリファレンス周波数は珍しくありません。

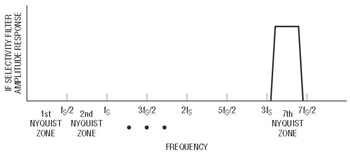

リファレンス・クロックは、一般にOCXOデバイスまたはTCXOデバイスから発生させており、通常は非常に低いジッタと位相ノイズを有しています。受信RFチャネルの帯域幅(または2つ以上の隣接チャネルを同時にデジタル化するレシーバでは複数チャネルの帯域幅)の2 倍より適度に高くなるようにPLLリファレンス周波数を選んで、正しい周波数計画を実施した場合には、同じリファレンス・クロックをIFサンプリングA/Dコンバータに使用することも可能です。IFフィルタの通過帯域とその移行帯の大部分がA/Dコンバータの単一のナイキスト・ゾーンに収まって周波数が折り返さないようにするのが理想です。これは図3に示すIFフィルタ振幅応答を見ることによって明確になります。ここで、IFはA/Dコンバータの第7ナイキスト・ゾーンに合致するように選択します。図3では、fSはA/Dコンバータのサンプリング・レートを表します。この場合、図1のLOは、ミキサーでダウンコンバートした中間周波数帯域の中心が、図3に示したIF選択フィルタの中心にくるように選択します。

図3.周波数の折り返しを防ぐA / Dコンバータのサンプリング・レートを基準にしたIFフィルタ振幅応答の例

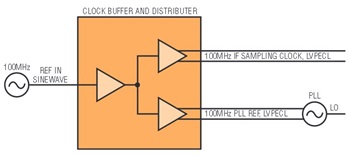

図4は、リファレンス周波数を100MHzと仮定して、前述したクロック分配方式をまとめたものです。図4のクロック・バッファおよび分配器は、このシステムで非常に重要な役割を果たします。OCXOデバイスまたはTCXOデバイスからシングルエンドの正弦波を受け取り、A/DコンバータおよびPLLへの転送に適した2 種類の差動LVPECL信号を配信しています。クロック・バッファおよび分配器はこの役割を果たしながらも、分配クロックに加わるジッタを最小限に抑えなければなりません。LTC6957-1は、付加ジッタの少ないデュアルLVPECL出力クロック・バッファで、このアプリケーションに適しており、前述したすべての条件を満たしています。LTC6957の別のバージョンを選ぶことにより、他の出力形式を採用することもできます。LTC6957-2はLVDS 出力を備えており、LTC6957-3とLTC6957-4はCMOS 出力を備えています。

図4.リファレンス・クロック分配方式

回路の実装

前述したように、ジッタはIFを高くした場合の性能を制限する主な要因の1 つです。一般的なA/Dコンバータへのクロック分配器としてLTC6957-1を使用した場合にどれ位の性能が得られるかを調べるために、図5に示すようにリニアテクノロジーの2つのデモ回路を変更して接続してみました。

図5.315.5MHzの入力テスト・トーンと100MHzのリファレンス・クロックを使用する2つのリニアテクノロジー・デモボードを用いたIFサンプリング・システムの回路図

LTC2153-14は、高いアナログ入力周波数について性能を規定した310Msps、14ビットA/Dコンバータなので、このようなIFサンプリングA/Dコンバータとして適しています。そのデモ回路DC1565A-Gを図5に示すように変更しました。

LTC6957-1を搭載したデモ回路DC1765A-Aを使用して、100MHz OCXOの正弦波出力をバッファ処理します。DC1765A-Aの差動LVPECL出力の一方をDC1565A-Gの差動エンコード・クロック入力に接続します。もう一方は、図1に示したPLLを発生するLOのリファレンス入力として使用できます。

A/Dコンバータが100MHz のクロックで動作するとした場合、折り返しエラーが発生しないようにした上で理論上実現可能な最大の帯域幅は50MHzです。図3に示したように、第7ナイキスト・ゾーンを選択しているので、この50MHzの理想帯域幅は300MHz~350MHz の周波数範囲をカバーすることになります。このためには、300MHz~350MHz の範囲に存在するIF情報だけを通過させ、その一方で、折り返しを発生して目的の帯域に干渉するすべての信号を除去できる、中心周波数が325MHzで通過帯域が50MHz の理想的なバンドパス・フィルタが必要です。

実際のフィルタではフィルタの通過帯域と遮断領域の間に移行帯があり、更に中心周波数の許容範囲が加わるので、この場合さらに適正なIF帯域幅を選択すると、たとえば中心が325MHz付近にあり帯域幅が30MHz の表面弾性波(SAW)フィルタになります。この周波数範囲内でのSAWフィルタは、簡単に手に入るようになりつつあります。

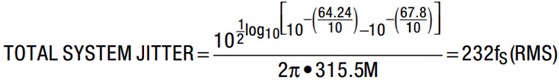

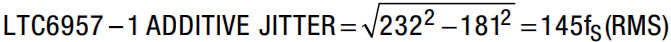

LTC6957-1付加ジッタの計算

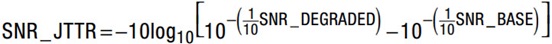

サンプリング・システムでは、ジッタは通常、2段階の手順で測定されます。第1段階では、ジッタがノイズの大きな発生要因ではない–1dBFSで比較的低周波のアナログ入力トーンを入力して基準線のSNR測定を行います。この測定をSNR_BASEと呼びます。2回目の測定は、1回目の測定と同じサンプリング・クロック信号源を使用しますが、周波数の高いアナログ入力トーンを入力します(引き続き-1dBFS)。ジッタによるSNRの低下の影響が無視できなくなるほど高い入力周波数を選んだ場合には、2回目の測定でSNRが低下します。この2回目の測定をSNR_DEGRADEDと呼びます。2回目の測定では、サンプリング・クロック、A/Dコンバータのアパーチャ・ジッタ、アナログ入力信号など、ジッタの発生源が複数考えられることに注意してください。2回の測定のRMS値の差をとることにより、A/Dコンバータのアナログ入力における量子化ノイズと熱ノイズの影響を除いた、高い入力周波数でのジッタによるSNRの低下が得られます。この計算値をSNR_JTTRと呼びます。これら3つの用語は次のように関連しています。

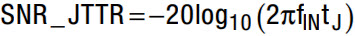

アナログ入力トーンが周波数fINの場合、A/Dコンバータのエンコード入力での全ジッタのtJ の大きさに起因するSNR (SNR_JTTR) の値は次のとおりです。

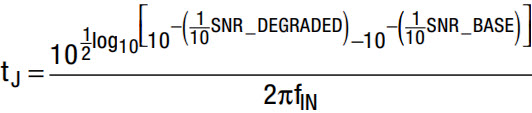

これら2つの式を組み合わせてtJ について解くと、前述した2回の測定結果からシステムのジッタを直接計算する式が得られます。

LTC6957-1のジッタへの影響は、前に概説した手順に従って測定します。図5に示す回路図に基づいて2回の測定を行います。1回目はもともとあるシステム・ジッタを測定します。これには、A/Dコンバータのアパーチャ・ジッタや100MHzと315.5MHz の信号源のジッタが含まれていますが、LTC6957-1のジッタは含まれていません。2回目の結果には、LTC6957-1のノイズへの影響が含まれています。2回の測定間でのRMS値の差をとることにより、LTC6957-1が付加したジッタが得られます。

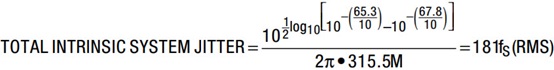

LTC6957-1の影響を除いた、もともとのシステム・ジッタは、トランスを使用して、100MHz、13dBmの信号源をA/Dコンバータのエンコード入力に直接接続し、クロック入力を差動で駆動することによって求めます。2回のSNR測定を、高調波成分を除いて行います。1回目は、A/Dコンバータのアナログ入力に10MHz、–1dBFSの正弦波を入力し、67.8dBという結果でした。A/Dコンバータのアナログ入力に315.5MHz、–1 dBFSのトーンを入力して2回目のSNR測定を行った結果、SNRは65.3 dBとなりました。前の説明で得られている式により、もともとのシステム・ジッタを計算します。

図5に示すように、LTC6957-1をシステムに加えた後のシステム・ジッタを求めるには、同様な2組の測定を別途行います。前の段落で説明したように、まず10MHz のアナログ入力で測定し、次に315.5MHz のアナログ入力で測定します。SNRの2つの数値は、それぞれ67.8 dBおよび64.24 dBです。前と同じジッタの式を使用すると、全システム・ジッタは次のようになります。

もともとのシステム・ジッタと全システム・ジッタのRMS値の差をとると、LTC6957-1の付加ジッタへの影響が分かります。

性能のまとめ

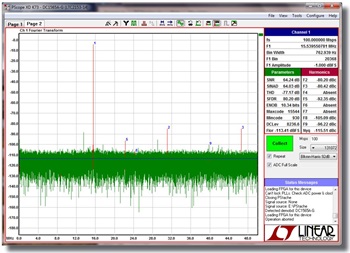

315.5MHz のテスト・トーンを、IF選択フィルタに似たBPFとアッテネータを介して変更後のDC1565A-Gのアナログ入力に接続し、A/Dコンバータ側から見た振幅を–1dBFS に調整します。

DC1565A-GはUSBを介してPCに接続されます。PCでは、PScope1データ収集制御ソフトウェアを使用して、レシーバの品質に影響する2つの非常に重要なパラメータを調べます。それはSNRおよびSFDRです。動作中のPScope™を図6に示します。131072ポイントのFFT(フーリエ変換)解析に加えていくつかの解析結果が表示されています。ここでは、A/Dコンバータのアナログ入力として315.5MHz、–1dBFSのトーン、およびA/Dコンバータのエンコード・クロックとしてLTC6957-1によってバッファ処理された100MHz のLVPECL 信号を使用しています。図6から分かるように、達成されたSNRは64dBを超えており、SFDRは80dBを超えています。これらは325MHz IFサンプリング・システムとして非常に優れた値です。

図6.図5に示すシステムのFFTと達成された信号品位パラメータを示すPScopeのスクリーンショット

LTC6957-1 の入力は100MHz の正弦波で、50Ω 終端での電力が+10dBmなので、その内部帯域幅制限フィルタ(FILTAおよびFILTB)は、LTC6957データシートの推奨に従って、両方ともオフにしています。これらのフィルタは、入力振幅が小さいか入力周波数が低い、あるいはその両方が低い場合、付加ジッタの量を減らすのに役立ちます。

まとめ

RFレシーバの一部として、325MHz IF サンプリング・システムを構築し、評価しました。低ジッタのクロック・バッファおよび分配器(LTC6957-1)を採用して100MHz のシステム・リファレンス・クロックをLVPECL形式で分配し、A/Dコンバータのサンプリング・クロックおよびPLLリファレンスとして使用します。IFサンプリング・システムの性能は、SNRとSFDRの数値を調べることによって評価します。測定の結果、64dBという優れたSNRと、80dBという抜群のSFDRが実現されることが示され、高いIFサンプリング周波数を用いることによるRFイメージ除去フィルタの要件緩和が可能であることが示されました。

注記

1 PScope は、A/Dコンバータからデータを収集して、時間領域と周波数領域の両方で分析し、関連パラメータを表示します(tspice.analog.com/software/ltcps.exeでダウンロード可能)。