概要

設計リソース

設計/統合ファイル

- Schematic

- Bill of Materials

- Gerber Files

- Altium Layout Files

- Assembly Drawing

評価用ボード

型番に"Z"が付いているものは、RoHS対応製品です。 本回路の評価には以下の評価用ボードが必要です。

- EVAL-CN0335-PMDZ ($54.14) 12-Bit, 300 kSPS, Single-Supply, Fully Isolated, Data Acquisition System for ±10 V Inputs

- EVAL-SDP-CB1Z ($134.00) Eval Control Board

- SDP-PMD-IB1Z ($74.45) PMOD to SDP Interposer Board

デバイス・ドライバ

コンポーネントのデジタル・インターフェースとを介して通信するために使用されるCコードやFPGAコードなどのソフトウェアです。

機能と利点

- 産業レベルの信号処理

- 単電源

- 完全な絶縁

製品カテゴリ

マーケット & テクノロジー

使用されている製品

参考資料

-

AN-825: iCoupler®アイソレーション製品での電源の考慮事項 (Rev. 0)2006/11/01PDF340 kB

-

CN0335 Software User Guide2018/10/10WIKI

-

MT-101: Decoupling Techniques2015/02/14PDF954 kB

-

MT-031: データ・コンバータのグラウンディングと、「AGND」および「DGND」に関する疑問の解消2009/03/20PDF144 kB

-

CN-0335: ±10 V入力、12ビット、300 kSPS、単電源、完全絶縁の データ・アクイジション・システム2014/03/03PDF270 kB

回路機能とその特長

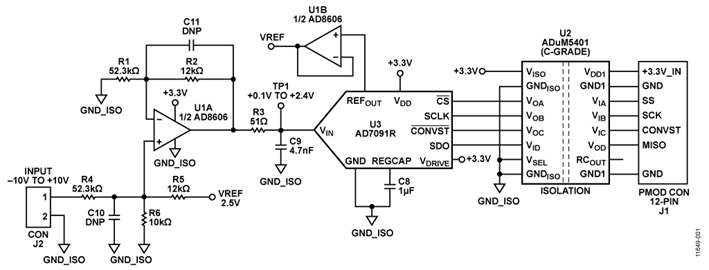

図 1に示す回路はわずか3個のアクティブ・デバイスからなる完全に絶縁された12ビット、300 kSPSデータ・アクイジション・システムです。

システムは単電源3.3 Vを使用して±10 Vの入力信号を処理します。室温でキャリブレーションした後の総合誤差は±10°Cの温度変化に対して±0.1% FSR以下なので、各種工業測定に理想的です。

この組み合わせは回路のフットプリントが小さいので、精度、速度、価格、大きさが重要な役割となるデータ・アクイジション・システムの業界最先端のソリューションとなります。データと電源の両方が絶縁されているので、この回路は高電圧、あるいは激しい産業環境で起こるグラウンド-ループ干渉に対しても強固です。

回路説明

回路は入力信号処理段、ADC段、出力アイソレーション段で構成されています。±10 Vの入力信号はレベル・シフトされ、デュアル・オペアンプAD8606の片方のオペアンプU1Aで減衰されます。オペアンプの出力は0.1 V ~ 2.4 Vで、直線性を維持するため100 mV ヘッドルームを計算にいれるとADCの入力範囲(0 V ~ 2.5 V)に一致します。ADCから得られるバッファ付き電圧リファレンス(VREF =2.5 V)は必要なオフセット電圧を生成します。この回路ノートで後ほど述べますが、抵抗値は他の良く使用される入力範囲に合わせて変更することができます。

回路は単電源動作が可能です。AD8606の最小出力電圧の仕様は負荷電流を10 mAとすると、温度範囲−40°C ~ +125°C全体で、2.7 V電源の場合50 mV、5V電源の場合290 mVです。 電源が3.3 V、負荷電流が1 mA以下で、温度範囲がもっと狭い場合には、最小出力電圧は概算で45 mV ~ 60 mV程です。

部品の公差を考慮し、安全余裕を持たせるために最小出力電圧(範囲の下限)を100 mV に設定します。出力範囲の上限はADCの入力での大振幅に対して100 mVヘッドルームを設けるために2.4 Vに設定します。従って入力オペアンプの公称出力電圧範囲は0.1 V ~ 2.4 Vになります。

AD8606のもう一方のオペアンプ(U1B)はADC (U3) のAD7091Rに内蔵されている2.5 V電圧リファレンスをバッファするために使用されます。

AD8606をこのアプリケーションに選択する理由はその低オフセット電圧(65 μV max)、低バイアス電流(1pA max)、低ノイズ(12 nV/√Hz max)によります。消費電力は3.3 V電源でわずか9.2 mWです。

帯域外ノイズを減らすためにオペアンプの出力段の後に1極RCフィルタ(R3/C9) を接続します。RCフィルタのカットオフ周波数を664 kHzに設定します。低周波数のノイズの場合で、さらにフィルタ・カット・オフ周波数を下げる必要のある場合には、オプションで2次フィルタ(R4、 C10 と R1、 R2、 C11)を接続する事ができます。このような場合には、信号帯域幅が低いのでAD7091Rのサンプリング・レートを下げる事ができます。

12ビット、1MSPS、SAR ADCのAD7091Rを選択した理由は消費電力が3.3 Vで349 μA(1.2 mW)と極めて低いからですが、これは現在市販のどの競合品よりも極めて低くなっております。AD7091Rは又温度ドリフト±4.5 ppm/oC typの2.5 Vリファレンスを内蔵しています。入力帯域幅は7.5MHzで、高速シリアル・インターフェースはSPI互換です。AD7091Rは小フットプリントの10ピンMSOPを採用しています。

(アイソレータADuM5401を除く)この回路の全消費電力は3.3V電源動作で約10.4 mWです。 回路は4チャンネル・デジタル・アイソレータADuM5401 (Cグレード) によってDC的に絶縁されます。デジタル・アイソレータADuM5401は絶縁された出力データに加え、回路用に絶縁された3.3 V電源も供給します。ADuM5401は絶縁する必要のない通常の回路動作には必要ありません。DC/DCコンバータ内蔵の4チャンネル、2.5 kVアイソレータADuM5401は小型16ピンSOICを採用しています。 ADuM5401の消費電力は7 MHzクロックの場合約140 mWです。

1 MSPS サンプリング・レートを実現するためにAD7091Rは50 MHzのシリアル・クロック(SCLK)を必要とします。しかし、アイソレータADuM5401(Cグレード)の最大データレートは25 Mbpsで、それは最大シリアル・クロック周波数12.5 MHzに相当します。さらに、SPIポートはSCLKクロックの後方エッジで出力データをプロセッサに入力する事が必要です。。従ってクロック周波数の上限はADuM5401を通る全体のラウンドトリップ伝播遅延(120ns max)によって1/120 ns = 8.3 MHzに制限されます。

AD7091Rは12ビットADCですが、プロセッサのシリアル・ポートの条件と互換性をもたせるために、シリアル・データは16ビット・ワードにフォーマットされます。従って、サンプリング周期”Ts”はAD7091Rの変換時間650 ns+58ns(データシートで要求されている余分な時間: 遅延t1+遅延tQUIET)+SPIインターフェースのデータ転送に必要な16クロック・サイクルで構成されます。

TS = 650 ns + 58 ns + 16 × 120 ns = 2628 ns

fS = 1/TS = 1/2628 ns = 380 kSPS

安全余裕をもたせるために、7 MHzの最大SCLKと300 kSPSの最大サンプリング・レートをお勧めします。デジタルSPIインターフェースは12ピンPmod準拠コネクタ(ディジレントPmod仕様)を使用してマイクロプロセッサの評価用ボードに接続できます。

回路デザイン

図 2に示す回路は −10 V ~ +10 Vの入力信号を減衰、しレベル・シフトしてADCの入力範囲の0.1 V ~ 2.4 Vにします。

ゲイン、出力オフセット、抵抗値の計算

入力電圧範囲が±10 Vの場合、計算は次のようになります。

実際の回路ではR4 と R5に最も近い値の供給可能な標準抵抗値を選択しました。選択した値はR4 = 52.3 kΩ そして R5 = 12 kΩです。R1 = R4そして R2 = R5である事に注意してください。

これらの値を注意して選択すれば、標準抵抗値で置換える事による全体の誤差は数パーセント以下になるでしょう。しかし、必要なヘッドルームが確実に維持されるように、式1を使用して入力±10 Vの場合のU1Aオペアンプの出力を再計算してください。<

このタイプの回路の絶対精度は主に抵抗よって決まります。従って標準抵抗値の代入や抵抗公差による誤差を取り除くためにゲインやオフセットのキャリブレーションを行う必要があります。

入力範囲が異なる場合の抵抗値の計算

入力範囲が±10 V 以外の場合、次のステップで計算を行います。

式17と式18の中のRとR0を式2で定義した値で置き換え、両方の式を解いて、比率R4/R6を求めます。

抵抗R6の値を選びます:比率R4/R6を使用してR4を計算します。R4 と R6の値がわかったら、式2と比率R4/R6を使いR5を計算します。式16を使いR2とR1を計算します。R1 = R4とし、R2を計算するのは妥当です。

抵抗の温度係数が全体の誤差に及ぼす影響

式1から出力電圧は5個の抵抗(R1、 R2、 R4、 R5、 R6)の関数である事がわかります。5個の各抵抗の小さな変化に対するTP1でのフルスケール出力電圧の感度をシミュレーション・プログラムを使用して計算しました。回路に入力した電圧は+10 Vです。各々の感度を計算した結果SR1 = 0.19、 SR2 = 0.19、 SR4 = 0.39、 SR5 = 0.11、 SR6 = 0.50となりました。各々の温度係数は2乗和平方根(RSS)方法で結合されると仮定すると、100 ppm/°Cの抵抗を使った場合の全体のフルスケール・ドリフトはおおよそ次の通りです:

Full scale drift =

=100 ppm/°C √(SR12 + SR22 + SR42 + SR52 + SR62)

=100 ppm/°C √(0.192 + 0.192 + 0.392 + 0.112 + 0.502)

= 69 ppm/°C

69 ppm/°Cのフルスケール・ドリフトは0.0069% FSR/°Cに相当します。25 ppm/°Cの抵抗を使用すれば、ドリフト誤差は69 ppm/°C = 17 ppm/°C又は 0.0017% FSR/°Cに軽減します。

能動部品の温度係数が全体の誤差に及ぼす影響

オペアンプAD8606とADCのAD7091RのDCオフセットはキャリブレーションにより軽減されます。

ADCのAD7091Rに内蔵しているリファレンスのオフセット・ドリフトは4.5 ppm/°C typで25 ppm/°C maxです。

オペアンプAD8606のオフセット・ドリフトは1μV/°C typで4.5μV/°C maxです。

入力アンプU1AのAD8606による誤差は出力範囲2.3 Vを基準とするので2 ppm/°Cです。U1Bリファレンス・バッファによる誤差は2.5 Vを基準とするのでやはり約2 ppm/°Cです。

表1にドリフト誤差を全てまとめました。これらの誤差にはAD7091Rの±1 LSB積分非直線性誤差は含まれていません。

50 ppm/°C あるいは100 ppm/°Cの抵抗を使用すると、抵抗によるドリフトは全体のドリフトに最も大きな影響がある事に注意してください。

| Error Source | Total Error |

| Resistors (1%, 100 ppm/°C) | ±0.0069% FSR/°C |

| AD7091R (∆VVREF/∆T = 25 ppm/°C) | ±0.0025% FSR/°C |

| AD8606, U1A (∆VOS/∆T= 4.5 μV/°C), 2

ppm/°C, Referenced to 2.3 V |

±0.0002% FSR/°C |

| AD8606, U1B (∆VOS/∆T= 4.5 μV/°C), 2

ppm/°C, Referenced to 2.5 V |

±0.0002% FSR/°C |

| Total FSR Error Temperature Coefficient

(100 ppm/°C Resistors) |

±0.0098% FSR/°C |

| Total % FSR Error for ∆T=±10°C (100 ppm/°C

Resistors) |

±0.098% FSR |

| Total % FSR Error for ∆T=±10°C (25 ppm/°C

Resistors) |

±0.046% FSR |

2点キャリブレーションの前と後のテスト・データ

2点キャリブレーションを行うために、入力に初め−10 V を印加し、その時のADC出力コードをコード1として記録します。次に入力に+10 Vを加え、その時のADCの出力コードをコード2として記録します。ゲイン係数を次の式で計算します。

キャリブレーション前の誤差は部品の公称値を使って計算された理想伝達関数とキャリブレーション無しの実際の回路伝達関数を比較する事により得られます。テストする回路は許容誤差±1%の抵抗を使用して作成されました。テスト結果には温度変化は含まれません。

図 3のグラフはテスト結果を室温でのキャリブレーションの前と後のパーセント誤差(FSR)で示しています。グラフからわかるように、キャリブレーション前の最大誤差は約0.23% FSRです。キャリブレーションした後、誤差は±0.03% FSRに下がりますが、それはほぼADCの1 LSB誤差に相当します。

プリント基板レイアウト時の考慮事項

高精度が要求される回路では、ボード上の電源とグラウンド・リターンのレイアウトを注意深く行う事が重要です。PCBはアナログ部とデジタル部をできる限り分離してください。このシステムのPCBは簡単な2層積み重ねで構成されていますが、4層積み重ねの方がより優れたEMCが得られます。レイアウトとグラウンディングに関するさらに詳しい内容はMT-031 Tutorialを、そしてデカップリング技術に関する情報についてはMT-101 Tutorialをご覧ください。適切にノイズを抑制しリップルを削減するためにAD8606に接続する電源を10 μF と 0.1 μFのコンデンサでデカップリングしてください。これらコンデンサには低ESR値の0.1 μFコンデンサを使用し、可能な限りデバイスの近くに配置してください。すべての高周波デカップリング・コンデンサにはセラミック・コンデンサを推奨します。電源ラインはできるだけ太いパターンにして低インピーダンス経路とし、電源ライン上のグリッチによる影響を軽減させる必要があります。

DC/DCコンバータを内蔵したisoPower ADuM5401は入力と出力の電源ピンに電源バイパスを必要とします。1ピンと2ピンの間と15ピンと16ピンの間のチップパッドのできるだけ近くに低ESRのバイパス・コンデンサが要求されます。ノイズを抑制しリップルを減らすには、少なくとも2個のコンデンサの並列組み合わせが必要です。VDD1 と VISOに使用する推奨コンデンサの値は0.1 μF と 10 μFです。小さい方のコンデンサはESRが低くなければなりません。たとえば、セラミック・コンデンサの使用をお勧めします。低ESRコンデンサの両端と電源入力ピンの間の全パターン長は2mm以下にする必要があります。バイパス・コンデンサを2mm以上のパターン長で取り付けるとデータ破壊を招く可能性があります。両方の共通グラウンド・ピンがパッケージ近くで相互接続されていない場合は、1ピンと8ピン間のバイパスおよび9ピンと16ピン間のバイパスを考慮する必要があります。詳細についてはADuM5401のデータシートを参照してください。

回路、ボード・レイアウト、部品表(BOM)などの全部揃った技術文書パッケージが www.analog.com/CN0335-DesignSupportに載っております。

高電圧耐性

このPCBは2500Vの基本的な絶縁材の経験をもとに忠実に設計されています。2500 Vを超えた高電圧テストはお勧めできません。この評価ボードを高電圧で使用する時は注意を払ってださい、そして安全機能をPCBに依存しないでください、なぜなら評価ボードは高耐圧試験(hipot試験あるいは絶縁耐圧試験としても知られている)が行われていないかあるいは安全性について認定されていないからです。

バリエーション回路

この回路は、図に示された部品の値で、優れた安定性をもち高精度で動作する事が証明されています。この回路で±10Vの入力電圧範囲をデジタル出力に変換したり、この回路を他の各種アプリケーション向けに使用する場合に他の高精度オペアンプや他のADCを使用する事ができます。

図 1の回路は回路デザインセクションで提供した式に従って、±10 V以外の他の入力電圧範囲用に設計する事ができます。表 2に一部の標準的な電圧範囲のための抵抗の計算を示します。

| Range (V) | k | R4 (kΩ) | R5 (kΩ) | R6 (kΩ) |

| ±5 | 1.2 | 40.87 | 18.8 | 20 |

| ±2 | 2 | 32.174 | 37 | 20 |

| ±1 | 4 | 40.87 | 94 | 20 |

| 0 to 1 | 4 | 14.435 | 830 | 20 |

| 0 to 2 |

2 | 14.087 | 405 | 20 |

| 0 to 2.5 |

2 | 22.609 | 520 | 20 |

| 0 to 5 |

2 | 65.217 | 750 | 20 |

| 0 to 10 |

1 | 63.478 | 365 | 20 |

| 0 to 24 |

1 | 90.174 | 216 | 10 |

下限がゼロで上限がリファレンス電圧よりも高い場合、変換するためにゲイン倍する必要がない(k = 1)ので、回路は簡略化できます。例として入力範囲が0 V ~10 Vの場合を図 4に示します。

ADR391は高精度2.5 Vバンド・ギャップ電圧リファレンスですが、低消費電力、高精度(温度ドリフト9 ppm/°C)で小型TSOTパッケージを採用しています。

AD8608はAD8605のクワッド・バージョンで、もし他に高精度オペアンプが必要の場合には AD8606の代わりに使用できます。

AD8601、AD8602、AD8604は超低オフセット電圧、広信号帯域幅を特徴とするシングル、デュアル、クワッドのレールtoレール入/出力、単電源アンプで、AD8605、AD8606、 AD8608の代わりに使用できます。

AD7457は12ビット、100 kSPS、低消費電力のSAR ADCですが、300 kSPSのスループットが必要でなければ、電圧リファレンスADR391と組み合わせる事によりAD7091Rの代わりに使用できます。

回路の評価とテスト

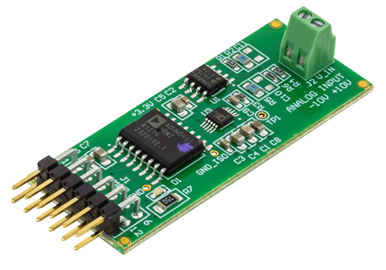

この回路は回路評価ボードEVAL-CN0335-PMDZ 、SDP-PMD-IB1Z 、 システム・デモ用プラットホーム (SDP) 評価ボードEVAL-SDP-CB1Zを使用します。インターポーザ・ボードSDP-PMD-IB1ZとSDP ボード EVAL-SDP-CB1Zには120ピン適合コネクタがあります。インターポーザ・ボードとEVAL-CN0335-PMDZボードには迅速な回路性能の設定と評価を可能とする12ピン Pmodマッチング・コネクタがあります。EVAL-CN0335-PMDZボードには(この回路ノートで述べたように)評価対象の回路が含まれており、EVAL-CN0335-PMDZ回路ボードからのデータを取り込むにはSDP評価ボードをCN0335 evaluation softwareと共に使用します。

必要な装置

- USBポート付きWindows® XP又はWindows Vista®(32-bit)又は Windows® 7/8 (64ビット又は32ビット)対応のPC

- EVAL-CN0335-PMDZ 回路評価ボード

- EVAL-SDP-CB1ZSDP評価ボード

- SDP-PMD-IB1Zインターポーザ・ボード

- CN0335評価ソフトウェア

- 高精度電圧源

始めてみよう

CN0335評価ソフトウェア・ディスクをPCのCDドライブに入れて評価ソフトウェアをロードしてください。又CN0335 evaluation softwareからもっとも最新の評価ソフトウェアをダウンロードできます。”マイコンピュタ”を使用して、評価ソフトウェア・ディスクのドライブを見つけ、setup.exeを開いてください。オンスクリーン・プロンプトに従いインストールを完了してください。すべてのソフトウェア部品を既定の領域にインストールする事をお勧めします。

機能ブロック図

図 5 にテスト・セットアップの機能ブロック図を示します。

セットアップ

- EVAL-CFTL-6V-PWRZ (+6 V DC電源)をDCバレル・ジャックを介してSDP-PMD-IB1Zインターポーザ・ボードに接続してください。

- SDP-PMD-IB1Z (インターポーザ・ボード) を120ピンConAコネクタを介してEVAL-SDP-CB1Z SDPボードに接続してください。

- EVAL-SDP-CB1Z (SDPボード)をUSBケーブルでPCに接続してください。

- EVAL-CN0335-PMDZ 評価ボード を12ピンヘッダー Pmod コネクタを介してEVAL-SDP-CB1Z インターポーザ・ボードに接続してください。

- 電圧源(電圧発生器)を端子ブロックJ2を介してEVAL-CN0335-PMDZ評価ボードに接続してください。

テスト

評価ソフトウェアを立ち上げます。アナログ・デバイセズのシステム開発プラットフォーム・ドライバがデバイス・マネージャにリストされていれば、ソフトウェアはSDPボードと通信します。1度USB通信が確立されれば、SDPボードを使ってEVAL-CN0335-PMDZボードからのシリアル・データの送信、受信、取り込みを行う事ができます。各種入力電圧の値に対するデータはコンピュータに保存できます。データ取り込みのための評価ソフトウェアの使用方法に関する情報と詳細はCN0335 Software User Guideに載っています。

EVAL-CN0335-PMDZボードの写真を図 6に示します。