概要

設計リソース

設計/統合ファイル

- Schematic

- Bill of Materials

- Gerber Files

- PADS Files

- Assembly Drawings

評価用ボード

型番に"Z"が付いているものは、RoHS対応製品です。 本回路の評価には以下の評価用ボードが必要です。

- EVAL-AD7176-2SDZ ($67.68) Precision 24-Bit, 250 kSPS Single-Supply Sigma-Delta ADC System for Industrial Signal Levels

- EVAL-SDP-CB1Z ($134.00) Eval Control Board

デバイス・ドライバ

コンポーネントのデジタル・インターフェースとを介して通信するために使用されるCコードやFPGAコードなどのソフトウェアです。

AD717x / AD411x IIO Sigma-Delta ADC Linux Driver

AD7173 GitHub Linux Driver Source Code

機能と利点

- 24-bit, 250kSPS ADC System

- Industrial Signal Levels

- Single Supply

製品カテゴリ

マーケット & テクノロジー

使用されている製品

参考資料

-

MT-101: Decoupling Techniques2015/02/14PDF954 kB

-

MT-076: Differential Driver Analysis2015/02/14PDF95 kB

-

MT-023: ADC Architectures IV: Sigma-Delta ADC Advanced Concepts and Applications2015/02/14PDF936 kB

-

MT-022: ADC Architectures III: Sigma-Delta ADC Basics2015/02/14PDF289 kB

-

MT-031: データ・コンバータのグラウンディングと、「AGND」および「DGND」に関する疑問の解消2009/03/20PDF144 kB

-

MT-004: The Good, the Bad, and the Ugly Aspects of ADC Input Noise - Is No Noise Good Noise?2009/03/04PDF342 kB

-

MT-075: 高速 ADC 向け差動ドライバの基礎と応用2009/02/03PDF0

-

MT-074: 高精度 A/D コンバータ用の差動ドライバ2009/02/03PDF358 kB

-

CN0310: 工業用信号レベル向け高精度、24ビット、250kSPS単電源Σ-ΔADCシステム2012/11/26PDF436 kB

回路機能とその特長

工業用信号をサンプリングする時、重要な事は高速で高分解能な変換情報を提供する事です。従来500 kSPSまでのサンプリングレートで供給可能な最も高い分解能のA/Dコンバータ(ADC)は14 ビット~18 ビットでした。

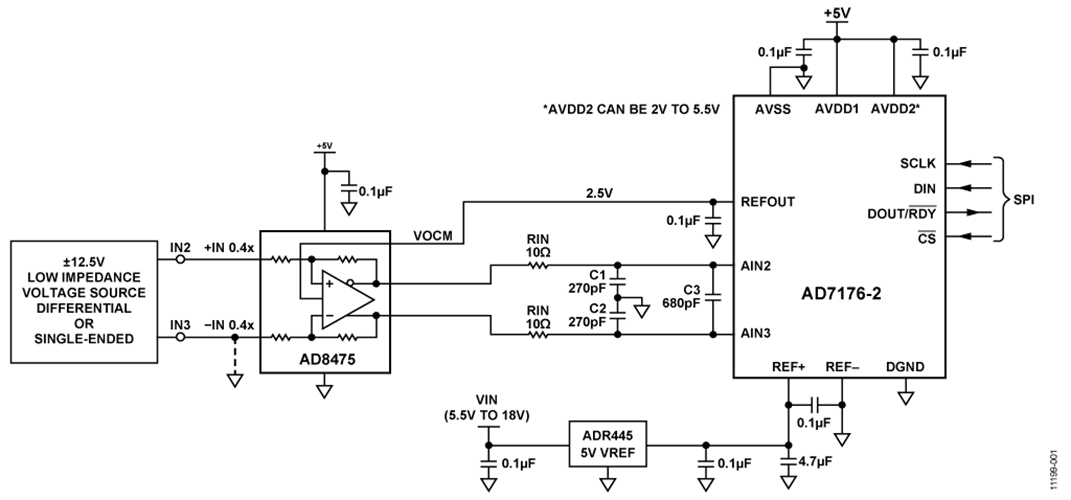

図 1に示す回路は24ビット、250 kSPSシグマデルタ(Σ-Δ)ADCを使って工業用信号をサンプリングするために最適化された単電源システムです。差動2チャンネル又は疑似差動4チャンネルの各々は17.2ビットのノイズフリー・コード分解能で最大50 kSPSのレートでスキャンできます。

この回路は±5 V、±10 V、0 V ~ 10 Vの標準工業用信号レベルを低電源電圧駆動の高精度ADCで取り込み、デジタル化までの間の考慮すべき点を、レザー・トリムした抵抗を内蔵した革新的な差動アンプを使用して減衰、レベル・シフトを行う事により解決しています。回路のアプリケーションにはプロセス・コントロール(PLC/DCS モジュール)、医療及び科学の多チャンネル機器、クロマトグラフィがあります。

回路説明

入力を0.8× 又は0.4×に減衰する高精度差動減衰アンプ AD8475 に工業用レベル信号を加えます。減衰はその集積化され、調整され、マッチングがとられた高精度抵抗によって制御されます。AD8475を単電源5V、ゲイン0.4×で動作させた時、抵抗により±12.5 Vまでのシングル・エンド入力又は差動入力が可能になります。入力には±15 Vまでの過電圧保護回路が内蔵されています。

AD8475 と AD7176-2 の組み合わせ回路の直線性は入力信号(0.4×のゲインを使用)が±10 Vシングル・エンド又は差動入力範囲以内の時維持されます。それは図 4の実測INLの限界に示されているように測定のエンドポイントは−10 V と+10 Vです。 この場合、AD8475の出力は0.5 V ~ 4.5 Vの範囲で振れます。

要求されるコモン・モード電圧をVOCMピンに加えて、コモン・モード出力を設定します。図 1の回路ではADCのAD7176-2 から2.5 VREFOUT電圧をAD8475のVOCMピンに加えてコモン・モード電圧を設定します。

AD8475はAD7176-2のサンプリング容量入力を駆動できるように減衰とレベル・シフトを行います。

アンプAD8475の出力はRCフィルタ回路へ接続されますが、このRCフィルタは差動ノイズとコモン・モード・ノイズのフィルタリングする共にAD7176-2の入力サンプリング容量によって要求されるダイナミックな充電を行います。又フィルタ回路はアンプ出力をダイナミックなスイッチド・キャパシタ入力からの全てのキックバックを遮断します。コモン・モード帯域(RIN、C1)は59 MHz、差動モード帯域(2 × RIN、0.5C1 + C3)は9.8 MHzです。

AD8475はシングル・エンド信号を入力できるように設定する事もできます。−IN 0.4×入力を接地し、+IN 0.4×入力にシングル・エンド信号を加えてください。

24ビット、Σ-Δ ADCのAD7176-2 はAD8475の出力をサンプリングし、それをデジタル信号に変換します。変換レートとデジタル・フィルタ性能は5 SPS ~ 250 kSPSの出力データ・レート範囲で調整可能です。 AD7176-2は完全差動の2入力又は疑似差動の4入力に設定できます。ADCの最大チャンネル・スキャンレートは50 kSPSです。AD7176-2のノイズフリービット性能は1250 kSPSで17.2 ビット、1 kSPSで20.8 ビット、50 SPS で21.7 ビットです。

図 2は入力を接地して測定したシステム全体の有効rmsノイズです。250 kSPSのデータ・レートの場合、有効rmsノイズは約30 μV rmsです。回路の直線性は±10 V入力をフルスケールにした時最良になる事を念頭において、計算のためのフルスケール入力を20 V p-pに設定しました。

20 Vのフルスケール入力範囲を規準としたビット表示の有効分解能は下記のように計算できます。

図 3は(入力を短絡して測定した)ビットrms表示の有効分解能を出力データ・レートの関数として表したグラフです。

最初にrmsノイズにファクタ6.6を乗算してrmsノイズをそのピークtoピーク・ノイズに変換する事により有効分解能をノイズフリー・コード分解能に変換する事ができます。その結果ノイズフリー・コード分解能を得るために有効分解能から差し引く必要のあるのは約2.7ビットになります。計算例として、19.3ビットの有効分解能は16.6ビットのノイズフリー・コード分解能と等価になります。これをバッファ無しで入力を短絡した時、250 kSPS出力データ・レートでノイズフリービットが17.2のAD7176-2の仕様と比較します。この約0.3ビットの差はフルスケール範囲として最大の±12.5 Vではなく、±10 Vを使用した事実の結果です。

図 4はエンドポイント手法を使いフルスケール・レンジのppmで表したシステムの積分非直線性(INL)です。

回路は主にDC入力用に設計されていますが、低周波AC入力も変換可能です。歪性能はアナログ入力振幅の大きさによって変わります。図 5と図 6はそれぞれ−1 dBFS と−6 dBFS の1 kHzサイン波を入力した時の性能を示します。サイン波入力はAudio Precision2700シリーズのオーディオ源から直接AD8475に供給されます。

高分解能システムで最適な性能を得るには、優れたプリント回路基板(PCB)レイアウト技術、グラウンディング技術、デカップリング技術が必須です。詳細については Tutorial MT-031、 Tutorial MT-101高分解能システムで最適な性能を得るには、優れたプリント回路基板(PCB)レイアウト技術、グラウンディング技術、デカップリング技術が必須です。詳細についてはCN-0310 設計支援パッケージに載っています。

回路の評価とテスト

評価に必要な装置

下記の装置が必要です:

- EVAL-AD7176-2SDZ評価用ボードとソフトウェア

- システム・デモ用プラットホーム (EVAL-SDP-CB1Z)

- 高精度DC電圧源

- Audio Precision 2700シリーズ(AC 入力)

- PC(Windows 32ビット又は64ビット)

- 7V~9V DC電源又はACアダプタ

ソフトウェアのインストール

AD7176-2 評価キットにはCDに自己インストール型ソフトウェアが含まれています。ソフトウェアはWindows® XP(SP2)、Windows Vista、Windows 7(32ビット又は64ビット)とコンパチブルです。もしセットアップ・ファイルが自動的に動作しなければCDからのsetup.exeファイルを実行してください。

PCに接続した時、評価システムが確実に正しく認識されるように、評価用ボードとSDPボードをPCのUSBポートに接続する前に評価用ソフトウェアをインストールしてください。

CDからのインストールが完了した後、EVAL-SDP-CB1Zを(コネクタA又はコネクタBを介して)EVAL-AD7176-2SDZに接続し、供給されるケーブルを使用してEVAL-SDP-CB1ZをPCのUSBポートに接続してください。

評価システムが検出されたら、表示するダイアログ・ボックスを通して進めてください。これでインストールが完了します。

セット・アップとテスト

ソフトウェアの使用とテストの実行に関する完全な詳細はユーザー・ガイド UG-478(英語)をご覧ください。

図 7にテスト・セットアップの機能ブロック図を示します。

図 1の回路をテストするには下記の小さなハードウェア変更が必要です。

- 信号はJ8端子ブロックのA2とA3からAD8475への入力です。

- SL9とSL10のはんだリンクをポジションCに変更してJ8のA2とA3からの信号をAD8475入力に配線してください。

- AD8475出力をAD7176-2のAIN2ピンとAIN3ピンに接続するためにR64とR74に10 Ω, 0603抵抗を実装してください。

- (ユーザー・ガイドUG-478に示されているように)ボードの下側のR110 とR120の抵抗を取り除いてください。