概要

設計リソース

設計/統合ファイル

- Schematic

- Bill of Materials

- Gerber Files

- PADS Files

- Assembly Drawing

評価用ボード

型番に"Z"が付いているものは、RoHS対応製品です。 本回路の評価には以下の評価用ボードが必要です。

- EVAL-AD7091RSDZ ($83.49) 12-Bit ,1 MSPS SAR ADC and Driver with Total Power Dissipation Less than 5 mW

- EVAL-SDP-CB1Z ($134.00) Eval Control Board

デバイス・ドライバ

コンポーネントのデジタル・インターフェースとを介して通信するために使用されるCコードやFPGAコードなどのソフトウェアです。

機能と利点

- 12-bit, 1MSPS Data Acquisition

- Single Supply

- 5mW Power

製品カテゴリ

マーケット & テクノロジー

使用されている製品

参考資料

-

MT-101: Decoupling Techniques2015/02/14PDF954 kB

-

MT-031: データ・コンバータのグラウンディングと、「AGND」および「DGND」に関する疑問の解消2009/03/20PDF144 kB

-

MT-036: Op Amp Output Phase-Reversal and Input Over-Voltage Protection2008/12/11PDF653 kB

-

CN0247: 全消費電力 5 mW以下の 12 ビット、1 MSPS SAR ADC+ドライバ2012/08/07PDF541 kB

回路機能とその特長

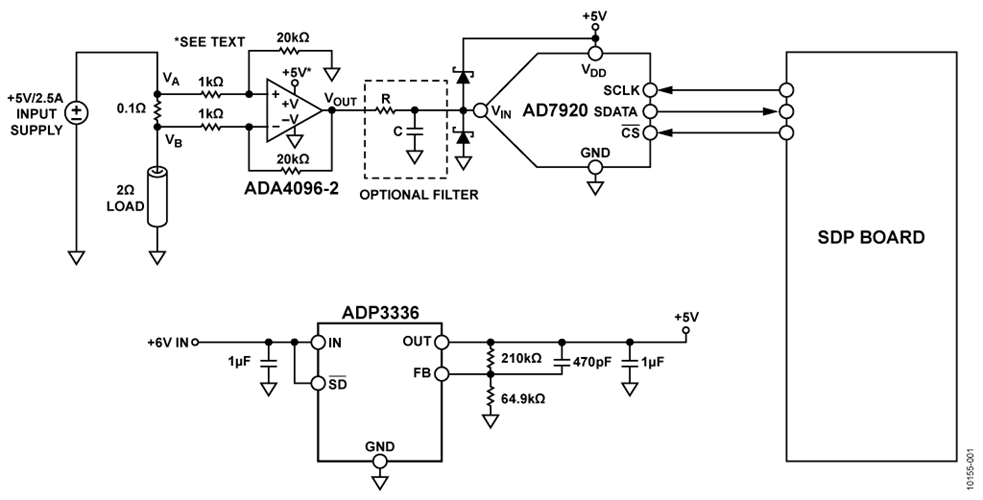

図 1に示す回路は12ビット、1 MSPS SAR ADCの AD7091R とオペアンプ・ドライバ AD8031 を使用した、単電源3Vで全消費電力5mW以下の超低消費電力データ・アクイジション・システムです。

選択した部品は低消費電力で小型パッケージなのでこの組み合わせは消費電力、価格、大きさが重要な要素の携帯用バッテリ駆動装置には業界最先端のソリューションとなります。

AD7091Rは3V電源でVDD 端子の電源電流はわずか350 μA(typ)要するだけで、今日市販されている他のどの競合ADCよりもはるかに小さくなっております。これは標準消費電力に換算すると~1 mWになります。

AD8031の消費電流はわずか800 μAなので、標準消費電力が3 V電源で2.4 mWとなり、システム全体の電力消費は10 kHzのアナログ入力信号を1 MSPSでサンプリングした場合5 mW以下になります。

回路説明

最適の性能が得られるように、ほとんどのSAR ADCはアナログ信号の為の適切な入力バッファを必要とします。バッファは内部のトラック&ホールド・スイッチがホールドからトラックに切り替わる時にADC入力で発生する過度信号から信号源を絶縁します。ADCを駆動するバッファはこの過度状態から回復しADCのアクイジション時間以内に要求されている精度に安定する必要があります。これは、信号源が高インピーダンスで、低歪みと高S/N比が重要なアプリケーションにおいては特に重要です。従って適切なバッファ・オペアンプを選択する事は、設計過程で重要な部分になります。

AD7091Rは2.5 Vリファレンス内蔵、12ビット、高速、超低消費電力、単電源ADCです。このデバイスは2.7 V~5.25 Vの電源電圧で動作します。AD7091Rは最大1 MSPSのスループット・レートが可能です。サンプリング・レート1 MSPSで、入力信号が10kHzの時、AD7091Rの全消費電力は約2.3 mWです。

表1に示すようにAD7091Rの電力はスループットに比例するので、1 MSPSサンプリング周波数が必要でないアプリケーションではこの消費電力の値を小さくする事ができます。

システムの電力消費をさらに小さくするためには、コンバータのスループット・レートを低くしてください。表1はAD7091Rが通常モードで動作している時の3V電源での標準的な消費電力対スループットを示します。

表1はパワーダウン・モードが駆動した時に実現可能な消費電力の減少を示します。パワーダウン・モードはAD7091Rをより低いスループット・レートで動作させる時、電源条件を大幅に下げる事ができる極めて有効な手段です。

AD7091Rは超小型3 mm × 2 mm 10ピンLFCSPパッケージ又は3 mm × 5 mm 10ピンMSOPパッケージを採用しています。2つのパッケージは競合品に対し大幅な省スペースになります。

AD8031はレールtoレール入出力、低消費電力オペアンプでAD7091Rの駆動アンプとして最適です。AD8031は2.7 V ~12 Vの電源電圧で動作するので、2つのICを同じ電源電圧で駆動する事ができます。AD8031は小信号帯域幅80 MHz、スルーレート30 V/μs、0.1%までのセトリング・タイム125 ns です。 AD8031の出力は単電源動作時に負側レールの20 mV以内まで振れます。

入力0 Vまでの直線性が必要な場合、AD8031に追加の負電源が必要です(チュートリアル Tutorial MT-035を参照)。

図1は、回路の簡略化した図です。100 nFと10 μFのセラミック・コンデンサを使用してIC電源ピンをグラウンドに対して十分にデカップリングしてください。これらのコンデンサを両方のICの電源ピンにできるだけ近く配置してください。

ADCに加わるアナログ入力信号が電源レールを300 mV以上超えないように注意してください。もし信号がこのレベルを超えると、内蔵ESD保護ダイオードが順方向バイアスとなりサブストレートに電流が流れ始めます。ダイオードが破損する事なしに導通可能な最大電流は10 mAです。これはチュートリアルMT-036に説明されているようにAD7091RのVINと電源レールとの間にペアのショットキー・ダイオードを接続する事により避けられます。

AD7091Rは2.5 Vリファレンスを内蔵しています。規定の性能を達成するためにREFIN/REFOUTピンを適切なデカップリングしてください。REFIN/REFOUT コンデンサの標準的な値は2.2 μFです。内蔵リファレンス電圧は外部からオーバードライブできます。

外部リファレンス電圧を使用する場合は、2.7 V ~ VDDの範囲をREFIN/REFOUTピンに接続する必要があります。レギュレータ・バイパス(REGCAP)デカップリング・コンデンサの標準的な値は1 μFです。

VDRIVE入力に印加される電圧によって、シリアル・インターフェースのロジック・レベル電圧が制御されます。このピンをAD7091Rのデジタル出力に接続されているロジック・ファミリーの電源電圧に接続してください。 VDRIVEは1.8 V ~VDDの範囲で設定できます。VDRIVE デカップリング・コンデンサの標準的な値は10 μFと100 nFの並列です。

ビジー表示機能が必要な場合、VDRIVEとSDOピンの間に100 kΩのプルアップ抵抗を接続してください。

AD7091Rのアナログ入力バッファとして使用されるAD8031はユニティゲイン・バッファの構成とします。帯域外ノイズを減らすためにオペアンプの出力段の後に1極RCフィルタを接続します。RCフィルタのカットオフ周波数を660 kHzに設定します。しかしシステムのスループット・レート仕様により、このパラメータは変わります。AD7091Rが最大のスループット・レートで動作しないシステムではフィルタ・カットオフ周波数を低くできます。アナログ信号入力の振幅とオフセットの大きさによっては、オペアンプAD8031で増幅、減衰、レベルシフトの回路を組み、入力信号振幅をADCのアナログ入力範囲に整合させる事ができます。

| Mode | IDD | IDRIVE | IAMP (µA) | Total Current (µA) | Total Power (mW) |

| Power Down | 550 nA | 36 nA |

766 | 767 | 2.3 |

| Static (Power On, Input Grounded, No Clock) | 21 µA | 81 nA | 766 | 787 | 2.4 |

| Operating (Power On, 10 kHz Input, 1 MSPS Sampling) | 368 µA |

406 µA |

766 | 1540 | 4.6 |

| Operating (Power On, Input Grounded, 1 MSPS Sampling) | 344 µA |

35 µA | 766 | 1145 | 3.4 |

| Operating (Power On, Input Grounded, 1 kSPS Sampling) | 57.8 µA | 18.9 µA | 766 | 843 | 2.5 |

サンプリング時、変換開始パルス幅= 20ns。 VDD = VDRIVE = 3 V。

図2と図3はそれぞれ回路の積分非直線性(INL)と微分非直線性(DNL)のグラフです。INLとDNLが±1 LSB以下になっている事に注目してください。

図4は周波数10 kHzのアナログ信号を入力し1 MSPSのレートで取り込んだ8192サンプルについて計算したFFTデータです。SNRは70.44dBFSです。

この回路は、大きな面積のグランドプレーンを持った多層PCボード(PCB)に構築する必要があります。最適な性能を得るには適切なレイアウト、接地、デカップリング技術を使用する必要があります(チュートリアルMT-031、チュートリアルMT-101とCN0247-Design Supportパッケージに示されているAD7091R 評価用ボード・レイアウトを参照)。この回路は、大きな面積のグランドプレーンを持った多層PCボード(PCB)に構築する必要があります。最適な性能を得るには適切なレイアウト、接地、デカップリング技術を使用する必要があります(チュートリアル AD7091RとAD8031の周辺部品の値はアプリケーションとセンサーの特定条件を満足するように変更する事ができます。たとえば、バッファはゲインやオフセットを与える回路に構成でき、RCフィルタのカットオフ周波数はサンプリング周波数と入力周波数に応じて変更可能です。

回路、ボード・レイアウト、部品表(BOM)など完全な技術文書パッケージが CN0247-Design Supportに載っております。

回路の評価とテスト

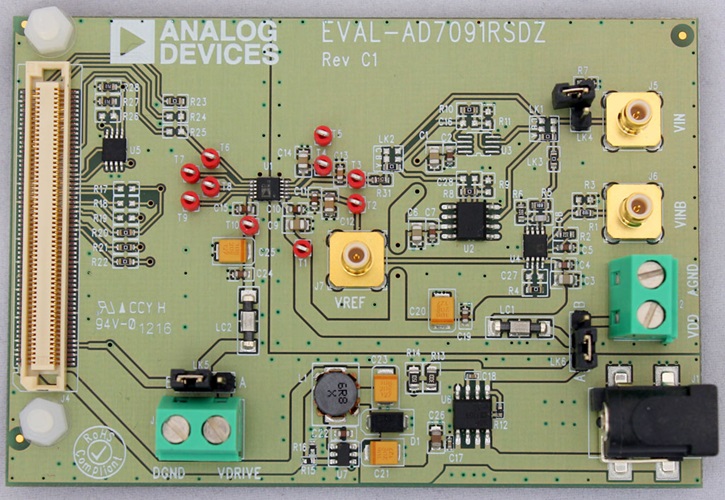

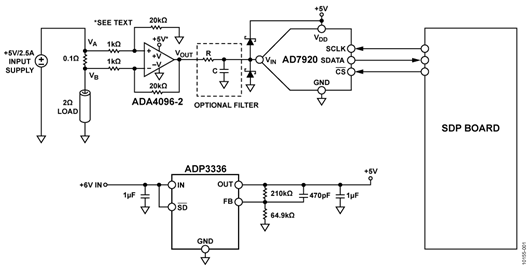

EVAL-AD7091RSDZ 評価用ボードはデバイスAD7091Rをこの回路ノートに記述されている回路で評価し、テストするために開発されました。回路の詳細とユーザー・インストラクションはEVAL-AD7091RSDZの技術文書に載っております。図5にテスト・セットアップの機能ブロック図を示します。

必要な装置

回路をテストするために、下記の装置が必要です。

- EVAL-AD7091RSDZ 評価用ボード(ソフトウェアと9 V DC用ACアダプタ電源を含む)

- EVAL-SDP-CB1Z システム・デモ用プラットフォーム・ボード

- 低歪み信号発生器(アジデント81150AあるいはAudio PrecisionのSystem Two 2322のような信号発生器)

- USB2.0ポート付きWindows® XP又はWindows Vista又はWindows 7(32ビット又は64ビット)対応のPC

- 電源:9 V DC 用ACアダプタ(評価用ボードに含まれている、50mAの外部3VDC電源)

セットアップ

任意のハードウェアを接続する前に、 EVAL-AD7091RSDZ評価用ボードのリンクが次の位置になっている事を確認してください:

- LK1:ポジションA(入力バッファとしてAD8031を選択する)

- LK2:ポジションA(J5で入力を入力バッファに接続する)

- LK5:ポジションA(外付けVDRIVE 源をイネーブルにする)

- LK6:ポジションB(外付けVDD源をイネーブルにする)

リンクを確認した後は評価用ボードの説明書に従ってハードウェアを接続、ソフトウェアをインストールしてください。

テスト

この回路ノートに含まれている各種テストを行う方法に関する詳しい説明は評価用ボードの説明書を参照してください。