AN-1485: ブレーク・ビフォア・メーク機能を備えたSPI 制御スイッチの外部配線によるマルチプレクサ構成の実現

はじめに

信号のスイッチングはエレクトロニクス・システムで重要な部分の1 つです。複数の信号によって柔軟性が生まれ、システム中で使用できるチャンネル数が多くなります。アプリケーションには多様なタイプがあり、各アプリケーションでスイッチングに対する要求が異なります。スイッチングを必要とするアプリケーションが非常に多いことから、ちょうど求められる機能を持つスイッチを見つけるのが難しい場合もあります。

このアプリケーション・ノートでは、アナログ・デバイセズのシリアル・ペリフェラル・インターフェース(SPI)制御スイッチのファミリに搭載されたブレーク・ビフォア・メーク(BBM)スイッチング機能について説明します。このBBMスイッチング機能を適切な外部配線と組み合わせて、特定のアプリケーションに必要なマルチプレクサ(MUX)構成を作成する方法を示します。また、外部配線を使用したスイッチの性能についての考慮事項についても説明します。

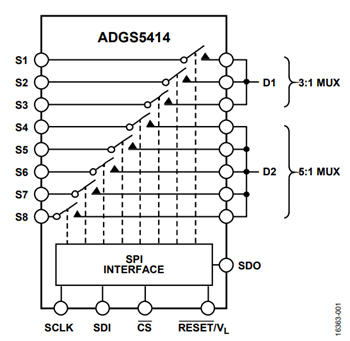

図1 に、ADGS5414 を外部配線で3:1 MUX と5:1 MUX に構成する例を示します。

SPI 制御スイッチ

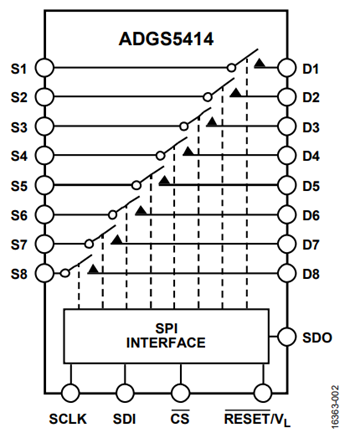

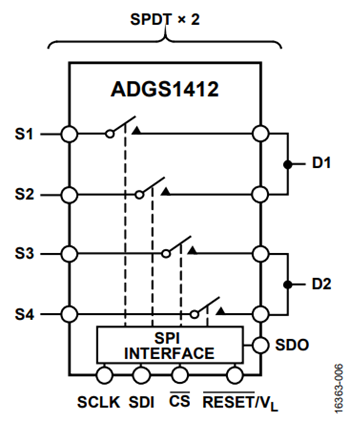

アナログ・デバイセズのSPI スイッチには、4 線式シリアル・インターフェースとエラー検出機能が組み込まれています。図2に、SPI スイッチの1 つであるADGS5414 の機能ブロック図を示します。図2 では、デバイスのSPI 部分を構成する4 本のピンを図示しています。これらのピンは、シリアル・クロック入力(SCLK)、シリアル・データ入力(SDI)、シリアル・データ出力(SDO)、チップ・セレクト(CS)です。RESET/VL はSPIブロックに電力を供給し、ハードウェア・リセットの実行に使用できます。

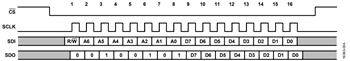

動作モードには、アドレス・モード、バースト・モード、デイジーチェーン・モードがあります。すべてのデバイスで、BBMスイッチング機能が確保されています。業界標準のSPI モード0およびSPI モード3 と互換性があります。シリアル・データはSCLK の立上がりエッジでデバイスに読み込まれ、SCLK の立下がりエッジで伝搬出力されます。最大50MHz のSCLK 周波数でデバイスと通信できます。SPI デバイスのデフォルト・モードはアドレス・モードです。このモードでは、CSによって分割される16 ビットのSPI コマンドで、デバイスのレジスタにアクセスできます。アドレス・モード・コマンドでは、R/Wビットの後に7 ビットのアドレスが続き、8 ビットのデータで終了します。図4 に、アドレス・モードの場合のSPI フレームを示します。

バースト・モード動作では、アドレス・モードと同じSPI コマンドを使用しますが、複数のSPI コマンドの実行の間でCSをローのままにできる点が異なります。

新しいSPI 制御ファミリでは、SPI インターフェースでプロトコルと通信のエラーを検出でき、過酷な環境でも信頼性の高い通信を実現できます。SPI インターフェースでは、3 つのエラーを検出できます。不正なSCLK カウント・エラー、無効な読出しと書込みアドレス・エラー、巡回冗長性チェック(CRC)エラーです。各エラーの検出機能は、エラー構成レジスタの対応するイネーブル・ビットを使用して有効または無効にできます。更に、エラー・フラグ・レジスタには、各エラーに対応するエラー・フラグ・ビットがあります。

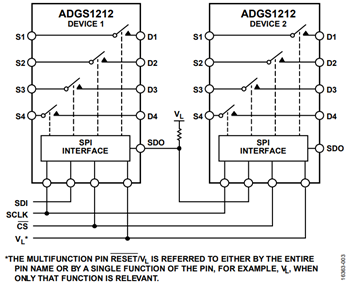

デイジーチェーン・モードは、SPI スイッチのもう1 つの重要な機能です。これにより、複数のデバイスを1 つのチェーンに接続できます。デイジーチェーン構成では、あるデバイスのSDOが、チェーン内の次のデバイスのSDI に接続され、その次のデバイスにも同様の接続が繰り返されます(図3 の2 個のADGS1212 デバイスを参照)。この構成では、4 本のデジタル・ラインのみで多数のSPI スイッチを制御できる利点があります。そのため、ボードの実装面積と設計の複雑さを低減できます。

BBM スイッチング

BBM スイッチングでは、あるスイッチを開いてから別のスイッチを閉じます。BBM スイッチングの機能は、アナログ・デバイセズのすべてのSPI スイッチで確保されています。あるスイッチを閉じて別のスイッチを開くSPI コマンドが発行された場合、開くよう指示されたスイッチが開いた後に、他方のスイッチが閉じます。

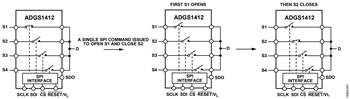

図7 に、外部配線を使用して4:1 MUX に構成されたADGS1412を示します。また、スイッチS1 を開いてスイッチS2 を閉じるように指示するSPI フレームが発行された場合の動作も示します。

ADGS1412 は、最初はS1 を閉じるように構成されているので、この入力の信号がドレイン(D)に出力されています。SPI コマンド0x0102 は、スイッチ・データ・レジスタ用のコマンドで、これが送信されるとS1 を開いてS2 を閉じます。BBM の定義に従い、S2 が閉じる前にS1 が開きます。この機能により、S1 とS2 への入力回路で短絡が発生しません。

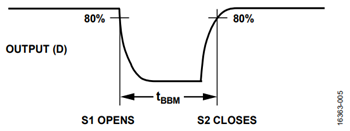

図5 に、S1 とS2 の電圧が等しいと仮定した場合の、このイベントのシーケンスの間の信号D を示します。

S1 が開くと、電圧が低下します。その後S2 が閉じ、S2 に印加されている信号がD に出現します。SPI 制御スイッチのデータシートに記載されているBBM 時間は、最初の信号が初期値の80%まで低下してからS2 が最大値の80%に到達するまでの時間です。各デバイスのBBMタイミングについて実施された試験の詳細については、対応するSPI 制御スイッチのデータシートを参照してください。

このBBM機能により、アプリケーションで必要とされるようなマルチプレクサとしてSPI スイッチを構成することが可能で、マルチプレクサの構成において高い柔軟性が得られます。プリント回路基板(PCB)上でユーザが目的に応じてソース・ピンやドレイン・ピンを接続しますが、適切な外部配線を適用する必要があります。図6 に、外部配線を使用したマルチプレクサに構成されたデバイスの例を示します。このケースでは、ADGS1412 が単極双投(SPDT) × 2 のソリューションとして構成されています。

性能に関する考慮事項

スイッチをマルチプレクサに構成する場合、データシートの仕様に変化が生じます。

デバイスの複数のドレインを互いに接続すると、各ドレインの容量が加算されるので、接続ポイントでの全体的な容量が増加します。この増加により、スイッチ・オフ時のドレイン容量CD(OFF)とスイッチ・オン時のドレイン容量CD(ON)は、マルチプレクサ構成で接続された場合には大きくなり、スイッチを介して伝搬する信号のバンド幅が低減します。この低減は、スイッチ・チャンネルの抵抗コンデンサ(RC)値が大きくなることに起因します。

また、ドレインが互いに接続されている場所でのリークが増えることも想定されます。このリークは、互いに接続されたドレイン・ピン間でリーク電流が加算されることによるものです。

最後に、互いに接続されたチャンネル間のクロストーク性能が低下することが予想されます。この性能低下は、PCB パターンを介してチャンネルが互いに物理的に接続されることにより発生します。

これらのトレードオフは想定範囲内で、相補型金属酸化膜半導体(CMOS)スイッチによるマルチプレクサではどれも同じトレードオフが発生します。

アナログ・デバイセズSPI スイッチのファミリ

アナログ・デバイセズSPI スイッチ・ファミリには、様々なアプリケーションに対して最適化された幅広いシリアル制御スイッチがあります。表1 に、ファミリの製品の代表品番、その構成、各デバイスの性能を最適化する方法を示します。表1 に示す全デバイスは、このアプリケーション・ノートで説明したBBM スイッチングで動作します。このため、外部配線によるマルチプレクサ構成が可能です。

| Generic | Configuration | Performance Optimization | Robustness | Characterized Supply Voltages (V) |

| ADGS1612 | SPST × 4 | 1 Ω on resistance (RON), 0.2 Ω on resistance flatness (RFLAT (ON)) | Not applicable | ±5/+12/+5/+3.3 |

| ADGS1412 | SPST × 4 | 1.5 Ω RON, 0.3 Ω RFLAT (ON) | Not applicable | ±15/±5/+12 |

| ADGS1212 | SPST × 4 | −0.9 pC charge injection (QINJ) and 2.6 pF on switch capacitance CD (ON) and CS (ON) | Not applicable | ±15/+12 |

| ADGS5412 | SPST × 4 | 9.8 Ω RON | Guaranteed latch-up immunity and 8 kV human body model (HBM) electrostatic discharge (ESD) rating | ±15/±20/+12/+36 |

| ADGS5414 | SPST × 8 | 13.5 Ω RON | Guaranteed latch-up immunity and 8 kV HBM ESD rating | ±15/±20/+12/+36 |

まとめ

アナログ・デバイセズのSPI スイッチは、信頼性の高いインターフェース・エラー検出機能とデイジーチェーン・モードを備えた4 線式シリアル・インターフェースを搭載しています。このファミリに属する各SPI スイッチでは、BBM スイッチング動作が確実にサポートされています。この機能により、スイッチをエンド・アプリケーションで必要とされるマルチプレクサとして構成する際の柔軟性が向上します。デバイスの外部配線がデバイスの仕様にどう影響するかは、考慮する必要があります。こうした性能のトレードオフは、他のCMOS マルチプレクサ・デバイスで見られるトレードオフと同様です。