AN-1397: ADM3065E 50Mbps RS-485 トランシーバを使用したEnDat モータ・コントロール・エンコーダ・アプリケーション

はじめに

モータの位置と角度のエンコーダは、アブソリュート・エンコーダとしても知られ、サーボ機構駆動装置、ロボティクス、工作機械、エレベータなどのシステムで広く使用されています。図1 にモータ・コントロールのシグナル・チェーンを示します。ここでは、交流モータのクローズドループ制御向けにスレーブ側のアブソリュート・エンコーダ(ABS エンコーダ)とマスタ側の産業用サーボ機構駆動装置間をインターフェースするために、RS-485 トランシーバを使用しています。ABS エンコーダは機械的な動き(位置と方向)を電気信号に変換し、これがサーボ機構駆動装置にフィードバックされます。サーボ機構駆動装置は、このエンコーダの情報に基づき交流モータのインテリジェント制御を行います。サーボ機構駆動装置とABS エンコーダ間のRS-485 通信リンクでは、通常、最大16MHz の高データ・レートと短い伝搬遅延時間特性が求められます。RS-485 のケーブル長は通常、最長で50m ですが、場合によっては150m まで延長が可能です。産業界の過酷な環境下では、露出したケーブルとRS-485 コネクタは、国際電気標準会議(IEC)61000-4-2 に規定される静電放電(ESD)のような有害な電磁電流(EMC)にさらされる場合があります。

EnDat エンコーダ向けRS-485

このアプリケーション・ノートでは、アナログ・デバイセズのADM3065E 50Mbps(25MHz)RS-485 トランシーバを使用した、EnDat モータ・コントロール・エンコーダ・アプリケーションの利点について説明します。ADM3065E トランシーバは、モータ駆動やエンコーダに対する過酷な環境下でも高い信頼性で動作し、更にノイズ耐性とIEC 61000-4-2 ESD 耐性を主要な特長として保持するよう設計されています。ADM3065E のタイミング仕様、とりわけ、ドライバとレシーバ間の伝搬遅延が短いという特長により、産業用のサーボ機構駆動装置からABS エンコーダに至るシステム設計の複雑さを軽減できます。この低伝搬遅延は、EnDat エンコーダ用の高い周波数(16MHz)に限らず、全てのシステム・クロック周波数においてシステム設計の複雑さを軽減します。このアプリケーション・ノートでは、モータ・コントロール・アプリケーションの主な利点を、関連するアプリケーション回路やタイミング測定を用いて説明します。

エンコーダ向けRS-485 の堅牢性

モータ・コントロール・エンコーダ・アプリケーションは、データ通信にとっては厳しい環境です。電気的ノイズや長いケーブル長によって、ABS エンコーダからサーボ機構駆動装置までのRS-485 を用いた信号伝送の安定性が影響を受けるためです。アナログ・デバイセズのRS-485 トランシーバには、こうした厳しい環境でも信頼性の高い動作を可能とし、ノイズ耐性や堅牢性を付加した設計がなされています。

ノイズ耐性

RS-485 の信号は平衡接続、差動型で、本質的にノイズ耐性があります。システムのノイズは、一組のRS-485 のツイスト・ペア・ケーブルの両方のワイヤに均等に結合します。一方の信号は他方と反転した信号を放射し、電磁界は相互に打ち消し合ってRS-485 バスと結合します。このため、システムの電磁干渉(EMI)が低減します。また、ADM3065E の駆動強度は2.1V に増強されているので、通信時のS/N 比(SNR)が改善されます。

RS-485 レシーバのヒステリシスによってもノイズ耐性は向上します。これについては、増強したRS-485 トランシーバ性能のセクションで説明します。アナログ・デバイセズのiCoupler®技術を付加すれば、ノイズ耐性が更に向上します。

増強したRS-485 トランシーバ性能

TIA/EIA-845-A RS-485 規格では、RS-485 トランシーバを安定させる手段を実装するか、レシーバ・デバイスに発振条件を実装することを推奨しています。レシーバのヒステリシスは、レシーバの安定性を改善するのに有効で、ノイズ耐性向上の手段となります。これは、過酷な産業用モータ・コントロール環境での長いケーブル配線には特に重要です。

ADM3065E のデータシートでは、標準的なレシーバ・ヒステリシス(VHYS)30mV、レシーバの差動入力スレッショールド電圧(VTH)−200mV~−30mV が仕様規定されています。

VTH はレシーバの出力電圧(VOL とVOH)をハイからロー、ローからハイに変化させるための閾値です。VHYS は本質的に、ハイからローのVTH(図2 の左側)とローからハイのVTH(図2 の右側)の差です。VHYS には、VTH 近傍のノイズがレシーバ出力でのロジック・ハイからローへの疑似遷移の原因とならないようにする効果があります。

ノイズ耐性向上のための信号絶縁の付加

ADuM141D を使用して、容易にADM3065E に信号絶縁を付加できます。ADuM141D は、アナログ・デバイセズのiCoupler®技術をベースにした4 チャンネルのデジタル・アイソレータです。ADuM141D は最大150Mbps のデータ・レートで動作することができるので、50Mbps のADM3065E RS-485 トランシーバを使用した動作に最適です(図3 参照)。

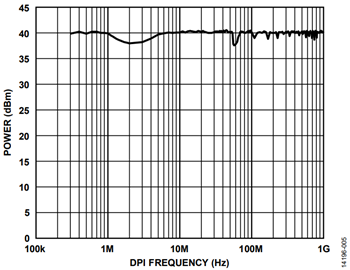

ダイレクト・パワー・インジェクション(DPI)は、電源や入力ピンに混入するノイズを除去する部品の性能を測定します。ADM141D で使用した絶縁技術はDPI IEC 62132-4 規格で試験済みです。ADuM141D では、VDD1 とVDD2 のいずれかの電源ピンに容量結合した高電力ノイズ源を使用して、DPI IEC 62132-4 規格に準拠する試験を実施しました。ノイズ源は、300kHz~1GHzの周波数帯域で掃引しています。DPI IEC 62132-4 の試験中、ADuM141D のVIA ピンにクロック信号が入力され、そのクロック・データのエラーがモニタされます(ループバック・テスト・モード)。信号のビット幅の変化量が±10%を超えると、不合格と見なされます。図4 に、ADuM141D VDD1 電源ピンに接続した6.8 nF のコンデンサを通じてDPI ノイズ源を挿入した試験の構成例を示します。

図5 に、ノイズ・パワー(dBm)とDPI 周波数(Hz)に関するADuM141D の不合格ポイントを表す代表的な性能プロットを示します。IEC 62132-4 規格に適合するADuM141D の性能を、市場で入手可能な他のアイソレータと比較して評価しました。ADuM141D のノイズ耐性の性能は他の類似製品よりも優れています。ADuM141D は広い周波数範囲にわたり優れた性能を維持しますが、その他のアイソレーション製品では、200MHz~700MHz の周波数帯域でビット・エラーが発生します(図5 参照)。

堅牢性と信頼性

ADM3065E は最高+125°C の周辺温度でも高信頼動作する高温性能を可能とし、3.0V~5.5V の広い電源動作範囲でRS-485 の性能を強化します。これにより、差動電力が要求されるエンコーダやモータ駆動に対する信頼のおける柔軟なソリューションを提供できます。

バス・アイドル、オープン・サーキット、短絡のフェイルセーフ

ADM3065E はフェイルセーフ機能を備えたRS-485 レシーバです。この機能により、ABS エンコーダからサーボ機構駆動装置へのRS-485 インターフェースのケーブルの切断を検知することができます。

ADM3065E は確実なフェイルセーフ機能を持ち、−7V~+12V のレシーバのコモン・モード入力の全範囲で、バス・アイドル、オープン・サーキット、短絡に対してロジック・ハイのレシーバ出力機能を提供します。図6 に、レシーバ入力のスレッショルド電圧とレシーバ出力のロジックの変換基準について、ADM3065E と一般のRS-485 トランシーバとの比較を示します。ADM3065E はレシーバ入力が−30mV のスレッショルド電圧を超えるとロジック・ハイを出力しますが、一般のRS-485 では+200mVを超えたときにロジック・ハイを出力します。

オープン・サーキット・フェイルセーフ機能により、RS-485 のA ピンとB ピンが切断され、終端抵抗や他のノードがない場合には、ADM3065E レシーバ出力が確実にハイになります。この機能は、すべてのアナログ・デバイセズRS-485 トランシーバに内蔵されています。ADM3065E のA ピンには、内部プルアップ抵抗があります。A ピンが切断されているか、またはフロート状態にある場合、このプルアップ抵抗はA ピンを−30mV よりも高い電圧にプルアップします。ADM3065E のB ピンには、プルダウン抵抗があります。B ピンが断線するかフローティングになった場合、このプルダウン抵抗がB ピンを−200mV より低い電位に引き下げます。このシナリオでは、A ピンの電圧はB ピンの電圧よりも高いので、バス差動電圧がハイとなり、レシーバの出力は常にロジック・ハイになります。

短絡フェイルセーフ機能により、2 つのノードが反対のレベルにバスを駆動する場合、またはバス・ラインの配線が互いに短絡している場合、ADM3065E のレシーバ出力が確実にロジック・ハイになります。

バス・アイドル・フェイルセーフは、このセクションで説明したバス・オープン・サーキットやバス短絡フェイルセーフより複雑で、どのノードもRS-485 バスに信号を駆動していない場合にADM3065E レシーバ出力をロジック・ハイにします。このフェイルセーフを機能させるには2 つの方法があります。最初の方法では、オフセットのレシーバ閾値(TIA/EIA-845-A RS-485 規格の+200mV ではなく−30mV)を備えたフェイルセーフRS-485 トランシーバを使用します。バス・アイドルのフェイルセーフ機能を備えたアナログ・デバイセズのRS-485 トランシーバは、短絡のフェイルセーフ機能も備えていています。2 番目の方法では、バスでプルアップ抵抗とプルダウン抵抗を使用して、差動電圧を最小限に抑えます。この方法は、アクティブ終端または電源終端とも呼ばれます。電源電圧、および終端抵抗、レシーバのインピーダンスなどのバス負荷に基づいて、必要な抵抗値を計算します。

IEC 61000-4-2 ESD 性能

エンコーダからモータ・ドライブ間の露出したRS-485 コネクタやケーブルに対するESD は、一般的なシステムの故障要因になります。可変速駆動システムのEMC 耐性に関するシステム・レベルのIEC 61800-3 規格は、最小でもIEC 61000-4-2 規格に定める±4kV(接触放電)/±8kV(気中放電)のESD 保護を求めています。ADM3065E ではこれを上回る、±12kV(接触放電)/±12kV(気中放電)のIEC 61000-4-2 規格のESD 保護を実現しています。

図7 では、人体モデル(HBM)ESD 8kV の波形とIEC 61000-4-2規格の8kV の接触放電電流の波形を比較しています。図7 より、この2 つの規格がお互いに異なる波形とピーク電流を仕様規定していることがわかります。IEC 61000-4-2 の8kV パルスに関連するピーク電流は30A で、一方、これに相当するHBM ESD のピーク電流は1/5 未満の5.33A になっています。その他の違いは、初期電圧スパイクの立上がり時間にあります。HBM ESD 波形の10ns と比較すると、IEC 61000-4-2 ESD では、立上がり時間が1ns と極めて短くなっています。IEC ESD 波形に関連付けられた電力量は、HBM ESD 波形の電力量よりも非常に大きくなっています。HBM ESD 規格では、被試験装置(EUT)に対し、正負の放電をそれぞれ3 回行うことになっているのに対し、IEC ESD規格では正負それぞれ10 回の放電試験を行うことが要求されています。

IEC 61000-4-2 のESD 定格に対応するADM3065E は、様々なレベルのHBM ESD 保護機能を備えた他のRS-485 トランシーバに比べ、過酷な環境での動作に適しています。

グリッチなしのパワーアップ/パワーダウン

ADM3065E には、広範囲でグリッチなしのパワーアップ/パワーダウン(ホット・スワップ)保護機能が備わっています。

回路基板を電源がオンの(つまりホットの)バックプレーンに挿入すると、データ・バスへの差動外乱により、データ・エラーが発生することがあります。この期間中、プロセッサのロジック出力ドライバは高インピーダンスになり、DE とRS-485トランシーバのDE とRE入力を定義したロジック・レベルに駆動できなくなります。高インピーダンス状態のプロセッサ・ロジック・ドライバからの最大±10μA のリーク電流によって、標準的な相補型金属酸化物半導体(CMOS)はトランシーバへの入力を誤ったロジック・レベルにドリフトしてしまう可能性があります。更に、回路基板の寄生容量によって、VCC ピンまたはGND ピンがイネーブル入力と結合してしまう場合もあります。このため、ホット・スワップ機能がないと、トランシーバのドライバまたはレシーバが間違ってイネーブルになることがあります。VCC の電源電圧が上昇した場合、内部のプルダウン回路がDE ピンをロジック・ローに、REピンをロジック・ハイに保ちます。初期のパワーアップ・シーケンスの後、プルダウン回路はトランスペアレントになり、ホット・スワップは許容入力値にリセットされます。

RS-485 の優れたタイミング性能

信号レート

ADM3065E はBiSS、EnDat 2.2、HIPERFACE DSL®のエンコーダ規格で求められている高データ・レートに対応しています。シリアル同期インターフェース(SSI)のようなRS-422 トランシーバを使用するエンコーダ規格に対応して、ADM4168E トランシーバでは低データ・レートでも高データ・レートでも信頼性の高いソリューションを提供します。表1 は、記載されたエンコーダ規格に対する半2 重および全2 重のいくつかのオプションを示すものです。

伝搬遅延

ADM3065E を使用して、システムのデータ伝送遅延の影響を抑制できます。ADM3065E のタイミング仕様、とりわけ、ドライバとレシーバ間の伝搬遅延が短いという特長により、産業用のサーボ機構駆動装置からABS エンコーダに至るシステム設計の複雑さを軽減できます。この低伝搬遅延は全てのシステム・クロック周波数に対する設計の複雑さを軽減するもので、高い周波数(16MHz)に限定されるわけではありません。

表1. モータ・コントロール・アブソリュート・エンコーダ・インターフェース対応のアナログ・デバイセズのトランシーバのソリューション

| Encoder Standard | Physical Layer | Data Rate (MHz) | High Data Rate RS-485 Transceiver Options | Low Data Rate RS-485 Transceiver Options |

| EnDat 2.2 | RS-485 | 0.1 to 16 | ADM3065E, ADM3066E | ADM3061E, ADM3062E |

| BiSS | RS-422 | 0.08 to 10 | ADM4168E, ADM3067E | ADM4168E |

| HIPERFACE DSL | RS-485 | 4.69 | ADM3065E, ADM3066E | ADM3061E, ADM3062E |

| SSI | RS-422 | 2 | ADM4168E, ADM3067E | ADM4168E |

| EnDat 2.1 | RS-485 | 0.1 to 2 | ADM3065E, ADM3066E | ADM3061E, ADM3062E |

EnDat エンコーダ・インターフェース

ロータリ・エンコーダは産業用オートメーション・システムで幅広く使用されています。このタイプのエンコーダは一般に電気機械で使用されており、エンコーダは回転シャフトに接続され、制御システムにフィードバックします。エンコーダの主要目的は角度位置と角速度の測定ですが、システム診断やパラメータ設定など、その他の機能もよく利用されています。このセクションでは、エンコーダとコントローラ間のインターフェースのマスタ側の実装と試験について説明します。

通信プロトコル

エンコーダ(スレーブ)とコントローラ(マスタ)との通信はデジタル双方向で、リアルタイム制御システムで動作できる速度に加え、工業環境下で機能する堅牢性を備えています。

通信プロトコルにはオープン・ソースのものもありますが、独自のプロトコルを選択する駆動装置メーカーもあります。合計20 種類以上のプロトコルが存在します。主要プロトコルとして、EnDat とBiSS の2 つが挙げられます。

両者に相違はありますが、エンコーダの通信プロトコルの実装に関しては共通点があります。プロトコルのインターフェースはシリアル双方向で、RS-422 またはRS-485 のいずれの電気的仕様も満たしています。リンク間のデータ伝送はマスタが供給するクロックに同期しています。いくつかのデータの種類(例えば、位置の値、パラメータ、診断結果など)がリンク間で交換されます。この交換ではマスタがスレーブに送ったコマンドに応じてデータの種類が選択されます。

ハードウェア・レイヤには共通性がありますが、各プロトコルを実行するのに必要なソフトウェアには独自性があります。通信スタックと必要なアプリケーション・コードは、共にプロトコルに固有のものです。

このアプリケーション・ノートでは、図8 に示すEnDat 2.2 インターフェースの、マスタ側のハードウェアおよびソフトウェア実装について説明します。

遅延による影響

産業用のアプリケーションによっては、コントローラとエンコーダが物理的に100m以上離れている場合があります。この距離を最大16MHz の通信速度で接続すれば、システムが伝送遅延の影響を受けるのは明らかです。

遅延は2 種類に区分できます。まず、ケーブルの伝送遅延(tCABLE)が生じます。次に、トランシーバの伝搬遅延(tTRX)が生じます。総遅延(tDELAY)はこの2 つの和です。

tDELAY = tCABLE + tTRX

光速とケーブルの誘電率とでケーブルの遅延が求まり、標準的な値は6ns/m~10ns/m です。短いケーブルの場合、この遅延はほとんど無視できますが、ケーブルが長くなるほど問題になります。

マスタがクロックを出力すると、このクロックはケーブルを伝搬し、エンコーダではケーブル長分だけ遅延します。スレーブはデータを送信し、そのデータはこのクロックを使用してケーブルを戻ります。すなわち、マスタが受信するデータはケーブル長の2 倍の長さ分だけ遅延することになります。

遅延の2 つ目の原因はトランシーバの伝搬遅延です。マスタ側とスレーブ側の双方にトランシーバがあり、データはケーブルを往復すると仮定すると、信号は4 個のトランシーバ分だけ遅延することになります。このようにケーブル長とトランシーバ数を考えると、伝搬遅延が考慮すべき重要なパラメータである理由がわかります。

ケーブル長は、マスタとスレーブの物理的な距離で決まるため、変更することはできません。しかし、トランシーバの選択により伝搬遅延は変えることができます。

遅延補償

tDELAY がクロックの半周期を超えると、マスタとスレーブ間の通信は破綻します。この場合、設計者には次の選択肢があります。

- データ・レートを下げる

- トランシーバの伝搬遅延を短くする

- マスタ側に遅延補償を導入する

3 番目の選択肢はケーブル遅延とトランシーバ遅延の双方を補償するもので、ケーブルが長くてもシステムが高いクロック・レートで動作できるようにする有効な手段です。選択肢3 を採用した場合の欠点は、遅延補償によりシステムが複雑化し、マスタが補償に対応できない場合があることです。

遅延補償を採用できないシステムやケーブルが短いシステムでは、伝搬遅延の小さいトランシーバを使用することが有効なのは明らかです。伝搬遅延が小さいと、システムに遅延補償を導入しなくても高いクロック・レートが可能となります。

伝搬遅延が小さいことの利点は、高データ・レートだけにあるわけではありません。遅延補償のないシステムは、通常低いデータ・レートで動作しますが、これが伝搬遅延が小さいことのもう1 つ利点となっています。

マスタへの実装

プロトコルに関わらず、マスタへの実装にはシリアル・ポートと通信スタックが必要です。エンコーダのプロトコルは、シリアル・ペリフェラル・インターフェース(SPI)またはユニバーサル非同期レシーバ/トランスミッタ(UART)のような標準ポートには対応していないため、汎用のマイクロコントローラで用いられる周辺機器は使用できません。代わりに、フィールド・プログラマブル・ゲート・アレイ(FPGA)を使用してエンコーダのインターフェースを実装するのが一般的です。FPGAのプログラマブル・ロジックによって、ハードウェアに専用の通信ポートを実装し、遅延補償のような先進機能をサポートすることができます。通信スタックはソフトウェア実装に適しており、通例、プロセッサ上で実行されます。

FPGA 手法は柔軟性が高く、アプリケーションに適合可能ですが、不利な点もあります。まず、FPGA はプロセッサに比べて高価です。次に、FPGA は電力を著しく消費します。最後に、カスタムFPGA の設計に要する開発期間が長く、市場投入までの時間を考慮すると許容できないことがあります。

このアプリケーション・ノートで説明するEnDat インターフェースは、モータ・コントロール・ドライブを目的とした標準的なプロセッサADSP-CM408CSWZ-AF 上に実装されます。ADSP-CM408CSWZ-AF は、パルス幅変調器(PWM)タイマー、A/D コンバータ(ADC)、SINC フィルタなどのモータ・コントロール用周辺機器のほか、非常に柔軟性に富むシリアル・ポート(SPORT)を備えています。これらのSPORT は、EnDat やBiSS のようなエンコーダ・プロトコルを含む多くのプロトコルをエミュレートできます。

ADSP-CM408CSWZ-AF の充実した周辺機器セットのおかげで、エンコーダを同じデバイスにインターフェースさせるだけでなく、先進のモータ・コントロールを実行することが可能です。つまり、FPGA の必要性がなくなります。FPGA 用のハードウェア記述言語(HDL)のコード開発の必要がなくなり、C コードと標準的なプロセッサ開発ツールに焦点を絞ることができます。また、PCB の面積を節約でき、プロセッサの消費電力もFPGAに比べ一般に小さくなります。

テスト・セットアップ

EnDat 2.2 のアプリケーション構成を図9 に示します。EnDat スレーブはKollmorgen®製の標準的なサーボ機構モータ(AKM22)で、EnDat エンコーダ(ENC1113)がシャフトにマウントされています。3 対の線(データ、クロック、電力線)がエンコーダとトランシーバ・ボードを結んでいます。EnDat PHY にはトランシーバ(ADM3065E)が2 つと、エンコーダ用電源があります。トランシーバの一方はクロック用に使用し、クロックは常にマスタから供給されるので、このデータ・フローは単方向となります。もう一方のトランシーバはデータ・ラインに使用します。データ・ラインは半二重で、データ・フローは双方向です。

EnDat マスタはADSP-CM408CSWZ-AF で構成され、標準的な周辺機器とソフトウェアを使用しています。送信ポートと受信ポートは共に、柔軟性の高いSPORT を実装しています。これらのSPORT は通信に関するあらゆるタスクを処理します。すなわち、データの入出力、EnDat スレーブ向けクロック信号の発生、トランシーバへのコントロール信号の送信などを行います。

遅延による影響のセクションで説明したように、ケーブルが長いと遅延が生じ、スレーブから受信したデータはマスタが供給したクロックと位相がずれることになります。このケーブル遅延を補償する効果的な手段は、受信SPORT で使用するクロックの位相をシフトすることです(図9 参照)。この構成が機能するには、クロックの位相シフト量をシステムの総遅延量と一致させる必要があります。

ダイレクト・メモリ・アクセス(DMA)を使用して、データはADSP-CM408CSWZ-AF の周辺機器と通信スタックの間で伝送されます。これにより、通信に関係するソフトウェア・オーバーヘッドを最小限に抑制します。通信スタックは、シーケンス制御、エンコーダへのコマンド送信、エンコーダからのデータ受信などのタスクを処理します。エンコーダからのデータはモータ・コントロール・アプリケーションに送られ、やはりADSPCM408CSWZ-AF 上で実行されます。

EnDat プロトコル

EnDat プロトコルは様々な長さの多種にわたるフレームで構成されていますが、これらのフレームはすべて同じシーケンスに基づいています。まず、マスタはスレーブにコマンドを発行します。次に、スレーブはこのコマンドを処理し、必要な計算を実行します。最後に、スレーブは結果をマスタに送信します。図10 にマスタとスレーブ間の通信例を示します。

図10 では、トランシーバのクロック(Tx CLK)は、ADSPCM408CSWZ-AF で生成された送信クロックです。これはエンコーダに伝達されるクロックですが、ケーブル長やその他のシステムの遅延が原因で、エンコーダからのデータはTx CLKとは位相がずれてADSP-CM408CSWZ-AFに戻ることになります。この伝送遅延tDELAY を補償するため、ADSP-CM408CSWZ-AF でも受信クロック(Rx CLK)信号を出力します。これは、Tx CLKよりtDELAY だけ遅延します。Rx CLK とスレーブから受信したデータの位相を揃えることが、伝送遅延を補償する有効な手段となります。

ADSP-CM408CSWZ-AF からのクロック信号は連続的ですが、EnDat プロトコルでは、クロックは通信中のみエンコーダに印加されるように仕様規定されています。これ以外の時間は、クロック・ラインはハイに保たれている必要があります。このクロック信号を処理するために、クロック・イネーブル信号CLKEN がADM3065E のデータ・イネーブル・ピンに供給されます。CLK EN はADSP-CM408CSWZ-AF で生成され、送信クロックと同期しています。エンコーダはクロック信号ENC CLK を参照します。

ちょうどクロックの2 周期分の時間(2T)が経過すると、マスタはトランシーバ・データとしてコマンドをクロックに同期して出力し始めます。コマンドは6 ビット長で2 ビット分の0 が続きます。データ・トランシーバを通過するデータの方向を制御するため、ADSP-CM408CSWZ-AF は送信の間、Tx EN とRx ENのビットをいずれもハイにセットします。この信号がADM3065E の受信イネーブル(RE)ピンとデータ・イネーブル(DE)ピンに供給されます。ADM3065E は送信または受信モードのいずれかに保たれ、無効化されることはありません。TxモードとRx モードとの切替えは短時間の遅延で可能ですが、ディスエーブル・モードからイネーブル・モードへの切替えにはこれよりかなり長い時間を要します。

コマンドの送信後、スレーブは応答の準備をします。応答準備完了に要する時間は、コマンドの種類とエンコーダの種類で決まります。

このため、システムは待ち状態に入り、マスタはクロックを印加し続けますが、データ・ラインは不通となっています。スレーブの応答準備ができると、データ・ライン上でRx DATA はハイになり、その後直ちに応答が送信されます。n ビットの応答を受信後、マスタはCLK EN 信号をローにセットしてクロックを止めます。同時に、ENC CLK 信号はハイになります。

既述のとおり、データ・フローは半二重で、連結したデータ・ライン上のトラフィックはENC DATA として示されています。

図10 では、Tx CLK とRx DATA は伝送遅延のために位相がずれています。Rx CLKをtDELAYだけ遅延させて、受信クロックとRxDATA の位相を合わせることができます。

同期

モータ・コントロール・アプリケーションとエンコーダ・インターフェースを同じデバイスで実行させる利点の1 つは、正確に同期できることです。モータ・コントロール・ループでは、電流測定と位置のフィードバックを、パワー・インバータに印加するPWMパターンと同期させることが求められます。ADSPCM408CSWZ-AF では、図11 に示すように、トリガとDMAを組み合わせることで同期を実現しています。新たなPWM の周期が始まると、PWMのタイマーが同期パルスPWM_SYNC を生成します。このパルスが電流測定(図示していません)をトリガし、また、メモリから送信ポートへのデータのDMA転送をトリガします。このデータはエンコーダへのコマンドで、例えば、send position という命令です。

エンコーダがデータをマスタに返送する準備ができると、受信ポートがデータを取得し、DMA が結果をメモリに転送します。割込み信号IRQ が通信スタックに対し、データ処理の用意ができていることを伝えます。この処理ではソフトウェアの介入がないので、効率的な実装を行うことができます。

試験結果

図12 と図13 にこのアプリケーション・ノートで説明したEnDatシステムの試験結果を示します。試験で用いたクロック周波数は8MHz で、遅延補償を受信クロックの位相シフトで行っています。

図12 において、最下部の信号はEnDat マスタからのコマンドです。ここで示すコマンドはsend position で、2 ビットの0、6 ビットの1、2 ビットの0 で構成されています。合計10 ビット長のコマンドです。エンコーダからの応答は上から3 番目の信号です。この信号はADM3065E のレシーバ出力ピンRO で計測しており、そのため、シングル・エンドです。連結されたデータ・ラインは上から2 番目の信号です。これはADM3065E のA ピンとB ピンの差を計測したもので、信号は差動信号です。最後に、最上部の信号がエンコーダに印加したクロックです。

図13 に、送受信中のADM3065Eのコントロール・ラインを示します。最下部の信号は、トランシーバ処理データのデータ・イネーブルとレシーブ・イネーブルの信号を示します。ローは送信を示し、ハイは受信を示します。上から3 番目の信号はトランシーバ処理クロックのデータ・イネーブル信号を示します。信号がハイの場合、エンコーダ・クロック信号がエンコーダに印加されます。マスタとスレーブのデータ信号は連結されたデータ・ライン上の信号です。エンコーダからの出力データがADSP-CM408CSWZ-AF で受信された後、割込み信号が生成され、EnDat スタックが実行されます。