AN-1359: 単電源システムで高精度のAD5761R バイポーラDAC を採用するためにADP5070 を使用した低ノイズで両電源のソリューション

はじめに

このアプリケーション・ノートでは、デュアル(バイポーラ)電源を必要とする電源コンポーネントに単一ユニポーラ電源を用いる方法について説明します。バイポーラD/A コンバータ(DAC)であるAD5761R は、バイポーラ出力電圧範囲を実現するために両電源を必要とします。このアプリケーション・ノートで示す例では、ADP5070 DC/DC スイッチング・レギュレータをADP7142 およびADP7182 相補型金属酸化物半導体(CMOS)低ドロップアウト(LDO)リニア・レギュレータ、LC フィルタ、および抵抗分圧器と組み合わせて使用し、5V 単電圧電源から両電源を生成してAD5761R に給電します。

5V 電源とADP5070、ADP7142、ADP7182 やLC フィルタの組み合わせを共用することで、ユニポーラおよびバイポーラの電圧範囲を出力するDAC のための電源ソリューションを実現します。このソリューションのノイズ性能は、デュアル・ベンチ電源によって給電するDAC のノイズ性能と同等です。

このアプリケーション・ノートに記載されている電力スペクトル分析、電圧出力ノイズ、AC 性能データは、このソリューションの性能を裏付けています。

システムでどのテストを実行するかによって、推奨電源の構成は異なる結果をもたらします。例えば、ADP5070 電源と追加のLCフィルタを組み合わせた構成は、DACの内部リファレンスを使用した場合に10Hz~10kHz のスペクトル・ノイズを低減するのに最適です。それに対して、外部電源は、外部リファレンスを使用したスペクトル分析で最高の結果をもたらします。外部電源を用いて収集した結果を、全ての電源構成のベースライン測定として用いました。周波数帯域幅(10kHz~10MHz)が高い場合、CMOS LDO リニア・レギュレータをADP5070 電源に追加すると、最高のスペクトル・ノイズ性能が得られます。LCフィルタとLDO を組み合わせた構成は、ADP5070 からのスイッチング・ノイズを低減するために用いられているもので、この構成でのDAC から得られた出力スペクトルは、外部電源構成に匹敵するものです。

システムのノイズに対する感度によって、回路においてノイズを許容可能なレベルまで低減するのに必要な量が決まります。AD5761R に備わっているノイズ除去機能により、0.1Hz~10Hzの出力ノイズ測定間には大きな違いは見られません。LDO を追加することで、AD5761R の出力ノイズは大幅に低減し、ベースライン測定に匹敵する性能が得られます。

AC 性能テストでは、AD5761R はここに示した全ての電源構成の下でデータシートの仕様範囲内で動作します。

AD5761R は、出力アンプ、リファレンス・バッファ、温度係数が最大5ppm/ºC の内部リファレンスを統合した16 ビットDAC です。AD5761R は、最大30V のユニポーラ電源、または−16.5V~0V(VSS)および4.75V~16.5V(VDD)のバイポーラ電源で動作します。AD5761R は、8 つのプログラマブル出力範囲、35nV/√Hz のノイズ、選択した範囲で7.5μs のセトリング・タイムが可能です。

ADR4525 は2.5V の電圧リファレンスであり、このアプリケーション・ノートで説明しているテスト全般において、超低ノイズ電圧リファレンスを必要とするアプリケーションに対応するための外部リファレンスとして使用されています。

ADP5070 は、調整された正側レールと負側レールを個別に生成するデュアル高性能DC/DC レギュレータです。2.85V~15V の入力電圧範囲により、様々なアプリケーションをサポートできます。両方のレギュレータに内蔵されたメイン・スイッチにより、最大+39V の調整可能な正の出力電圧に加え、入力電圧より−39Vまで低い負の出力電圧を生成できます。ADP5070 は、ピン選択により1.2MHz/2.4MHz のスイッチング周波数で動作します。更に、レギュレータには、電磁干渉(EMI)を低減するための金属酸化膜半導体電界効果トランジスタ(MOSFET)ドライバ段のスルー・レート制御回路が組み込まれています。

ADP7142 は、2.7V~40V で動作し、最大200mA の電流を出力するLDO リニア・レギュレータです。この入力電圧の高いLDOリニア・レギュレータは、40V~1.2V のレールを駆動する高性能アナログ回路やミックスド・シグナル回路を調整するのに最適です。このデバイスは専用のアーキテクチャを使用して、高い電源電圧変動除去と低ノイズを実現し、優れたライン過渡応答と負荷過渡応答を実現します。ADP7142 レギュレータの出力ノイズは、5V 以下の場合11μV rms で、5V オプションの出力電圧を15V に調整可能です。

ADP7182 は、−2.7V~−28V で動作し、最大−200mA の電流を出力するLDO リニア・レギュレータです。この負入力電圧の高いLDO リニア・レギュレータは、−27V~−1.2V のレールを駆動する高性能アナログ回路やミックスド・シグナル回路を調整するのに最適です。

バイポーラDAC

バイポーラ・レンジの生成

テストおよび測定、データ・アクイジション、アクチュエータ制御、産業用オートメーションなどのアプリケーションは、動作中に電圧範囲が変わることがあるため、様々な電圧範囲を必要とします。乗算型DAC やnanoDAC などの単電源DAC は、バイポーラ出力範囲の生成に使用できます。ただし、これらのDAC を使用してバイポーラ出力範囲を生成するには、オペアンプや抵抗などの外付けディスクリート部品を追加する必要があります。このタイプのソリューションでは、基本構成として、汎用DAC と後続の増幅段、オフセット段が含まれています。図1に、単電源DAC を使用したディスクリート・ソリューションの例を示します。ディスクリート・ソリューションは、ボード面積、システム全体の性能、コストが重要でないアプリケーションで利用できます。図1 の回路を実装するには、概算で23mm2の面積が必要です。この概算では、最終出力信号の品質を低下させる、外付け部品の増加によって発生するあらゆる誤差を考慮しています。高価な高精度抵抗を追加してシステム性能を最適化すると、コストが増加します。バイポーラDAC は、バイポーラ出力を生成できますが、そのためにはバイポーラ電源が必要です。更に、全てのバイポーラDAC が、完全なソリューションを実現するためのリファレンス、出力バッファ、リファレンス・バッファを内蔵しているわけではありません。このような場合は、設計時間、ファクタ・フォーム、および適切なデバイスの選択プロセスにより、アプリケーションの複雑度が増します。例えば、必要な仕様を満たすバイポーラDAC に適した電圧リファレンスを選択するため、設計および評価の時間が増加します。統合化ソリューションを選択することでこのオーバーヘッドを削減できます。

AD5761R は、必要な全ての機能を提供し、バッファされたリファレンスと出力バッファを統合する完全なソリューションです。デカップリング・コンデンサが、必要とされる唯一の外付け部品です。提案した構成は、5V 単電源のみが使用できるアプリケーションをサポートします。DC/DC スイッチング・レギュレータ、LCフィルタ、LDOリニア・レギュレータ、抵抗分圧器が、AD5761R の動作に対応するよう用いられています。図2 に、図1 でバイポーラ・レンジを生成するのに必要とされた外付け部品を内蔵する、AD5761R を示します。AD5761R は、小型の3mm × 3mm LFCSP パッケージで提供されます。

AD5761R に対応するよう構成された単電源システム

回路の説明

図2 に示すAD5761R DAC は4 つのユニポーラ出力範囲(0V~5V、0V~10V、0V~16V、0V~20V)と4 つのバイポーラ出力範囲(±3V、±5V、±10V、−2.5V~+7.5V)を実現しています。

このアプリケーション・ノートでは、AD5761R は、8 つの全ての出力範囲をカバーできるように特定の電源電圧で駆動されています。AD5761R は、電圧電源の他に1V の最小ヘッドルーム/フットルームを必要とするため、21V の最小VDD と−11V の最大VSS をDAC に供給します。DAC を使用して低い範囲の電圧を出力する場合は、低い電源電圧を供給します。

このアプリケーション・ノートでは、必要なVDDおよびVSS電圧を提供する2 つの電源構成を示します。システムの許容ノイズ・レベルは、DACへの最適な電源供給方法を決定します。2 つの構成は、以下に示すコンポーネントで構成されています。

- ADP5070 と抵抗ラダー。この場合は、LK1、LK2、LK7、LK8 リンクを挿入します。

- ADP5070 と抵抗ラダーおよびリニア・レギュレータ(ADP7142 およびADP7182)。この場合は、LK1、LK2、LK7、LK8 リンクを除去します。

LK1 リンクおよびLK2 リンクは、回路内のリニア・レギュレータをバイパスし、LK7 リンクおよびLK8 リンクは、これらのリニア・レギュレータの直前で使用可能な電圧を決定します。表1に、LK7 およびLK8 リンク構成のテスト・ポイントA とテスト・ポイントB で使用可能な電圧を示します。

図3 にAD5761R の電源構成を示します。ここで、VDD とVSS は最初のユニポーラ5V 単電源とは異なる方法で生成されています。

| Link | Link Inserted | Link Removed | Test Conditions/Comments |

| LK7 | 21.1 V | 23.2 V | Voltage measured at Test Point A |

| LK8 | -11 V | -13 V | Voltage measured at Test Point B |

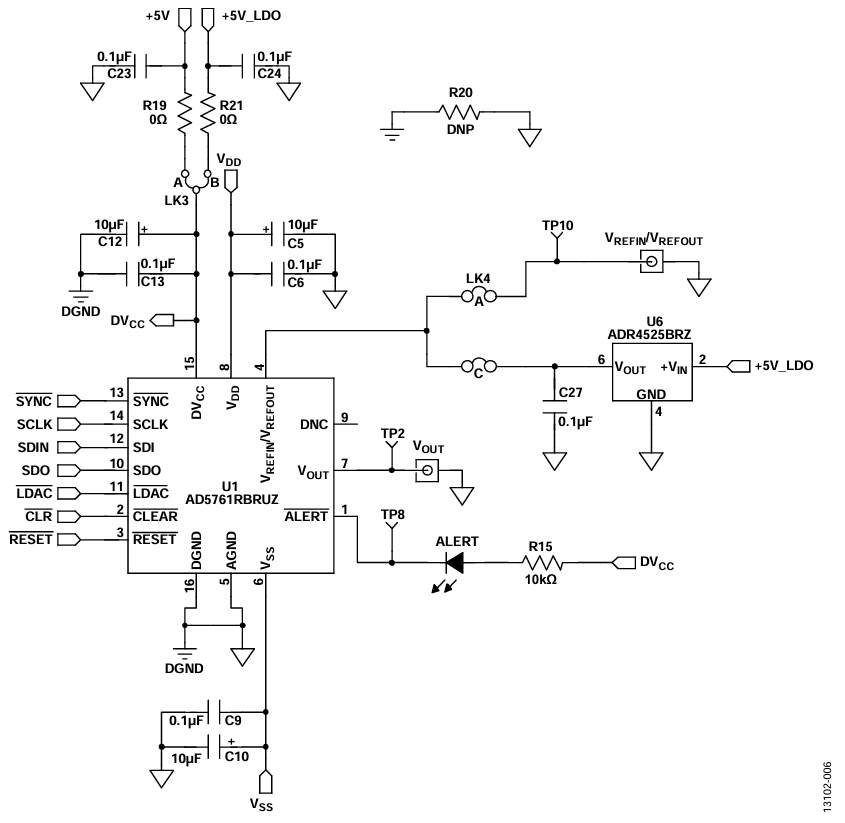

ADR4525 も2.5V のリファレンス電圧を外部から供給できます。図6 を参照してください。

DC/DC スイッチング・レギュレータ

ADP5070 の出力電圧は、LK7 を挿入した場合+21.1V、LK8 を挿入した場合−11V に調整されます。これらの電源電圧は、AD5761R がDAC からの8 つの全てのプログラマブル出力範囲をカバーするのに必要です。

図3 に、主にスイッチング・リップルを打ち消すための2 つのフィルタ部品を示します。インダクタL1 およびコンデンサC14、C16、C19 は、正出力のためのLC フィルタを形成し、インダクタL2 およびコンデンサC15、C17、C20 は負出力で構成されます。これらのLCフィルタは、レギュレータの制御ループ内にあり、リップル周波数においてかなりの減衰をもたらす部品値になっています。リップルを更に打ち消すために、オプションの2 段LDO リニア・レギュレータをスイッチング・レギュレータの出力段に追加しました。LC フィルタのみを用いた場合、AD5761R はデータシート仕様の範囲内で動作します。ノイズ性能を更に向上する必要のあるアプリケーションに対しては、出力段にLDO を用いることができます。

リニア・レギュレータ

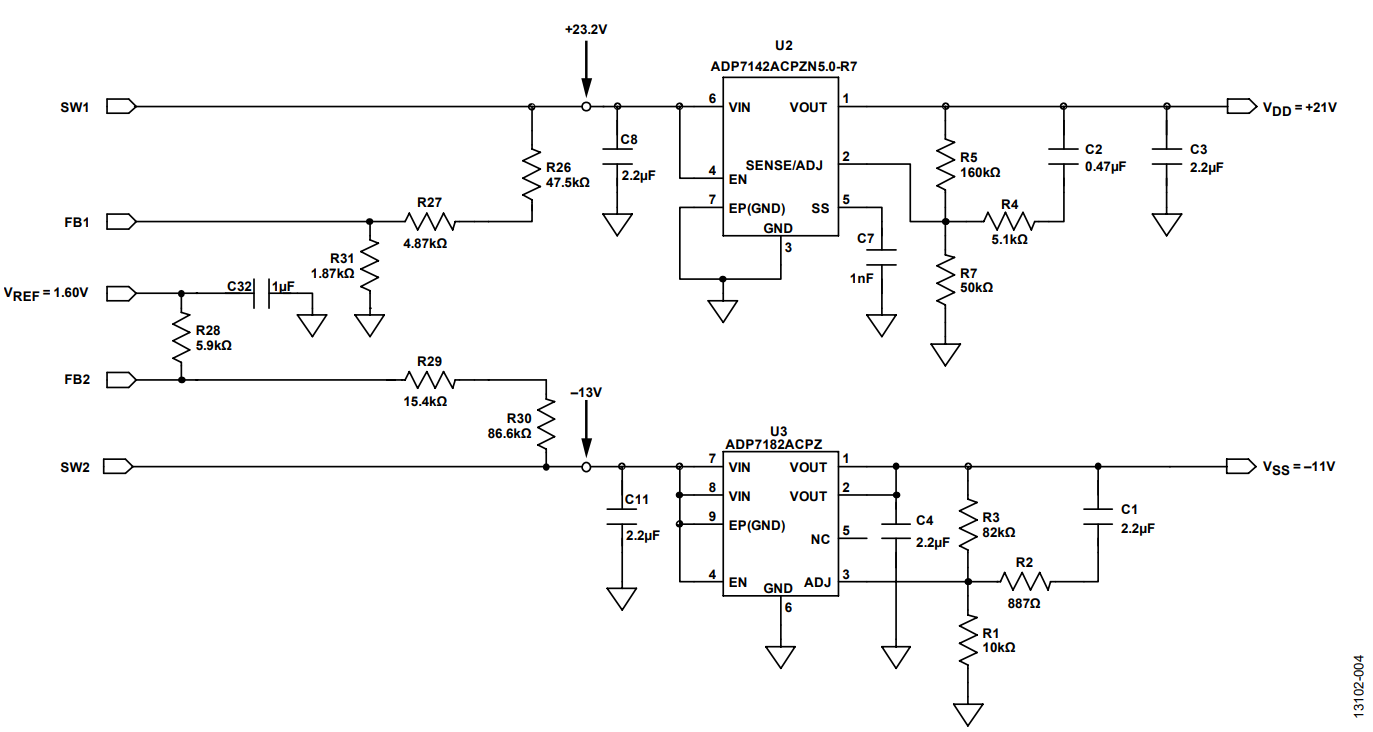

ADP5070 とADP7182 およびADP7142 リニア・レギュレータの組み合わせは、最もノイズが小さい+21V および−11V 電圧電源を可能にします。なお、この方法では、LK1、LK2、LK7、LK8は除去します。

ADP5070 は、+39V の正の電圧と–39V の負の電圧を出力します。図4 に、これらの電圧をADP7142 とADP7182 の許容入力電圧に調整するのに必要な抵抗分圧器を構成している抵抗(R26、R27、R31 およびR28、R29、R30)の値を示します。なお、リニア・レギュレータの目的の出力電圧の他に2V の最小ヘッドルーム/フットルームが必要です。

ADP7142 およびADP7182 の両リニア・レギュレータは、可能な限り小さいノイズで電圧信号を出力できるように構成されています。ADP7182 およびADP7142 のデータシートで説明しているように、超低出力ノイズを得るには出力電圧を設定する抵抗分圧器に2 つの部品を追加する必要があります。誤差アンプのACゲインを低減するためにCNR(C1、C2)とRNR(R2、R4)がRFB1(R3、R5)に並列接続されています。

リニア・レギュレータをスイッチング・レギュレータの出力段に追加と、パッシブ・フィルタによって除去されないスイッチング・レギュレータによるDAC 出力中のノイズを低減するのに役立ちます。

抵抗分圧器

図5 に、抵抗分圧器を使用してADP5070 の正および負の出力電圧をAD5761R に必要な+21V VDD および-11V VSS電圧電源に調整する方法を示します。この構成には、LK1、LK2、LK7、LK8 の各リンクが挿入されるリニア・レギュレータは含まれていません。

DVCC デジタル電源

図6 に、5V の外部電圧信号からAD5761R にデジタル的に給電する方法を示します。ADP5070 で生成され、ADP7142 レギュレータで調整される低ノイズの電圧信号を検討することもできます。

リファレンス電圧

AD5761R は2.5V、5ppm/ºC 内部電圧リファレンスを搭載しています。これはデフォルトでオンになっています。図6 に、LK4の位置に応じてDAC に供給できる2 つの外部電源を示します。

LK4 は位置A に短絡できます。この場合、外部電圧がVREFIN/VREFOUT SMBコネクタへの入力です。内部リファレンスを使用する場合、このコネクタで2.5V を外部用途で使用できます。

LK4 を位置C に短絡した場合、リファレンス電圧は超低ノイズ、高精度電圧リファレンスであるADR4525 から供給されます。

測定と結果

ADP5070 の設定

可能な限り高いリップル振幅を与えて、最も厳しい条件の結果を得るには、ADP5070 のスイッチング周波数を1.2MHz に設定し、高速スルー・モードにします。

AD5761R の電源構成

このセクションで説明する一連の測定では、このバイポーラDACの代表的な出力範囲である±10V 出力電圧範囲の3 つのデータ・コード(ゼロスケール、ハーフスケール、フルスケール)でテストしたAD5761R DAC を示します。一連の測定において、AD5761R は以下に示す4 つの異なる電源構成で駆動されています。

- 外部電源

- DC/DC スイッチング・レギュレータ(ADP5070)とLC 出力フィルタ

- DC/DC スイッチング・レギュレータ(ADP5070)とそれに続くCMOS LDO リニア・レギュレータ(ADP7142 とADP7182)(この電源構成は、AC 性能テストに含まれていません)

- DC/DC スイッチング・レギュレータ(ADP5070)とLC 出力フィルタ、およびそれに続くCMOS LDO リニア・レギュレータ(ADP7142 とADP7182)

DAC の内部リファレンスとADR4525 を使用したAD5761R の性能テストも行いました。

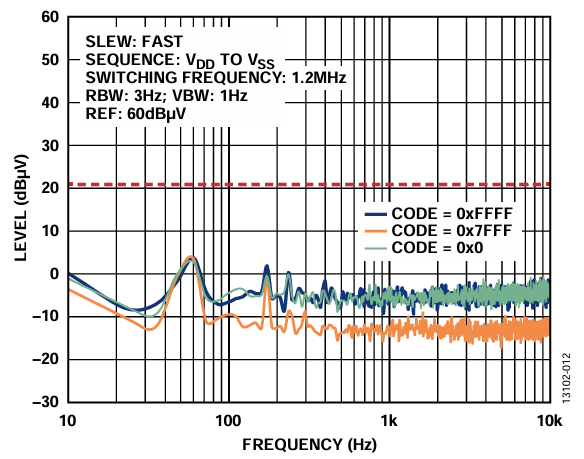

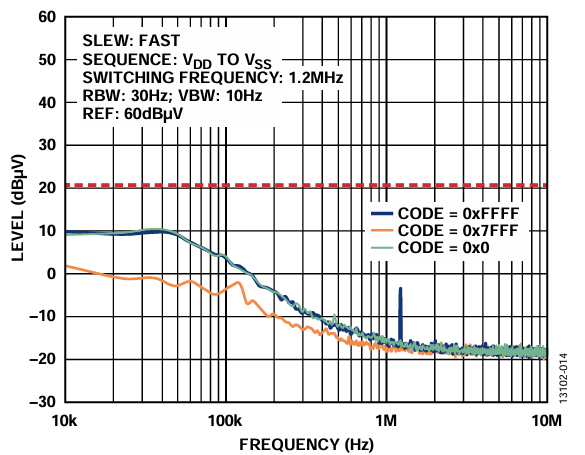

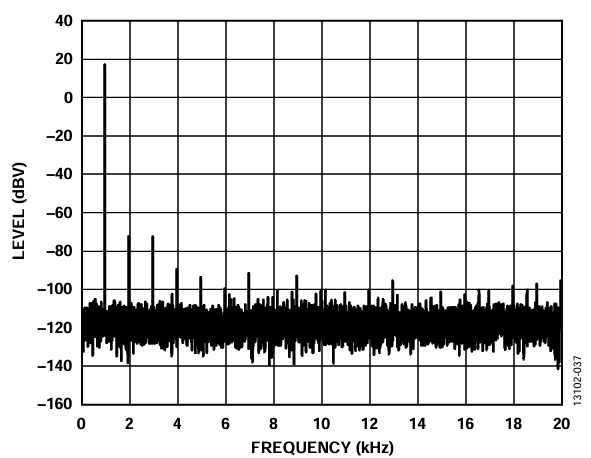

DAC 出力のスペクトル応答

このセクションで説明している結果は、選択した電源構成に応じてDAC 出力ノイズ・スペクトルがどのように変化するかを示しています。図7~図20 に示したスペクトル分析の最大出力スペクトル応答レベルを集めたものを表2 および表3 に示します。

| Power Supply Configuration | Internal Reference | External Reference | ||||

| Zero-Scale | Half-Scale | Full-Scale | Zero-Scale | Half-Scale | Full-Scale | |

| External Supply | 8.00 | 3.63 | 7.04 | 2.60 | 3.39 | 1.45 |

| ADP5070 and LC Output Filters | 6.57 | 2.41 | 8.01 | 2.58 | 3.34 | 3.59 |

| ADP5070, LC Output Filters, and CMOS LDO Linear Regulators | 7.4 | 3.91 | 5.96 | 1.68 | 2.49 | 3.32 |

| Power Supply Configuration | Internal Reference | External Reference | ||||

| Zero-Scale | Half-Scale | Full-Scale | Zero-Scale | Half-Scale | Full-Scale | |

| External Supply | 2.23 | −1.57 | 0.58 | 9.33 | −1.55 | 10.55 |

| ADP5070 and LC Output Filters | 1.19 | −0.62 | 4.37 | 10.27 | 1.73 | 9.64 |

| ADP5070 and CMOS LDO Linear Regulators | 1.85 | −0.93 | 0.69 | 9.89 | −0.98 | 9.22 |

| ADP5070, LC Output Filters, and CMOS LDO Linear Regulators | 1.94 | −2.20 | −0.06 | 9.99 | −1.60 | 10.03 |

表4 には、10kHz~10MHz の周波数範囲にわたる、1.2MHz のスイッチング周波数での最大DAC 出力スペクトル応答レベルを示します。電源構成にLC フィルタを追加することでAD5761R が設定された仕様である20.6dBμV 以内に保たれます。これは0.1LSB レベルを表します。LDO を2 段目のフィルタとして追加することで、外部電源動作に匹敵するレベルまでリップルが低減し、最小限のノイズ出力でDAC を実行できます。

| Power Supply Configuration | Internal Reference | External Reference | ||||

| Zero-Scale | Half-Scale | Full-Scale | Zero-Scale | Half-Scale | Full-Scale | |

| External Supply | −17.07 | −17.06 | −16.96 | −16.49 | −17.48 | −17.5 |

| ADP5070 and LC Output Filters | −14.99 | −11.47 | −2.44 | −15.69 | −10.34 | −3.62 |

| ADP5070 and CMOS LDO Linear Regulators | −16.78 | −17.93 | −16.68 | −17.51 | −18.37 | −16.63 |

| ADP5070, LC Output Filters, and CMOS LDO Linear Regulators | −17.07 | −18.39 | −17.64 | −16.53 | −16.43 | −17.01 |

外部電源とAD5761R の構成

図7~図10 に示しているスペクトルのパターンは、後続のAD5761R DAC およびADP5070 ダイレクト・スイッチング・レギュレータ評価の基準プロットとして使用します。図7~図10の赤い点線は、スペクトル・レベルの閾値レベルを表します。閾値レベルは20.6dBμV に設定されており、これは約0.1LSB の値を表します。図7~図20 で、RBW は分解能帯域幅、VBW はビデオ帯域幅、REF はリファレンス値です。VBW は、一般に測定装置のビデオ・フィルタに関連するもので、これにより対象とする信号がより良好に表示されます。フロア・ノイズを維持しながらもトレースのノイズを低減します。

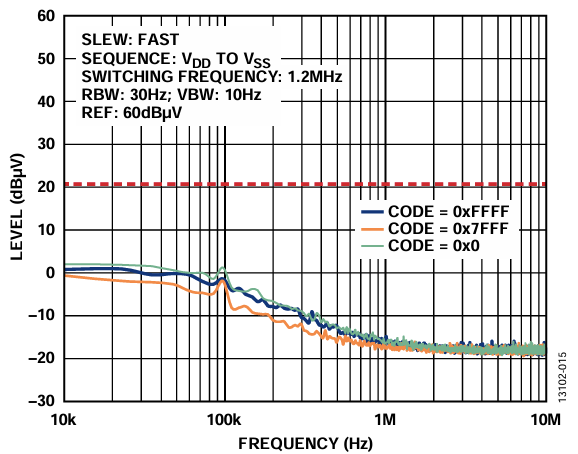

DC/DC スイッチング・レギュレータおよびLC 出力フィルタ電源構成

この電源構成では、初期リップル除去にLCフィルタを使用し、バイポーラ電源範囲を生成するのにADP5070 ダイレクト・スイッチング・レギュレータを使用しています。図11 および図12に、10Hz~10kHz の周波数帯域幅のリップル・レベルを示します。また、図13 および図14 に、10kHz~10MHz の周波数帯域幅のリップル・レベルを示します。

図13 および図14 に、10kHz~10MHz の周波数帯域幅での1MHzにおける周波数スパイクを示します。LC フィルタは、ADP5070DC/DC レギュレータからのこのリップルの振幅を十分に低減しません。そのため、この電源ソリューションの性能は、スペクトル分析の観点から理想的ではありません。

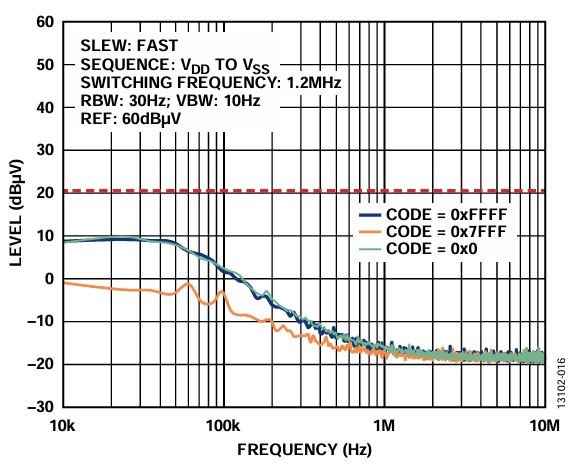

DC/DC スイッチング・レギュレータおよびCMOSLDO リニア・レギュレータ電源構成

ADP5070 DC/DC レギュレータの出力にLDO を追加することで、1MHz の周波数で観測されるスパイクを大幅に低減できます(DC/DC スイッチング・レギュレータおよびLC 出力フィルタ電源構成のセクションを参照)。この低減は、電源回路にLCフィルタを追加しなくても、優れた性能が得られることを表しています。

図15 および図16 に、高周波数でのADP5070、LDO、およびAD5761R 電源構成を示します。

DC/DC スイッチング・レギュレータ、LC 出力フィルタ、およびCMOS LDO リニア・レギュレータ電源構成

DC/DC スイッチング・レギュレータおよびLC 出力フィルタ電源構成に2 つのLDOを追加すると、AD5761R のアナログ電源でのリップルを更にフィルタリングできます。ADP7142 はアナログ正電源(VDD)で使用し、ADP7182 はアナログ負電源(VSS)に配置します。

DC/DCスイッチング・レギュレータおよびCMOS LDOリニア・レギュレータ電源構成のセクションで説明したように、高周波数での動作時には、不要な周波数にスパイクが追加されることなく優れたDC 出力スペクトル応答性能を得るのに、ADP5070DC/DC スイッチ出力にLDO を追加するだけで十分です。LCフィルタも出力ノイズ除去に作用しますが、出力ノイズを軽減する最大の要素はLDO です。ただし、それでもLC フィルタは、高周波リップルを十分にフィルタ処理するために推奨されるオプションです。

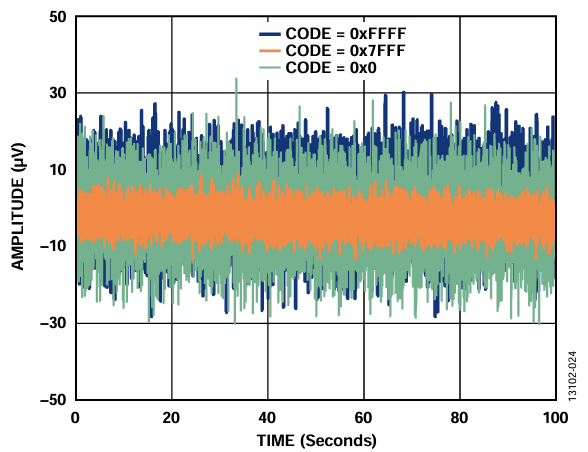

AD5761R 出力電圧ノイズ

高精度の応答を実現するには、DAC の出力で得られるピークtoピーク・ノイズを1LSB(16 ビット分解能および20V ピークtoピーク電圧範囲では305.17μV)未満に保つことを推奨します。AD5761R の出力ノイズの代表値は、0.1Hz~10Hz の周波数帯域幅で15μV p-p、100kHz 周波数帯域幅で35μV rms(約100μV p-pと等価)です。AD5761R の±10V 範囲の出力のノイズを0.1Hz~10Hz 周波数範囲および100kHz 帯域幅にわたって100 秒間測定しました。

3 つの異なる構成のテスト結果は、DAC がAD5761R データシートの仕様範囲内で動作していることを示しています。図21~図34は、各構成および周波数帯域幅のDAC の出力でのノイズを示しています。表5~表11 は、使用可能な電源構成のDAC の出力の最大ピークto ピーク・ノイズを示しています。

表2~表12 および図7~図37 のデータは、このアプリケーション・ノートで詳述する全電源構成に共通の傾向です。帯域幅の比較的低周波数の領域では、ADR4525 外部リファレンスのほうが、AD5761R 内部リファレンスを用いた場合に比べDAC 出力ノイズが低くなっています。反対に、帯域幅の比較的高周波数の領域では、内部リファレンスを用いた場合のほうがDAC 出力ノイズは低くなっています。この傾向は、前述のDAC 出力スペクトル応答結果に対応しています。

電源構成にLDO を追加すると、図31 および図32 に現れているDAC 出力ノイズの低周波数帯域の性能にわずかに影響が出ます。

それに対して、高い周波数帯域では、電源構成にLDO を追加することでノイズの低い全体性能を維持できます。図29 および図30に、ADP5070 とLDO でDACを最大100kHz の高周波数帯域で駆動した場合のAD5761R 出力ノイズを示します。

| Code | Maximum Peak-to-Peak Output Noise | |

| AD5761R Internal Reference | ADR4525 | |

| Zero-Scale | 41 µV p-p, 0.13 LSB p-p | 12 µV p-p, 0.04 LSB p-p |

| Half-Scale | 6.2 µV p-p, 0.02 LSB p-p | 4.8 µV p-p, 0.016 LSB p-p |

| Full-Scale | 40 µV p-p, 0.13 LSB p-p | 14 µV p-p, 0.04 LSB p-p |

| Maximum Peak-to-Peak Output Noise | ||

| AD5761R Internal Reference | ADR4525 | |

| Zero-Scale | 33.6 µV p-p, 0.11 LSB p-p | 63.2 µV p-p, 0.21 LSB p-p |

| Half-Scale | 21 µV p-p, 0.07 LSB p-p | 22 µV p-p, 0.07 LSB p-p |

| Full-Scale | 32 µV p-p, 0.10 LSB p-p | 58.4 µV p-p, 0.19 LSB p-p |

| AD5761R Internal Reference | ADR4525 | |

| Zero-Scale | 41 µV p-p, 0.13 LSB p-p | 13 µV p-p, 0.04 LSB p-p |

| Half-Scale | 6.6 µV p-p, 0.02 LSB p-p | 4.4 µV p-p, 0.014 LSB p-p |

| Full-Scale | 38 µV p-p, 0.12 LSB p-p | 13 µV p-p, 0.04 LSB p-p |

| Code | Maximum Peak-to-Peak Output Noise | |

| AD5761R Internal Reference | ADR4525 | |

| Zero-Scale | 44.4 µV p-p, 0.15 LSB p-p | 68.2 µV p-p, 0.22 LSB p-p |

| Half-Scale | 30.8 µV p-p, 0.10 LSB p-p | 30.4 µV p-p. 0.10 LSB p-p |

| Full-Scale | 75.2 µV p-p, 0.25 LSB p-p | 88.8 µV p-p, 0.29 LSB p-p |

| Code | Maximum Peak-to-Peak Output Noise | |

| AD5761R Internal Reference | ADR4525 | |

| Zero-Scale | 35.2 µV p-p, 0.12 LSB p-p | 60.4 µV p-p, 0.20 LSB p-p |

| Half-Scale | 22.8 µV p-p, 0.07 LSB p-p | 22.4 µV p-p, 0.07 LSB p-p |

| Full-Scale | 31.2 µV p-p, 0.10 LSB p-p | 67.6 µV p-p, 0.22 LSB p-p |

| Code | Maximum Peak-to-Peak Output Noise | |

| AD5761R Internal Reference | ADR4525 | |

| Zero-Scale | 40.6 µV p-p, 0.13 LSB p-p | 12.8 µV p-p, 0.04 LSB p-p |

| Half-Scale | 5.4 µV p-p, 0.018 LSB p-p | 4.4 µV p-p, 0.014 LSB p-p |

| Full-Scale | 45.2 µV p-p, 0.15 LSB p-p | 13.2 µV p-p, 0.04 LSB p-p |

| Code | Maximum Peak-to-Peak Output Noise | |

| AD5761R Internal Reference | ADR4525 | |

| Zero-Scale | 36.8 µV p-p, 0.12 LSB p-p | 60.4 µV p-p, 0.2 LSB p-p |

| Half-Scale | 23.8 µV p-p, 0.08 LSB p-p | 22.6 µV p-p, 0.07 LSB p-p |

| Full-Scale | 33.6 µV p-p, 0.11 LSB p-p | 60 µV p-p, 0.2 LSB p-p |

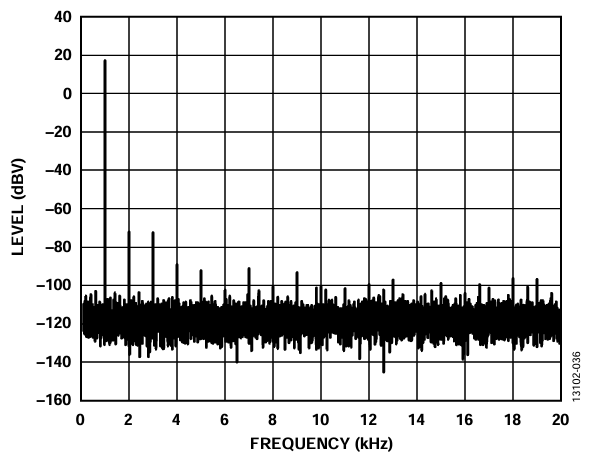

AC 性能

このセクションでは、ADR4525 を電圧リファレンスとして使用した電源構成のS/N 比、全高調波歪み(THD)、信号/ノイズ+歪み(SINAD)、スプリアスフリー・ダイナミック・レンジ(SFDR)の各パラメータについて説明します。表12 は、図35~図37 に示す3 つの電源構成において、連続する1kHz のサイン波を生成して得られたAC 性能をまとめたものです。

| Parameter | External Supply and AD5761R (dB) | ADP5070, LC Filters, and AD5761R (dB) | ADP5070, LC Filters, LDOs, and AD5761R (dB) |

| SNR | 95.05 | 95.19 | 95.24 |

| THD | −86.38 | −86.30 | −86.52 |

| SINAD | 85.82 | 85.77 | 85.98 |

| SFDR | 89.42 | 89.35 | 89.45 |

まとめ

AD5761R は、出力アンプ、リファレンス・バッファ、リファレンスを内蔵した、16 ビットのバイポーラDACです。チップ内での高集積化が行われているため、完全なソリューションが可能です。このアプリケーション・ノートでは、ADP5070 DC/DC スイッチング・レギュレータを用いた、単電源レールによるAD5761R 用の柔軟な電源ソリューションを紹介しています。

提示した構成および結果は、AD5761R が仕様の範囲内で動作していることを示しています。0.1Hz~10Hz の周波数帯域幅でDAC 出力の低ノイズ応答を得るための推奨電源ソリューションには、ADP5070、LCフィルタ、AD5761Rが含まれます。ただし、高周波数帯でDAC 出力の低ノイズ応答が必要な場合は、最適な電源ソリューションには、ADP5070、LCフィルタ、LDOレギュレータ、AD5761R が含まれます。また、LC フィルタを電源ソリューションから取り除いた場合も性能はこれと同等であり、ADP5070 によるスイッチング・スプリアスを目標LSB 閾値まで低減できます。

異なる電源構成の間には、性能にわずかな相違がありますが、これは、外部電源を用いたベースライン測定の結果と同等のものです。