PSRRの仕様に基づくデカップリングの要件

本稿のPart 1で説明したように、デジタル電流/アナログ電流のリターン・パスについては、グラウンド・プレーンのインピーダンスを低く抑えるように配慮することが重要です。それと同等に重要な事柄に、デカップリングがあります。これは、ICに対する電源供給部のインピーダンスを低く抑えるための手法です。Part 2では、このデカップリングについて詳しく説明します。

オペアンプやコンバータなどのアナログICは、複数の電源ピンを備えています。単電源のICの場合、それらのピンのうち1つはグラウンドに接続されます。また、A/Dコンバータ(ADC) やD/Aコンバータ(DAC) などのミックスド・シグナルICでは、アナログ電源、デジタル電源、I/O 電源には異なる電圧が使用されます。なお、FPGAなどのデジタルICの中にも、コア部、メモリ部、I/O部のそれぞれに異なる電源電圧が使用されるものがあります。

電源ピンの数にかかわらず、ICのデータシートには、各電源が許容できる電圧範囲として動作電圧と絶対最大定格の値が規定されています。ICの破損を防ぐことはもちろん、適切な動作が得られるようにするには、それらの制約を順守する必要があります。

しかし、現実の電源電圧には、ノイズや電源リップルといったかたちで小さな変動が生じます。仮にその変動がデータシートで規定された動作電圧の範囲内に収まっていたとしても、ICの性能は低下してしまう可能性があります。

例えば、オペアンプICの電源電圧が変動すると、入出力電圧がわずかに変化します(図1)。

通常、電源電圧に対するオペアンプICの感度は電源電圧変動除去比(PSRR) として定量化されます。PSRRは、電源電圧の変化に対する出力電圧の変化の比として定義されます。詳細については、Tutorial MT-043をご覧ください。

図1では、標準的なオペアンプICである「OP1177」を例にとっています。PSR( ここでは、dB単位のPSRRを表す) は、周波数が高くなるにつれ、約6dB/oct( 20dB/dec)で低下します。グラフ上の曲線は、それぞれ正電源と負電源のPSRを表しています。PSRRは、DCでは約120dBあります。しかし、周波数が高くなるほど電源ラインの不要なエネルギーが出力に直接カップリングしやすくなります。そのため、PSRR は急激に低下していきます。

オペアンプによって負荷を駆動する場合、電源レールに不要なインピーダンスが存在すると、負荷電流によって電源レールに変調が生じてしまいます。その結果、ノイズが増加し、AC信号に歪みが生じます。

ADC/DACをはじめとするミックスド・シグナルICでも、電源のノイズによって特性が劣化します。ただ、データシートにはあらゆる条件下におけるPSRRの値まで記載されているわけではありません。なお、電源ノイズは、デジタル回路にもさまざまな影響を及ぼします。例えば、ロジック・レベルのノイズ・マージンが減少したり、クロック・ジッタに起因するタイミング誤差が発生したりすることがあります。

プリント基板では、適切な局所的デカップリングが不可欠

通常、標準的な4層プリント回路基板には、2つの信号レイヤに挟まれるかたちでグラウンド・プレーンと電源プレーンのレイヤが設けられています。この種の基板を使用する場合、表面実装型ICのグラウンド・ピンは、ビアで直接グラウンド・プレーンに接続します。それにより、グラウンドへの接続に伴う不要なインピーダンスが最小限に抑えられます。

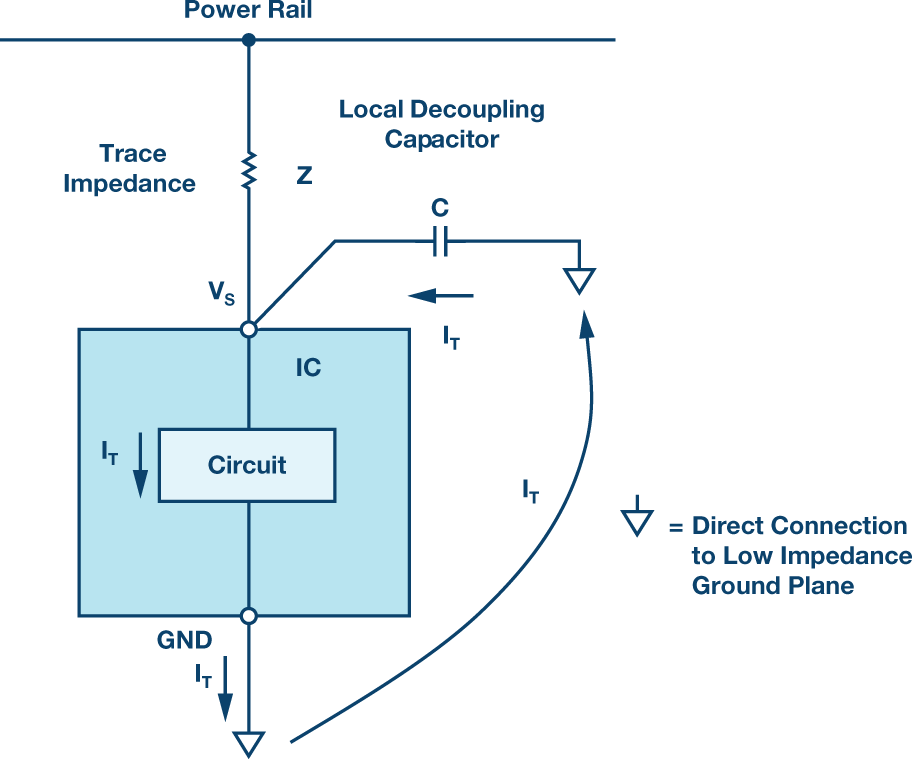

また、電源レールは通常、電源プレーンに設けられ、ICの各電源ピンに接続されます。図2は、ICに対する電源とグラウンドの接続をシンプルにモデル化したものです。

図においてITはIC内を流れる電流を表しています。この電流がパターンのインピーダンスZに流れることにより、電源電圧VSに変動が生じます。その結果、ICのPSRによっては、特性の面でさまざまな問題が生じるおそれがあります。

電源のノイズとリップルに対する感度は、次のような方法によって最小限に抑えることができます。それは、電源ピンとグラウンド・プレーンの間に、適切な種類のデカップリング・コンデンサをできるだけ短い配線で直接接続するというものです。デカップリング・コンデンサは、過渡的な電流に対応して電荷を蓄積する役割を果たすとともに、過渡的な電流をグラウンドに直接シャントします。そのため、ICに供給される電源電圧が一定に保たれます。リターン電流のパスはグラウンド・プレーンを介しますが、そのインピーダンスは低く抑えられます。したがって、一般にリターン電流によって大きな誤差電圧が生じることはありません。

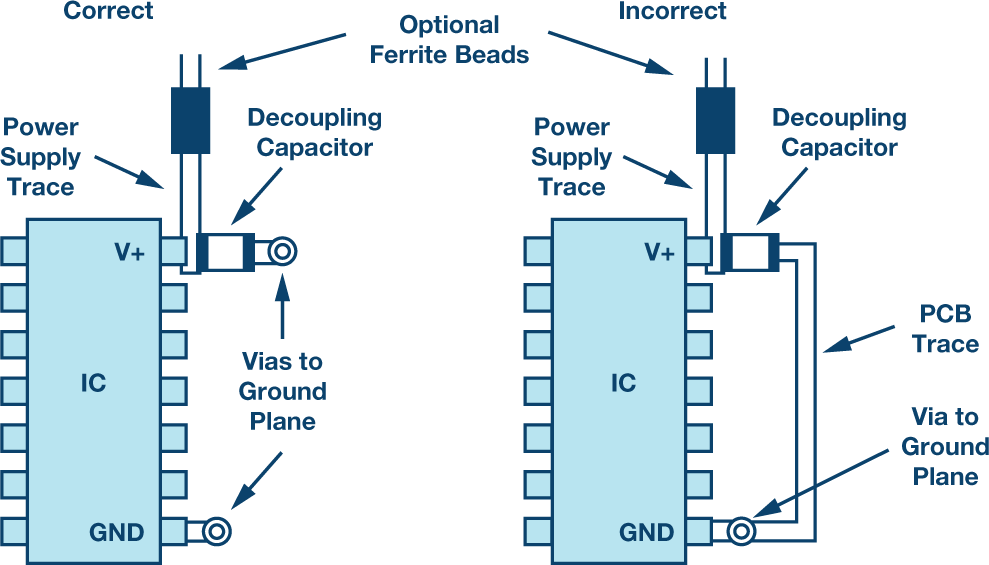

図3に示したように、高周波向けのデカップリング・コンデンサは、可能な限りICの近くに配置しなければなりません。そうしなければ、接続に使用するパターンのインダクタンスによって、デカップリングの効果に悪影響が及んでしまうからです。

図3 . 高周波向けデカップリング・コンデンサの適切な配置と不適切な配置

図3 (a) では、電源ピンとグラウンドへの接続が最短になっているため、最も効果的な構成だと言えます。一方、図3(b)では、グラウンドへの接続に長いパターンを使用しています。このことから、余分なインダクタンスと抵抗によってデカップリングの効果が抑制されてしまいます。また、長い閉ループによって干渉の問題が生じるおそれもあります。

デカップリング・コンデンサの適切な選択

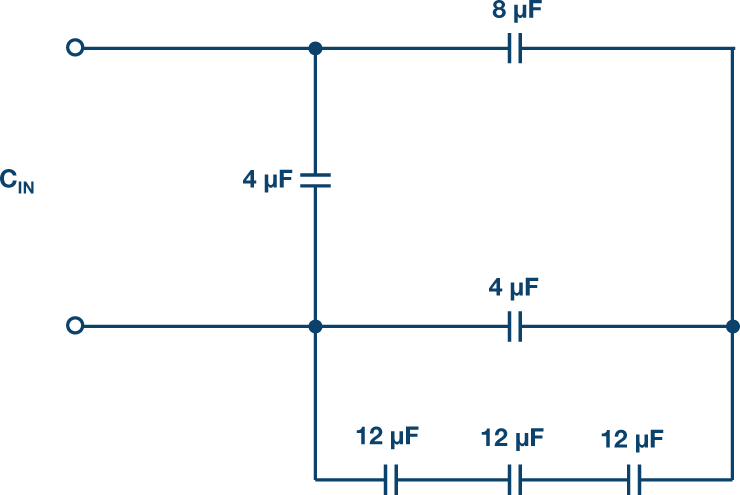

通常、低周波ノイズのデカップリングには、低周波の過渡電流に対応して電荷を蓄積可能な電解コンデンサが必要になります(値は1µF ~ 100µF程度)。一方、高周波の電源ノイズを低減するには、インダクタンスの小さい表面実装型のセラミック・コンデンサを使用します(値は0.01µF ~ 0.1µF程度)。これらをICの電源ピンに直接接続するのが最も有効な手段です。デカップリング・コンデンサは、インピーダンスの低いグラウンド・プレーンに直接接続しなければ効果がありません。直列に追加される寄生インダクタンスを最小限に抑えるために、短いパターンとビアを使って接続を行う必要があります。

ほとんどのICについては、データシートのアプリケーションのセクションに、電源デカップリング用の推奨回路が掲載されています。各ICを正しく動作させるには、そうした推奨事項に従う必要があります。

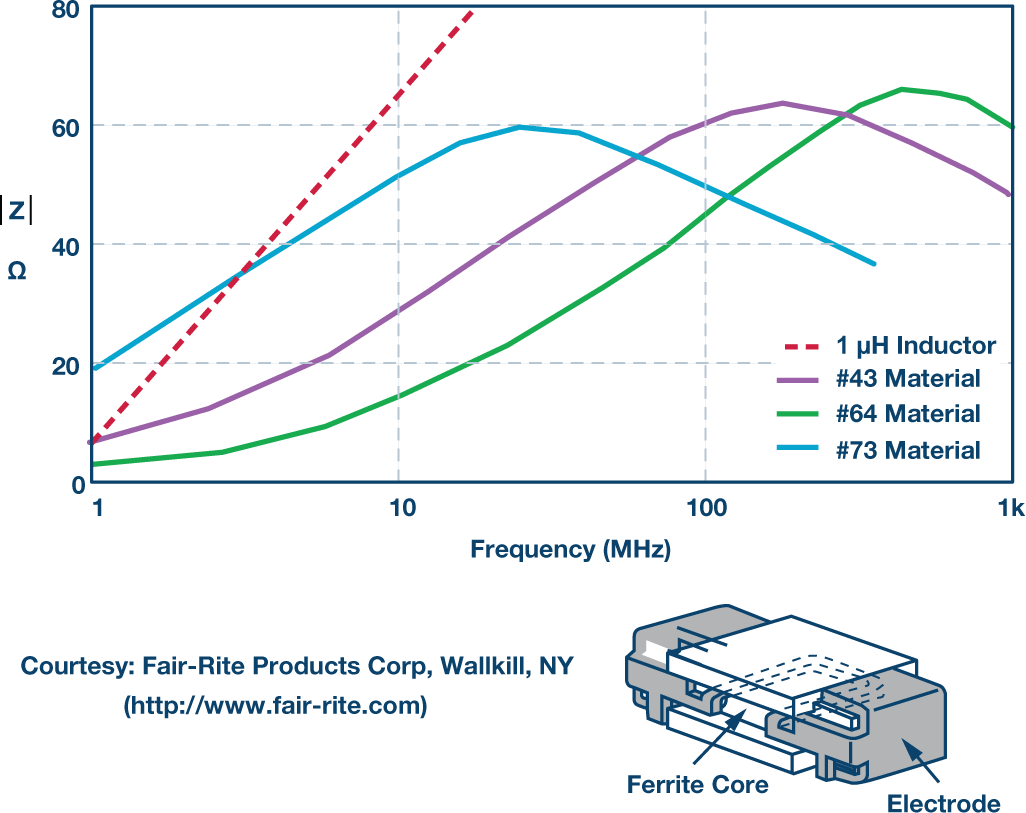

フェライト・ビーズは、ニッケル、亜鉛、マンガンなどの酸化物を材料とする非導電性のセラミックです。これも、電源のデカップリングを実現するためのフィルタに使用できます。低周波(100kHz未満)の領域において、フェライトは誘導性のデバイスとして機能します。そのため、LC型のローパス・フィルタ(デカップリング・フィルタ)に使用できます。一方、フェライトは100kHzを超えると、抵抗性の応答を示します(Q値が小さくなります)。フェライトのインピーダンスは、その材質、対応周波数範囲、DCバイアス電流、巻数、サイズ、形状、温度によって異なります。

フェライト・ビーズは必須のデバイスというわけではありません。ただ、高周波ノイズを隔離してより効果的なデカップリングを実現できるので、多くの用途で活用できます。注意が必要なのは、フェライト・ビーズが決して飽和しないようにすることです。これについては、オペアンプが多くの出力電流を供給する場合、特に注意を払う必要があります。フェライト・ビーズは飽和すると非線形性を示すようになり、フィルタリングの効果が得られなくなります。

フェライト・ビーズの中には、完全に飽和する前に非線形性を示すものがあります。このことにも注意してください。低歪みの出力で電源段を駆動しなければならない場合には、プロトタイプによって、フェライト・ビーズが飽和領域の近くで動作するか否かを確認する必要があります。図4に、一般的なフェライト・ビーズのインピーダンス特性を示しました。

寄生抵抗や寄生インダクタンスによって、コンデンサに非理想的な動作が生じないようにするには、慎重な検討に基づいて適切な種類のデカップリング方法を選択する必要があります。次回は、さまざまな種類のデカップリング・コンデンサと、それらの使い方について説明します。

最後に、恒例となっている回路の問題を紹介します。正解はEngineerZone®のStudentZoneでご確認ください。

参考資料

アプリケーション・ノートAN-1142「高速ADC用プリント基板のレイアウト・テクニック」AnalogDevices、2012年1月

チュートリアル MT-100「Breadboarding and Prototyping Techniques(ブレッドボーディング/プロトタイピングのテクニック)」Analog Devices、2009年

チュートリアル MT-101「Decoupling Techniques(デカップリングのテクニック)」Analog Devices、2009年

チュートリアル MT-031「データ・コンバータのグラウンディングと、「AGND」および「DGND」に関する疑問の解消」Analog Devices、2009年