概要

より高速なインターネット接続を求める声に牽引され、ケーブル・テレビ(CATV)の業界は新たなネットワーク・アーキテクチャを開発しました。そのアーキテクチャは、加入者にマルチギガビット対応のサービスを提供するためのものであり、ファイバ・ディープ・アプローチを採用しています。その特徴は、デジタル・ファイバによって重要なハードウェアをユーザの近くに配備する点にあります。リモートの物理デバイス(RPD:Remote PHY Device)は、ワイヤレス(セルラー)ネットワークのリモート・ラジオ・ヘッド(RRH)に相当します。RPDは、スペースを節約しつつ、ヘッドエンド(CMTS:Cable Modem Termination System)における放熱を抑えることを可能にします。その一方で、RPDの導入により、設計上の新たな課題がもたらされています。

CATVの信号は、周波数こそ低いもののワイヤレス・システムよりもはるかに広い帯域幅を使用します。具体的には、108MHz~1218MHzという数オクターブにわたる帯域幅が使用されるので、帯域内には複数の高調波が存在する状態になります。実は、RPDは設計者に対して最悪の状況をもたらしました。なぜなら、RF/ミックスド・シグナルのハードウェアによって、非常に広い周波数範囲をカバーしなければならなくなったからです。しかも、DCの消費電力を抑えつつ、より高いRF出力、より低いノイズ・フロア、より高い直線性を実現する必要があります。通常、ダウンストリーム(下り)の最終段に配置されるRFアンプは、1つにつき18Wもの電力を消費します。4ポートのシステムの場合、RFアンプは、RPDに供給される(そしてRPDで消費される)140W~160Wの電力バジェットのうち、約50%に相当する電力を消費することになります。

アナログ・デバイセズは、CATVにおいて効率の向上を実現するためのデジタル・プリディストーション(DPD:Digital Predistortion)技術を有しています。この技術は、DPD向けに最適化されたパワー・ダブラ「ADCA3992」に適用されています。このICに、「AD9162」などの高速D/Aコンバータ(DAC)、「AD9208」などの高速A/Dコンバータ(ADC)、集積度の高いクロック・ソリューション「HMC7044」を組み合わせることで、全帯域に対応するDPDを実現することができます。

本稿では、まず、RPDの進化について簡単に解説します。続いて、当社のアルゴリズム/IP(Intellectual Property)コアをお客様のFPGAに実装することで独自のDPDを実現する方法を紹介します。更に、当社が効率と直線性の問題をどのようにして解決したのか、その方法について詳しく説明します。

背景

CATVは、60年以上前に導入された技術です。それ以来、CATVは、単方向(ダウンストリームのみ)のアナログ・リンクから、アナログTV、IP(Internet Protocol)ベースのSD(標準画質)/HD(高精細)デジタルTV、インターネットに対するデータの高速ダウンロード/アップロードを実現するためのマルチモード、マルチチャンネルの複雑な双方向システム(上りまたはリバース・パスを含む)へと進化してきました。これらのサービスは、マルチプル・システム・オペレータ(MSO)によって提供されています。

ケーブルを利用したデータ通信とデジタルTVのサービスは、CableLabsに参画した企業らによって策定されたDOCSIS(Data over Cable Systems Interface Specification)という仕様にのっとって利用者に配信されています。ヘッドエンドの構成においては、EdgeQAM変調器を独立したユニットまたはCCAP(Converged Cable Access Platform)の一部としてCMTSと統合/追加するなど、様々な進化がありました。ダウンストリームのデータ容量に対する需要は、現在、約50%の年平均成長率(CAGR)で高まっています。つまり、約21ヵ月ごとに需要が倍増しているということです1。この需要を満たすために、1997年にDOCSIS 1.0がリリースされました。それ以来、ダウンストリームのデータ・レートは、40Mbpsから1.2Gbpsまで高められました(広く利用されているDOCSIS 3.0の実装の場合)。

ダウンストリームの伝送速度の向上は、チャンネル・ボンディング、変調の高度化(64QAMから256QAMへの移行)、ダウンストリームの上限周波数の向上(550MHzから750MHzへ、更には1002MHzへ)など、複数の技術を組み合わせることで実現されました。米国の場合、これらの技術は、従来のアナログTVサービスで採用されていた6MHzのチャンネル・プラン(EuroDOCSISとC-DOCSISでは8MHz)を維持しつつ実装されました。しかし、ダウンストリームで最大10Gbpsのレートを得るためには、より抜本的な改革が必要でした。その結果、2013年にリリースされたのがDOCSIS 3.1です。DOCSIS 3.1では、従来の規格をサポートしつつ、よりスペクトル効率が高いOFDM(Orthogonal Frequency Division Multiplexing:直交周波数分割多重)を採用しています。それにより、4096QAMの利用も可能になり、最高190MHzのチャンネル帯域幅に対応しています。また、ダウンストリームにおける上限周波数が従来よりも20%以上高い1218MHzに設定されています。この周波数は、オプションで1794MHzまで拡張可能です。

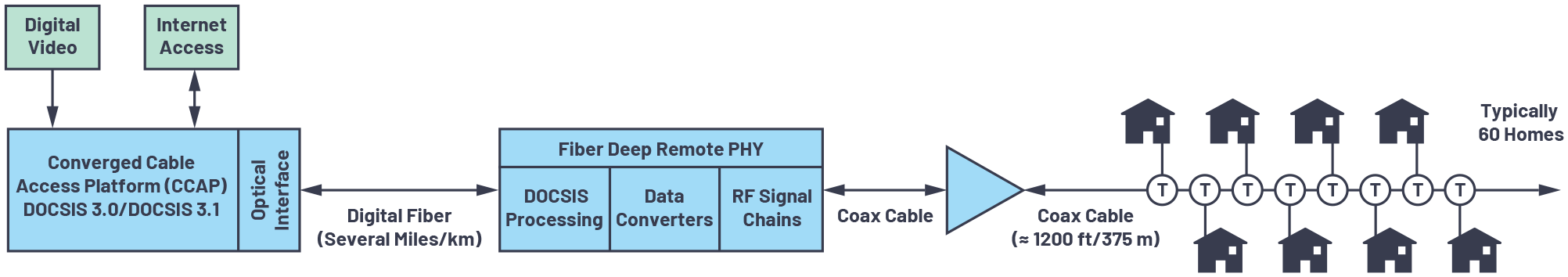

時を経ても変わっていないことがいくつかあります。その1つは、加入者のケーブル・モデムとの物理的なリンクに、インピーダンスが75Ωの同軸ケーブルを使用していることです。1990年代以前のシステムでは、ヘッドエンドと加入者の間には、必ず同軸ケーブルが使用されていました。しかし、現在では、敷設されるのはほぼ間違いなくHFC(Hybrid Fiber Copper)です。HFCを使用する場合、アナログの電気‐光コンバータがヘッドエンドの同軸出力に接続されます。信号は、ファイバを用いてサービス・エリアの近くのノードに伝送されます。その後、光‐電気コンバータを通過し、最終的には同軸ケーブルによって加入者に配信されます。加入者に対するラストマイルの接続には、オーバーヘッド・ケーブルか地下ケーブルが使用されます。この部分がシステムにおけるボトルネックになっています。FTTH(Fiber to the Home)リンクへのアップグレードは、非常に費用がかかるという問題を抱えています。そのため、CATVサービスを提供するMSOは、既存の同軸ケーブルの資産を最大限に活用するという決定を下しています。ツイスト・ペアの電話ケーブルと比較すると、同軸ケーブルは、干渉やクロストークに対して高いシールド性能を備えています。また、インピーダンス・ミスマッチによる信号の反射レベルも小さく抑えられます。そのため、同軸ケーブルは、比較的良好な環境を提供するケーブルだと言えます。ただ、ノードから最も遠い加入者までの標準的な距離が最大1200フィート(約366m)にも達するという状況では、損失の周波数依存性が大きくなります(108MHzから1002MHzの間で傾きは約17dB)。そのため、ハイパス応答のRFフィルタを挿入し、プリエンファシスあるいはチルトを加える必要があります。

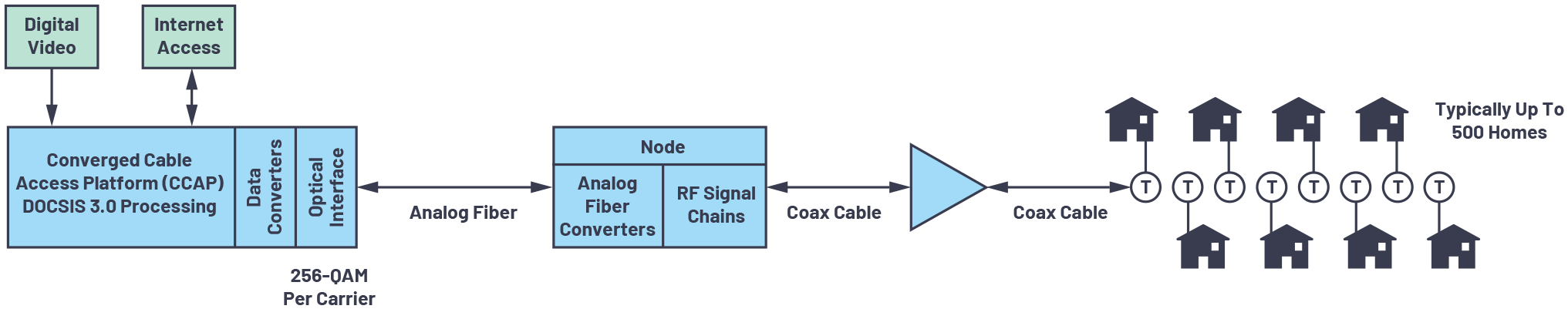

図1に、HFCの標準的な配備方法を示しました。この方法では、光ノードに接続した1本のトランク同軸ケーブルにより、数百の加入者に対して信号を送信します。それに向けて、信号をサブグループに分配するためのマルチウェイRFスプリッタと、個々の加入者にドロップ・ケーブルを接続するためのタップを用意する必要があります。標準的なノード + nのシステムでは、広帯域のブースタ・アンプが一定の間隔でネットワークに挿入されます。それにより信号のレベルを高め、ケーブル・モデムにおける十分なS/N比を確保します。

より多くのデータ容量を加入者に提供する

DOCSISのトランク・ケーブルで利用可能なデータ帯域幅は、接続した全ユーザによって共有されます。全ユーザに提供する帯域幅を増加させるための選択肢としては、次の2つが考えられます。

- ケーブルにおけるデータ転送レートを高める

- ケーブルに接続するユーザの数を削減する

先述したように、ヘッドラインのデータ・レートは、チャンネル・ボンディングを使用したり、より高次の変調方式を適用したり、帯域幅を拡張して利用可能なチャンネルを増やしたりすることで高めることができます。とはいえ、ダウンストリームの容量の増加は、解決策の一部にすぎません。そこで、ネットワークのアーキテクチャの改良も図られました。最初に行われたのは、ノードのセグメンテーションや分割によって、1つのノードに接続する加入者数を減らすことです。具体的には、サポートする加入者数を最大2000から500未満まで削減しました。これは効果的な手法でしたが、多くの費用を要しました。セグメンテーションや分割に代わる方法として考えられるのは、デジタル・ファイバ・リンクを備えたDAA(Distributed Access Architecture)を使用してCCAPからPHYを分離することです。つまり、図2のようにネットワーク・アーキテクチャを変更するということです。RPDのハードウェアには、ダウンストリーム用の変調段とRF段に加え、アップストリーム用のRF段と復調段が含まれます。体積が大きく消費電力の多いPHYコンポーネントをCCAPから分離することにより、ヘッドエンドの位置にエッジ・ルータを配置した仮想CCAPを実現することも可能になります。

デジタル・ファイバは、アナログ・ファイバよりもかなり高い性能を備えています。到達距離が長く(ノードの位置を決める際の柔軟性が向上)、単一のファイバで約5倍の波長に対応可能です。また、DAAによるアプローチでは、従来のHFCネットワークで必要だった電気‐光変換と光‐電気変換が不要になります。これらのことから、光ノードの出力における信号のダイナミック・レンジが抑制されます。つまり、ノイズ・フロアとアナログ変換における直線性の両方が変調誤差比(MER:Modulation Error Ratio)に影響を及ぼします。MERは、高いデータ・レートを必要とする高次の変調に対応する能力を示す指標です。

何が課題になるのか?

ファイバ・ディープのアーキテクチャにより、ユーザあたりのデータ容量を高めることができます。サービスを提供するグループのサイズを大幅に縮小し、周波数割り当てにおける自由度を高めて、ライン端のS/N比とMERを向上(DOCSIS 3.1において高次変調に不可欠)させるのです。デジタル・ファイバと新しいハードウェアを加入者の比較的近くに配置することで、RPDのノードにWi-Fiのアクセス・ポイントを追加するといった補完的なサービスを提供する機会も得られます。但し、ダウンストリームのアナログ送信チェーンにおいては、設計上の新たな課題がいくつか生じます。

DOCSIS 3.1では、ダウンストリームの上限周波数が1002MHzから1218MHzに拡張されました。これに伴い、更に6MHzのチャンネルを35個使用することに相当する量のデータを送信しなければならなくなります。図3に示すように、チルトのレベルは17dBから21dBに高まります。

新しいシステムでは、既存のシステムとの互換性を維持する必要があります。また、DOCSIS 3.0の最高チャンネル(中心周波数は999MHz)の出力は変更してはなりません(標準で57dBmV)。したがって、中心周波数が1215MHzの最高チャンネルに必要なRF出力は61dBmVになります。ノードの出力ポートの手前に配置する最後の能動部品は、極めて直線性の高いクラスAのパワー・アンプ(パワー・ダブラ型ハイブリッド・アンプ)です。チャンネルの追加、チルトの向上、ケーブル・モデムにおけるS/N比の向上が必要になることから、同アンプに求められる出力信号のレベルは、2倍を超える76.8dBmVのコンポジット・レベルになります。RF出力を増大させるという要求を満たすためには、ハイブリッド・アンプ1個あたりのDCバイアス電力を約10Wから18Wに高める必要があります。場合によっては、DC電源電圧を業界標準の24Vから34Vまで引き上げなければなりませんでした。通常、ノードは4つのRFポートを有し、それぞれにハイブリッド・アンプを用意することになります。一般的には、同軸ケーブルを介して印加される60VのAC電源から電力が供給されるので、大幅な設計変更が必要になりました。特に、温度管理の面では新たな課題に直面することになりました。

DOCSIS 3.1では、より高次のQAMに対応するために、ノードの出力における最も厳しいMERの要件が43dBから48dBに高められました2。このような高いMERを実現しようとすると、DACのクロックの位相ノイズとスプリアスがシステムの性能に影響を及ぼし始める可能性があります。パワー・ダブラは、MERと帯域内/帯域外の歪みの両方に直接影響を及ぼします。パワー・ダブラの性能の中で最も劣化が懸念されるのは非直線性歪みです。これには、高調波歪みと相互変調歪みの両方が含まれます。対応範囲が108MHzから1218MHzまでの数オクターブにわたることから、帯域内には、偶数次と奇数次の高調波が複数存在することになります。DOCSIS 3.0のキャリア(またはそれに相当する信号)が185個存在することに伴い、非常に複雑な組み合わせの相互変調積が生じます。上位チャンネルの出力は、最低位のチャンネルの出力の100倍以上大きく、大きな差周波数積(difference frequency products)が現れる可能性もあります。そのため、チルトも大きな影響を及ぼします。更に、ピーク対平均電力比(PAPR:Peak-to-average Power Ratios)は12dBを超えることがあります。

これらすべての要因が組み合わさることから、パワー・ダブラの設計者に対しては、大きな課題が突き付けられました。帯域幅の拡大、平均出力/ピーク出力の向上、直線性の改善が必要になるからです。ADCA3992は、GaAs/GaNをベースとするハイブリッド・アンプです。このクラスA/プッシュプル型のアンプを使用すれば、帯域幅、RF出力、直線性の要件を満たすことができます。ただ、RFシステムの設計者にとっての課題は、間違いなく消費電力と電力損失を低減することです。650mW(76.8dBmVのコンポジットに相当)のRF出力電力を得るために、約18WのDC入力を使用するとします。その場合、DCからRFへの変換効率はわずか3.6%にしかなりません。

システム・ソリューションとは何か?

ハイブリッド・アンプによって、必要な帯域幅と出力が得られるようになったとします。その場合、ソリューションに最初に求められるのは、出力ポート手前の最後の能動部品であるパワー・ダブラ型ハイブリッド・アンプにクリーンな信号を供給できるようにすることです。そのためには、AD9162のような広帯域に対応する高性能の16ビットDACと、HMC7044のような低位相ノイズ、低放射スプリアスでJESD204Bに準拠するクロック源を使用します。その結果、DOCSIS 3.1の全周波数範囲にわたり、DACの出力において、約52dBのMERを達成することができます。

ソリューションとして2つ目に求められる事柄はもっと複雑です。ソリューションとしては、消費電力を削減しながらパワー・ダブラの出力能力の向上とMERの改善を同時に実現できることが理想です。ただ、これらはほぼ相容れないことだと言えます。つまり、消費電力を削減すると、特定の出力電力におけるMERは悪化します。MERを一定に維持するためには、RF出力をバックオフしなければなりません。エンベロープ・トラッキング(ET:Envelope Tracking)などの手法を適用すれば、効率を高めることは可能です。しかし、非常に帯域幅の広いエンベロープ信号を生成し、ETのプロセスによって生じる大きな歪みを直線化すると、更に多くの課題が生じてしまいます。

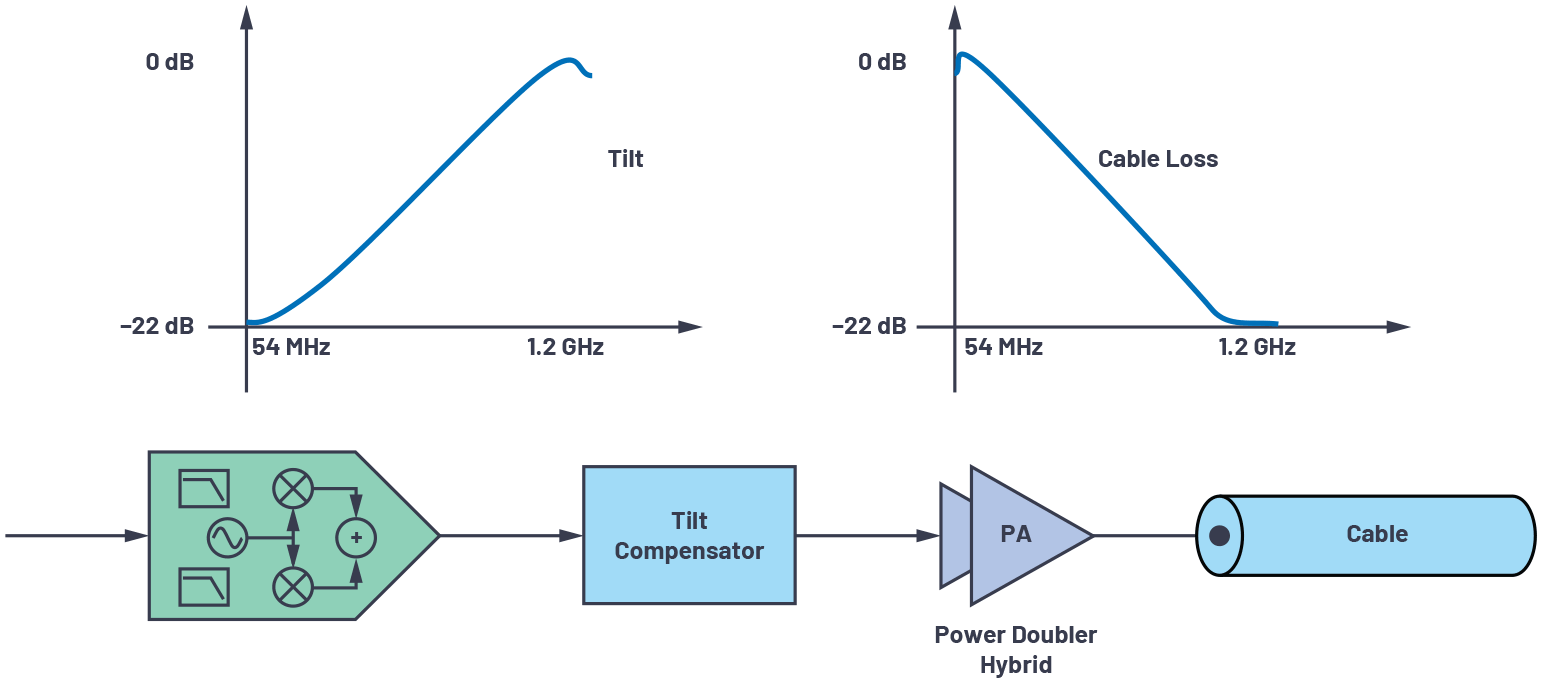

効率の向上とMERの改善を両立可能な最も魅力的なソリューションは、携帯電話の業界でほぼ例外なく採用されているDPDを利用することです。そうすれば、パワー・ダブラ型ハイブリッド・アンプをより効率的に動作させることができます。ただ、非直線領域での動作が多くなるので、信号がアンプに送られる前に、デジタル領域で歪みを事前に補正する必要があります。図4に示すように、DPDでは、アンプに到達する前にデータを整形し、アンプで生じる歪みを打ち消します。それにより、パワー・ダブラが直線性を保って動作できる範囲を拡大します。

直線性を保って動作できる範囲が拡大すると、DPDの自由度が増し、アンプを少ないバイアス電流や低い電源電圧で動作させることができます(消費電力を低減できます)。また、MERとBER(Bit Error Rate)を改善することも可能になります。DPDは、携帯電話システムのインフラで広く使用されています。ただ、DPDをケーブル環境に実装しようとすると、難易度の高い固有の要件が生じます。例えば、極めて広い帯域幅にわたり直線化を実現するための処理を適用する必要があります。また、DPDの実装に必要なデジタル信号処理に伴う消費電力を最小限に抑えなければなりません。更に、強くチルトさせたスペクトルでの動作への対応を図る必要もあります。これらすべてを、ハードウェア、FPGA、ソフトウェアをわずかに変更する(コスト増を最小に抑える)だけで実現しなければなりません。

効率は、アンプを直線性の低い動作領域で駆動することによって改善できます。ただ、そうすると複数の帯域内歪みが生じるので、DPDに固有の課題が生じます。信号の帯域幅が広いことだけでなく、そのスペクトル上の位置が狭く限られている(DCからわずか108MHz)ことも、DPDにおける課題になります。ケーブルで伝送する信号の性質は、ワイヤレス伝送の場合とは大きく異なります。ワイヤレス伝送の場合、必要な信号の帯域幅(例えば60MHz)は、RFの中心周波数(例えば2140MHz)に比べるとはるかに狭くなります。DOCSIS 3.1においてダウンストリームの標準値として割り当てられている108MHz~1218MHzでは、必要な信号帯域幅は1110MHzで、中心周波数は663MHzです。直線性が低いシステムでは、必ず高調波歪みが発生します。ケーブルにおけるDPDで焦点になるのは、帯域内の高調波歪みです。通常のワイヤレス・システムでは、3次と4次の高調波が最も重要になります。なぜなら、他の高調波成分は帯域外に存在するので、従来のフィルタによって除去することが可能だからです。ケーブルを標準的な方法で配備した場合、最低周波数のキャリアに対応する最初の11個の高調波は帯域内に現れます。

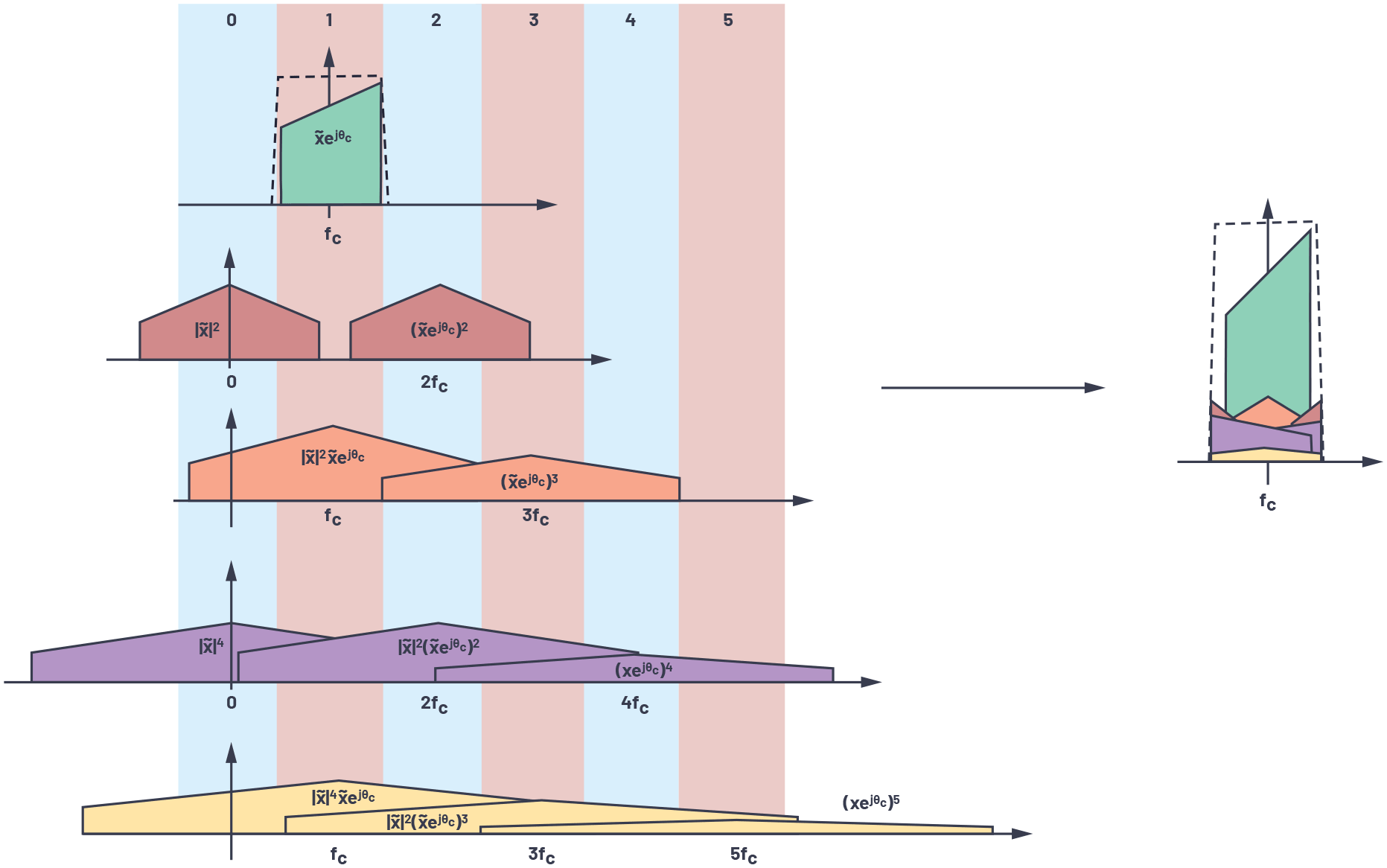

携帯電話システムでは、奇数次の高調波だけが問題になります。それとは対照的に、ケーブル・アプリケーションでは、偶数次と奇数次の項が帯域内に存在し、複数の歪みが重なり合う領域が発生します。このことは、深刻な問題につながります。狭い帯域を前提とした単純なアルゴリズムを使用することができず、DPDソリューションが複雑で高度なものになるからです。DPDソリューションは、高調波歪みの各次数の項に対応できるものでなければなりません。各次数kには、[k/2] + 1個の項が必要です。2次では2項、3次では2項、4次では3項といった具合です。狭帯域のシステムでは、偶数次の項は無視できます。一方、奇数次の項は、対象となる帯域内にそれぞれ1個の項だけを生成します。ケーブル・アプリケーションにおけるDPDでは、奇数次と偶数次の両方の高調波歪みについて考慮しなければなりません。各次数の高調波歪みが、帯域内で複数重なり合って生じる可能性を考慮する必要があります。

高調波歪みの補償

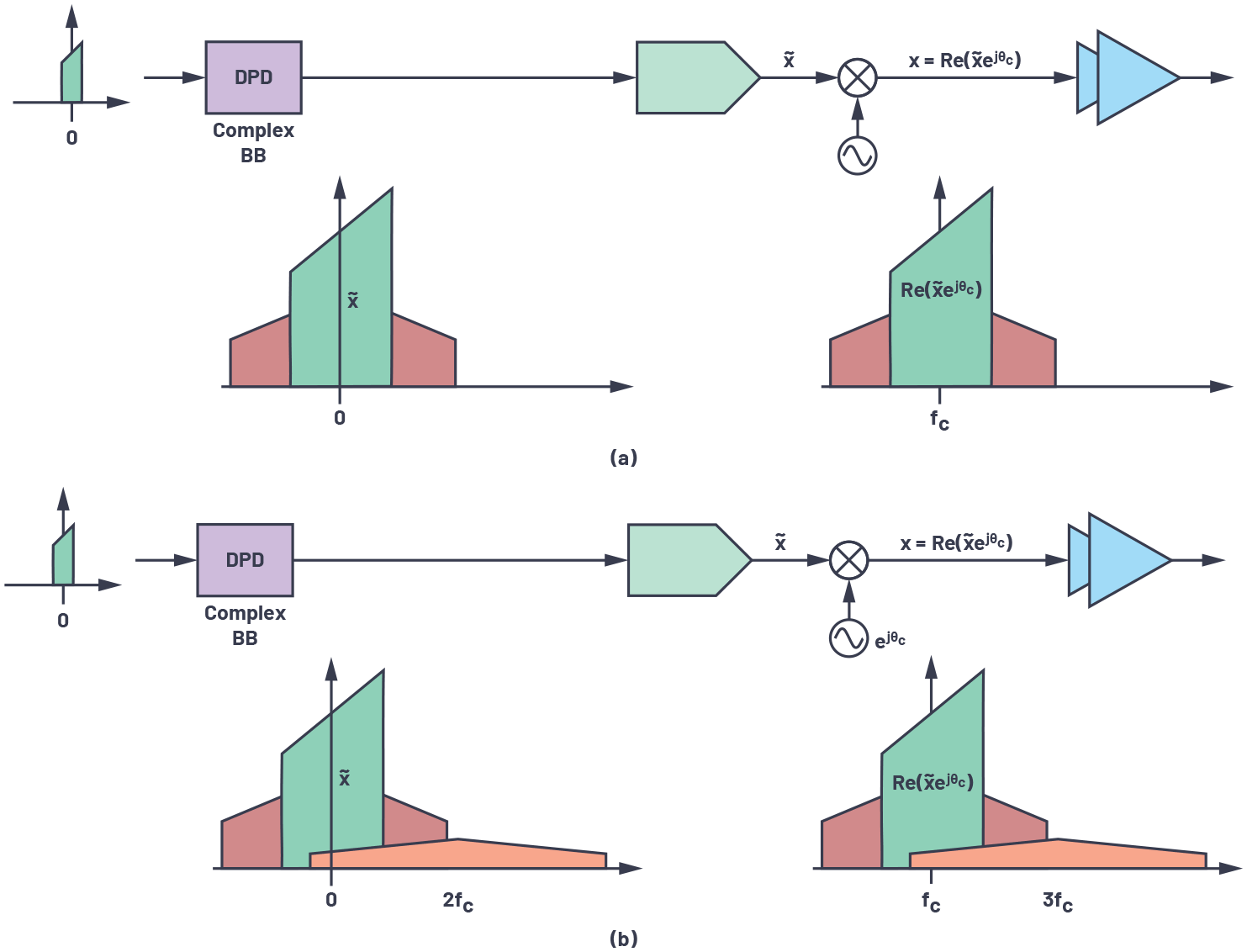

狭帯域に対応する従来のDPDソリューションでは、複素ベースバンドで処理を行います。これについて検討する際には、主にキャリアの周辺に対照的に存在する高調波歪みを対象とします。それに対し、広帯域のケーブル・システムでは、1次の高調波の周辺に位置する項では対称性が維持されますが、高次の高調波成分では対称性は維持されません(図5)。

図6(a)に示すように、狭帯域を対象とする従来のDPDは、複素ベースバンドで処理を行います。この例では、1次の高調波成分だけが帯域内に存在します。そのため、それらのベースバンド表現は、直接RF信号に変換されます。図6(b)のように、広帯域のケーブル・アプリケーションを対象とするDPDについて検討する場合、アップコンバージョンを実施した後のベースバンド表現がRFスペクトルに正しく配置されるように、高次の高調波歪みに対しては、周波数オフセットを加える必要があります。

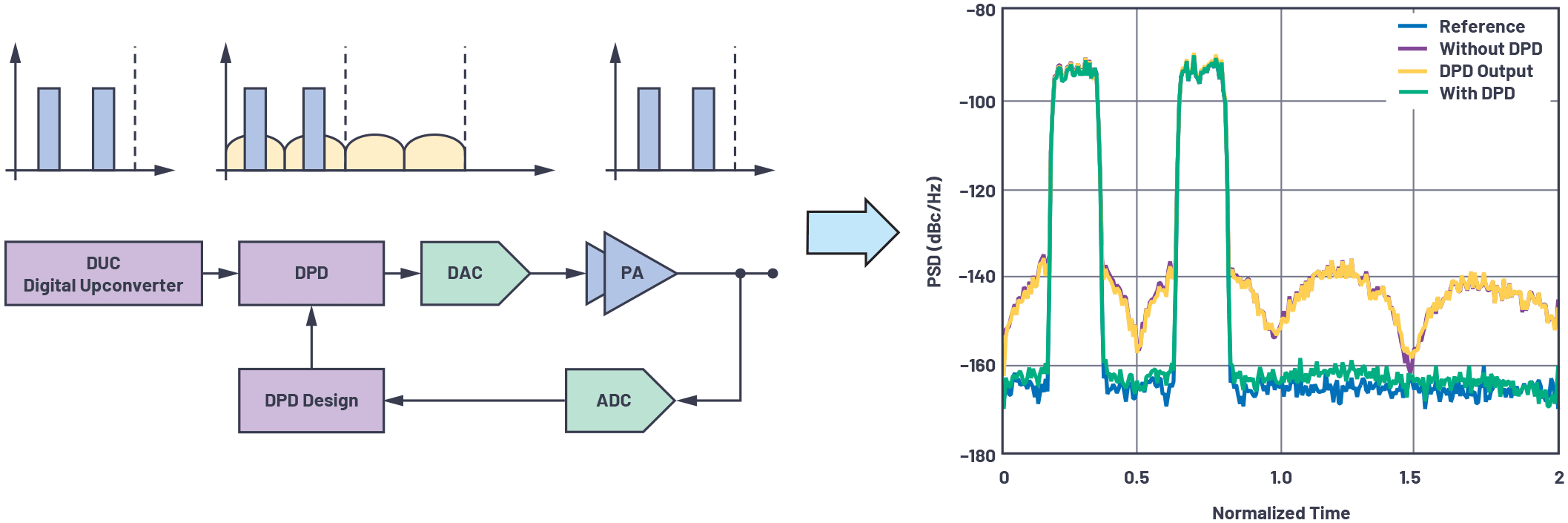

図7に、DPDの実装方法を示しました。理想的な状況では、デジタル・アップコンバータ(DUC)、DPD、DAC、パワー・ダブラの経路には帯域幅の制限はありません。同様に、観測経路上のADCは、全帯域幅を対象としてデジタル化を実行します。図7では、理解しやすくするために、帯域幅の2倍の範囲の信号経路を示しています。携帯電話アプリケーションでは、対象とする範囲を3倍~5倍まで拡大することもあります。理想的な実装では、DPDによって帯域内/帯域外の項が生成され、PAによって生じる歪みが完全にキャンセルされます。正確にキャンセルを実施するためには、対象となる信号帯域幅よりも十分に外側の位置に項が生成されることが重要です。現実の実装では、信号経路に帯域幅の制限が存在し、チルトの特性が現れます。そのため、現実のDPDは理想的な実装の場合とは異なる性能を示します。

アナログ・デバイセズは、ケーブル・アプリケーション向けに適応型のDPDソリューションを開発しました。完全にリアルタイムでクローズドループのソリューションであり、FPGAファブリック内のアクチュエータと、組み込みプロセッサ内のソフトウェア・ベースのアダプテーションで構成されます。その実装には、組み込みプロセッサとしてARM® Cortex®を内蔵した「Intel® Arria® 10 660 FPGA」を使用しています。DPDのIPコアとARMプロセッサで消費される電力は5.3Wです。新世代のFPGAを採用するか、ASICとして実装し直せば、消費電力は3W未満に抑えられるはずです。

評価の結果

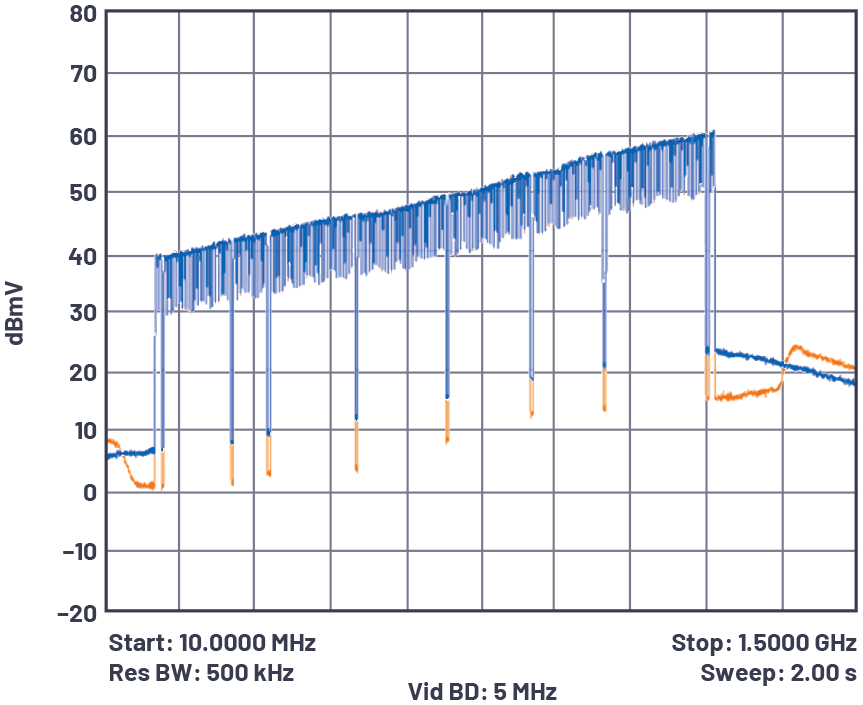

図8に示したのは、ADCA3992の評価結果です。電源電圧は34V、バイアス電流は400mA(DC電力は13.6W)、トータルのコンポジット出力は76.8dBmVという条件で動作させました。

評価に使用した信号は、DOCSIS 3.0に対応する一連のキャリアです。中心周波数は111MHzから1215MHz、チルトは21dBです。少数のギャップが生じており、帯域全体にわたって歪みが現れています。帯域の低域側では約6dB、高域側では8dBを超えるレベルで歪みが改善されていることがわかります。

DPDを使用せず、公称電流値が530mAのパワー・ダブラと比較すると、DC電力の削減量は4.4Wです。4ポートのシステムでは、電力のトータルの削減量は17.6Wになります。FPGAの消費電力である5.3Wを差し引いた値が正味の削減量であり、その値は12.3Wとなります。これは、4ポートのシステムにおいて、消費電力(熱)が72Wから59.7Wに削減されるということを意味します。各ダブラのバイアス電流を350mA(11.9W)までバックオフしても、目標のMERである41dBを満足します。システムにおける電力の削減量として、19.2Wという成果が得られる可能性があります。

まとめ

現在では、モバイル機器によって高速なデータ伝送を行うことが可能になりました。また、あらゆる建物で光ファイバを利用できる可能性も高まっています。しかし、ネットワークのラストマイルでは、旧来の技術に基づく膨大な量の機器が現在も使用されています。しかも、それらの電気的な特性は比較的良好だと言えます。したがって、当面の間は、それらの機器/技術を使用したネットワークが音声/ビデオ/データを消費者に提供するための重要な手段として存在し続けるはずです。ケーブル・ネットワークがDOCSIS 3.1(またはその進化形)に移行する際、周波数帯域の拡大、RF出力の増大、変調精度の向上、電力効率の向上といった要件を満たすためには、従来以上の取り組みが求められることになるでしょう。

DPDは、そうした相反する要件に対処するための手段をもたらしてくれます。しかし、この技術をケーブル・アプリケーションに実装する際には、同アプリケーションに固有の課題を解決しなければなりません。アナログ・デバイセズは、そうした課題に対処できるようにするために、システム・レベルのトータル・ソリューションを開発しました。ソリューションの構成要素としては、ミックスド・シグナルIC(DAC、ADC、クロック)、RFパワー・モジュール(GaN/GaAsのハイブリッド品)、高度なアルゴリズムなどが挙げられます。これらの技術を組み合わせることで、お客様である機器メーカーに対して性能と適応性の高いソリューションを提供することが可能になります。これを採用したお客様は、消費電力とシステム性能のトレードオフを最小限に抑えるために必要な柔軟性を得ることができるでしょう。また、ソフトウェア定義の手法で直線性を得ることが可能なので、全二重(full duplex)、帯域幅の拡張(1794MHzまで)、ETの採用が見込まれる次世代のケーブル技術への移行にも容易に対応できます。

DPDの略図を提供してくれたPatrick Pratt氏に感謝します。

参考資料

1Robert L. Howald「The Fiber Frontier(ファイバ・フロンティア)」 Spring Technical Forum Proceedings、2016年

2「Data-Over-Cable Service Interface Specifications, DOCSIS® 3.1 -- Physical Layer Specification: CM-SPPHYv3.1-I08-151210」CableLabs、2017年5月