Easy, ±5V Split-Voltage Power Supply for Analog Circuits Draws Only 720nA at No Load

Easy, ±5V Split-Voltage Power Supply for Analog Circuits Draws Only 720nA at No Load

by

Jim Drew

2011-07-01

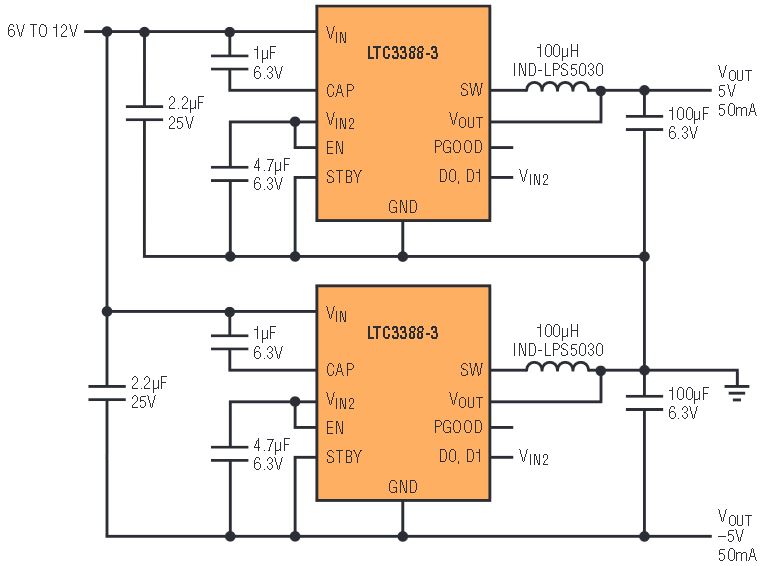

Analog circuits often need a split-voltage power supply to achieve a virtual ground at the output of an amplifier. These split-voltage power supplies are generally low power supplies supporting tens of milliamps of differential current loads. Figure 1 shows such a power supply using two LTC3388-3 20V high efficiency step-down regulators powered from a 6V–12V power source.

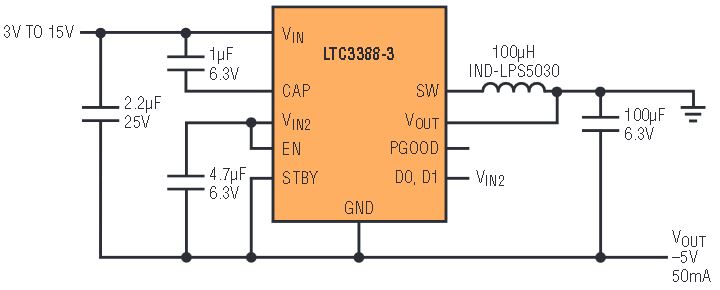

Figure 1. Easy split-voltage power supply.

The positive voltage rail is created by configuring one LTC3388-3 in its standard buck topology while the negative voltage rail is created with a second LTC3388-3 by grounding the VOUT connection and using the GND pin as the negative voltage rail. The negative voltage rail is connected to the exposed pad of this LTC3388-3 and must be isolated from the system ground plane and have sufficient surface area to provide adequate cooling of the LTC3388-3.

The LTC3388-1 and LTC3388-3 are high efficiency step-down regulators that draw only 720nA (typ) of DC current at no load while maintaining output regulation. They are capable of supplying up to 50mA of load current and contain an accurate undervoltage lockout (UVLO) feature to maintain a low quiescent current when the input is below 2.3V. The output voltage is digitally programmable to four output regulated voltages along with a PGOOD status pin that indicates that the outputs are above 92% (typ) of the output setting. The LTC3388-1 can be digitally set to 1.2V, 1.5V, 1.8V or 2.5V while the LTC3388-3 can be set to 2.8V, 3.0V, 3.3V or 5.0V. Both devices are available in a 10-lead MSE or a 3mm × 3mm DFN package.

Operation of the Split-Voltage Supply

Configuring the LTC3388 as a buck regulator creates a positive voltage by ramping the inductor current up to IPEAK (150mA typ) through an internal PMOS switch and then ramping the current down to 0mA through an internal NMOS switch. This action charges the output capacitor to slightly above the regulation voltage at which time the buck regulator enters sleep mode.

As the output voltage decays due to an external load, the buck regulator remains in sleep mode and an internal sleep comparator monitors the output voltage. When the output voltage drops below the regulation voltage, the buck regulator wakes up and the cycle repeats. This hysteretic method of providing a regulated output reduces losses associated with MOSFET switching and maintains an output voltage at light loads. The buck regulator is able to support 50mA of average load current when it is switching.

A negative output voltage rail is created by grounding the VOUT node of the buck regulator. This sets the ground reference connection of the LTC3388 as a negative voltage rail. The voltage from the VIN pin to the negative voltage rail is the sum of the input voltage plus the magnitude of negative voltage rail. This limits the source voltage to 20V (the LTC3388’s VIN(MAX)) minus the magnitude of the negative rail voltage.

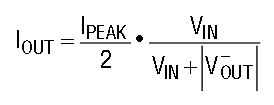

The inductor current is ramped up to IPEAK through the internal PMOS switch as in the buck regulator configuration and then down to zero through the NMOS switch, charging the output capacitor to a negative voltage. This switching action is that of an inverting critical conduction synchronous buck-boost converter. The maximum output current of this configuration is limited by the peak current of the inductor, the input voltage and the magnitude of the output voltage. The expression below estimates the maximum output current available.

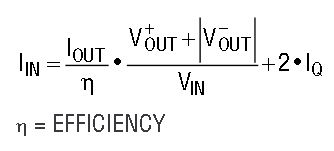

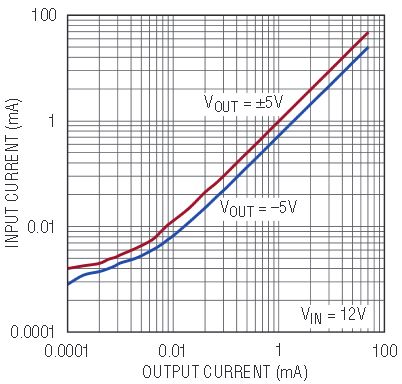

In a split voltage power supply application, the analog circuit is connected between the positive voltage rail and the negative voltage rail. This results in the load current of both regulators to be equal in magnitude. Figure 2 is a plot of the input current versus the output current for the circuit in Figure 1. At very low load currents, <10μA, the effect of the input quiescent current can be seen as a positive offset in the input current. For higher load currents, >100μA, this effect is minimal and the input current is approximately equal to the output current. The expression for the input current may be approximated as:

Figure 2. Input current versus output current for the split voltage power supply of Figure 1 (–5V curve also applies to –5V supply shown in Figure 3).

Negative Voltage Supply

Figure 3 shows the buck-boost configuration creating a negative output voltage rail. In this configuration the input voltage needs only be above the UVLO voltage of 2.5V (typ) to start the regulator. The –5V curve in Figure 2 applies here with a 12V input, as in the previous circuit.

Figure 3. Negative voltage power supply.

Conclusion

An easy-to-implement split-voltage power supply using the LTC3388 yields a low quiescent current, high efficiency solution for powering low current analog circuits that need a virtual ground output. The output voltage of each device is digitally programmable to four output voltages from 1.2V to 5.0V and will support a load current up to 50mA. Each regulator requires only four external capacitors and one inductor, covering minimal board real estate. A PGOOD status pin is provided to indicate when the output is within regulation. The LTC3388-1 and the LTC3388-3 are available in a 10-lead MSE or a 3mm × 3mm DFN package.

关于作者

Jim Drew于2007年加入ADI公司,担任本公司在波士顿马萨诸塞州设计中心的高级应用工程师。他负责特定应用电源IC的应用支持工作。感兴趣的领域包括用于太阳能、能量采集、超级电容充电器和主动电池平衡的电源调节应用。Jim曾担任EMC、Hewlett Packard、Compaq和Digital Equipment Corporation的咨询工程师,负责电源系统开发工作。2017年退休后,他还担任马萨诸塞大学洛厄尔分校的电子工程兼职教授...