XバンドおよびKuバンド用小型フォーム・ファクタ無線の設計

衛星通信、レーダー、EW/SIGINT分野に使用される航空宇宙および防衛用の電子機器の多くは、長い間XバンドとKuバンドの一部あるいは全範囲へのアクセスを必要としてきました。これらのアプリケーションは、無人航空機(UAV)や携帯無線機のような、よりポータブルなプラットフォームへ移行しつつあるため、非常に高い性能レベルを維持しながら、XおよびKuバンドで動作する、小型フォーム・ファクタで低消費電力の新しい無線設計を開発することが極めて重要です。この記事では、システムの仕様に影響を与えることなく、レシーバーとトランスミッタ両方のサイズ、重量、消費電力、そしてコストを大幅に削減する高周波数IFアーキテクチャの概要を示します。結果として得られるプラットフォームは既存の無線設計よりも高いモジュール性を有し、柔軟で、ソフトウェア定義部分の多いものとなります。

はじめに

近年のRFシステムには、周波数範囲の拡大とサイズの小型化と同時に、より広い帯域幅で、より高性能、低消費電力であることが求められるようになっています。この傾向が技術革新の原動力となり、従来を上回るRFコンポーネントの統合が可能になってきました。この傾向を促進している要素は数多くあります。

衛星通信システムでは、まとめると1日あたりテラバイト単位にも及ぶ量のデータの送受信に対応するためには、最大4Gbpsのデータ・レートが必要と見込まれています。この要求が、KuバンドとKaバンドで動作するシステムの実現に向けた取り組みを加速させています。これは、この周波数帯では広い帯域幅と高いデータ・レートを実現しやすい、という事実によります。このような需要は、チャンネル密度が高くなり、チャンネルあたりの帯域幅が広がることを意味します。

性能向上が求められるもう1つの分野は、EWと信号インテリジェンス(SIGINT)です。このようなシステムのスキャン・レートは増大し続けており、迅速に調整できるPLLと広い帯域幅をカバーするシステムの必要性が増しています。さらなる小型化、軽量化、低消費電力(SWaP)、そしてより高集積のシステムへの取り組みは、現場でのハンドヘルド・デバイスの使用や、大型の固定システムでのチャンネル密度増大に対する強い要求から生じたものです。

フェーズド・アレイの進歩は、RFシステムを1個のチップに集積化できたことも貢献しています。集積化によるトランシーバーの小型化が進むのに伴い、トランシーバー専用のアンテナ素子を組み込めるようになり、更にそれによって、アナログ・ビームフォーミングからデジタル・ビームフォーミングへの移行が可能になりました。デジタル・ビームフォーミングでは、1つのアレイから同時に複数のビームを追跡することができます。フェーズド・アレイ・システムには、気象レーダー、EWアプリケーション、指向性通信など、無数のアプリケーションがあります。比較的低い周波数の信号環境が非常に混雑したものとなっていることから、これらのアプリケーションの多くでは、より高い周波数への移行が避けられない状況になっています。

本稿では、AD9371をIFレシーバーおよびトランスミッタとして使用することを基本とする高集積アーキテクチャを使用してこれらの課題に対処し、IF段のすべてとその関連コンポーネントをなくすことを可能にします。ここでは、従来型システムとここで提案するアーキテクチャの比較、および標準のプロセスを通じてこのアーキテクチャを実装する方法を例を用いて説明します。特に、集積化トランシーバーを使用することによって、標準的なスーパーヘテロダイン型トランシーバーでは望めない、かなり高度な周波数プランニングが可能になります。

スーパーヘテロダイン・アーキテクチャの概要

スーパーヘテロダイン・アーキテクチャは高い性能を実現できることから、長年にわたり最良のアーキテクチャと見なされてきました。通常、スーパーヘテロダイン・アーキテクチャは、A/Dコンバータ(ADC)への入力を生成する1つまたは2つのミキシング段で構成されます。

図1. 従来のスーパーヘテロダイン方式によるXおよびKuバンドの受信および送信シグナル・チェーン。

代表的なスーパーヘテロダイン・トランシーバー・アーキテクチャを図1に示します。最初の変換段は、入力RF周波数を帯域外スペクトラムにアップコンバートまたはダウンコンバートします。最初のIF(中間周波数)の値は、周波数とスプリアスのプランニング、およびミキサーの性能とRFフロント・エンドに使用できるフィルタによって決まります。更にこの最初のIFは、ADCがデジタル変換できるように、より低い周波数に変換されます。ADCの能力は素晴らしい進歩を遂げ、より高い帯域幅を処理できるようになりましたが、現時点で最適性能を得ることのできる上限は約2GHzです。これよりも高い入力周波数では、性能と入力周波数のトレードオフを考える必要があります。また、入力レートを高くするには高いクロックレートが必要になり、それによって消費電力が増大するという事実も考慮しなければなりません。

ミキサーの他にもフィルタ、アンプ、ステップ減衰器があります。フィルタは、不要な帯域外(Out of Band:OOB)信号を除去するために使われます。これらの信号を抑制しないと、スプリアスが発生して目的の信号に重なり、復調が非常に困難になるか、まったく不可能になるおそれがあります。アンプはシステムのノイズ指数とゲインを設定し、小信号を受信するために適切な感度を提供しますが、ADCが過飽和になるほどの高い感度ではありません。

注意すべきもう1つの点は、このアーキテクチャでは、ADCのアンチエイリアシングに関する厳しいフィルタリング条件を満たすために、多くの場合は表面弾性波(SAW)フィルタが必要になるということです。SAWフィルタはロールオフが急峻で、これらの条件を満たすことができます。ただし、同時にかなりの遅延とリップルが発生します。

Xバンドのスーパーヘテロダイン・レシーバーの周波数プランの一例を図2に示します。このレシーバーでは、8GHzから12GHzまでの周波数を、帯域幅200MHzで受信することが求められます。調整可能なローカル発振器(LO)を使って必要なスペクトラムをミキシングし、5.4GHzのIFを生成します。更にこの5.4GHzのIFを5GHzのLOとミキシングして、最終的に400MHzのIFを生成します。最終的なIFの範囲は300MHz~500MHzで、これは多くのADCが良好に動作する周波数範囲です。

図 2. Xバンド・レシーバーの周波数プラン例

レシーバーの仕様−重要な点

よく知られたゲイン、ノイズ指数、3次インターセプト・ポイントなどの仕様に加えて、あらゆるレシーバー・アーキテクチャの周波数プランニングに影響する代表的な仕様として、イメージ除去、IF除去、自己生成スプリアス、LO放射などがあります。

- イメージ・スプリアス—LOと組み合わされてIF内にトーンを生成する対象帯域外のRF。

- IFスプリアス—ミキサーの前にあるフィルタを通過して、IF内にトーンとして出現するIF周波数のRF。

- LO放射—LOからレシーバー・チェーンの入力コネクタに漏れ出すRF。LO放射は、受信のみの動作時でも検出することができます(図3参照)。

図 3. フロント・エンドを通じて漏れ出すLO放射。

-

自己生成スプリアス—レシーバー内のクロックまたはローカル発振器のミキシングによって生じるIFのスプリアス。

イメージ除去仕様は、第1および第2ミキシング段の両方に適用されます。XバンドとKuバンドの代表的なアプリケーションでは、最初のミキシング段の中心を5GHz~10GHzの範囲のハイIF付近に置くことができます。図4に示すように、イメージはFtune + 2 × IFの範囲に発生するという事実により、ここでは

ハイIFが望ましい選択です。IFが高いほど、イメージ・バンドの位置は更に遠くなります。このイメージ・バンドは、最初のミキサーに達する前に除去する必要があります。そうしないと、この範囲内の帯域外エネルギーが最初のIFにスプリアスとして出現します。これが、通常2つの段が使われる主な理由の1つです。ミキシング段を1つだけにすると、IFの範囲が数百MHzの場合、イメージ周波数をレシーバーのフロント・エンドで除去することが非常に難しくなります。

図 4. IFへのイメージ・ミキシング。

最初のIFを2つめのIFにダウンコンバートする際には、2つめのミキサーにもイメージ・バンドが存在します。2つめのIFは周波数がより低いので(数百MHz~2GHzのどこか)、最初のIFフィルタのフィルタリング要件はかなり変化します。2つめのIFが数百MHzという標準的なアプリケーションでは、高周波数の最初のIFでのフィルタリングが非常に難しくなる可能性があるので、大きなカスタム・フィルタが必要です。多くの場合、これがシステム内で最も設計の難しいフィルタとなります。周波数が高く、通常は除去が必要な範囲も狭いからです。

イメージ除去に加えて、ミキサーから受信入力コネクタへ戻るLO電力レベルも、フィルタで積極的に除去する必要があります。これは、放射された電力によってユーザを検知できないようにする役割を果たします。これを実現するために、LOはRFパスバンドから十分に外れた位置に置き、適切なフィルタリングを行えるようにします。

ハイIFアーキテクチャの導入

最新の集積化トランシーバー製品には、2つの受信チャンネルと2つの送信チャンネルを持つ300MHz~6GHzのダイレクト・コンバージョン・トランシーバーであるAD9371が使用されています。受信および送信帯域幅は8MHz~100MHzの範囲で調整可能で、周波数分割二重(FDD)動作または時分割二重(TDD)動作用に構成可能です。このデバイスは12mm2のパッケージに組み込まれており、TDDモードで約3W、FDDモードで約5Wの電力を消費します。直交誤差補正(QEC)キャリブレーションの進歩によって、75dB~80dBのイメージ除去が実現されています。

図 5. AD9371ダイレクト・コンバージョン・トランシーバーのブロック図

集積化トランシーバーICの性能向上は、新しい可能性を開きました。AD9371には、2つめのミキサー、2つめのフィルタとアンプ、可変減衰ADC、およびデジタル・フィルタリング機能とシグナル・チェーンのデシメーション機能が組み込まれています。このアーキテクチャでは、300MHz~6GHzの調整範囲を持つAD9371を3GHz~6GHzの周波数に合わせて調整し、最初のIFを直接受信することができます(図6参照)。ゲインが16dB、NFが19dB、そして5.5GHzで40dBのOIP3性能を持つAD9371は、IFレシーバーとして理想的な仕様を備えています。

図6. AD9371をIFレシーバーに使用したXまたはKuバンドのトランシーバー

内蔵トランシーバーをIFレシーバーとして使用することで、スーパーヘテロダイン・レシーバーのようにイメージが2段目のミキサーを通過してしまうおそれもなくなります。これは、最初のIFストリップに必要とされるフィルタリングの必要性を大幅に軽減します。ただし、トランシーバー内の二次的な影響に対応するために、やはり何らかのフィルタリングを行う必要はあります。したがって最初のIFストリップでは、これらの影響を排除するために、最初のIF周波数の2倍の周波数でフィルタリングを行う必要があります。しかしこれは、数百MHz近くになることもある2つ目のイメージとLOのフィルタリングよりは、はるかに容易なタスクです。これらのフィルタリング条件には、通常、低コストの市販LTCCフィルタで対処できます。

この設計はシステムに高いレベルの柔軟性も提供し、様々なアプリケーションに容易に再利用できます。柔軟性を提供している要因の1つが、IF周波数の選択です。IF選択に用いられる一般的な経験則は、フロント・エンドのフィルタリング通過時の必要スペクトラム帯域幅よりも1GHz~2GHz高い範囲から選択する、という方法です。例えば、設計者の希望するフロント・エンド・フィルタ通過時のスペクトラム帯域幅が17GHz~21GHzの4GHzの場合は、5GHz(4GHzの必要帯域幅より1GHz高い値)にIFを設定します。これにより、フロント・エンドのフィルタリングを実現可能なものとすることができます。必要な帯域幅が2GHzだけの場合は、3GHzのIFを使用します。更に、AD9371はソフトウェアによる定義が可能なので、コグニティブ無線アプリケーションでは別途処理を行うことなくIFを容易に変更でき、ブロッキング信号も検出時点でこれを回避することができます。AD9371の帯域幅は8MHzから100MHzまで容易に調整できるので、対象信号付近での干渉を防ぐことができます。

ハイIFアーキテクチャの高い集積度により、レシーバーのシグナル・チェーンは、同等のスーパーヘテロダイン・アーキテクチャと比較して50%の必要スペースを削減しながら、消費電力も30%削減しています。更に、ハイIFアーキテクチャを採用したレシーバーは、スーパーヘテロダイン・アーキテクチャのレシーバーよりも高い柔軟性を備えています。このアーキテクチャは、性能を犠牲にすることなくサイズを小型化することが求められる低SWaP市場向け製品の実現を可能にします。

ハイIFアーキテクチャによるレシーバーの周波数プランニング

ハイIFアーキテクチャの利点の1つは、IFを調整できることです。これは、干渉スプリアスを回避する周波数プランを作成しようとする際に、特に有利です。ミキサー内で受信信号とLOがミキシングされて、IFバンド内で必要とされるトーンではないm × nスプリアスが発生した場合、干渉スプリアスが生じる可能性があります。

ミキサーは、式m × RF ± n × LOに従って出力信号とスプリアスを生成します。ここで、mとnは整数です。レシーバー信号は、IFバンド内に含まれるm × nスプリアスを生成しますが、場合によっては、必要とされるトーンが特定の周波数でクロスオーバー・スプリアスを発生させる可能性もあります。

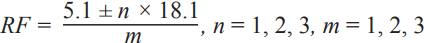

例えば、図7に示すように、5.1GHzのIFで12GHz~16GHzの周波数を受信するように設計されたシステムを考えると、帯域内にスプリアスを発生させるm × nイメージ周波数は、以下の式で求めることができます。

図7. 12GHz~16GHzレシーバーとトランスミッタのハイIFアーキテクチャ

この式の「RF」はミキサー入力のRF周波数で、これがIF内にトーンを発生させます。1つ例を使ってこれを示します。レシーバーが13GHzに調整されているとすると、これはLO周波数が18.1GHzであることを意味します(5.1GHz + 13GHz)。これらの値を前出の式に当てはめ、mとnを0~3の範囲とすると、次に示すRFの式が得られます。

結果を下表に示します。

表1. 18.1GHz LOに対するM × Nスプリアスの表| m | n | RFsum (GHz) | RFdif (GHz) |

| 1 | 1 | 23.200 | 13.000 |

| 1 | 2 | 41.300 | 31.100 |

| 1 | 3 | 59.400 | 49.200 |

| 2 | 1 | 11.600 | 6.500 |

| 2 | 2 | 20.650 | 15.550 |

| 2 | 3 | 29.700 | 24.600 |

| 3 | 1 | 7.733 | 4.333 |

| 3 | 2 | 13.767 | 10.367 |

| 3 | 3 | 19.800 | 16.400 |

この表の最初の行(黄色のハイライト表示)が必要とされる13GHz信号で、これはミキサー内の積1 × 1によって生成されます。他のハイライト表示されたセルは問題となりそうな帯域内周波数を示しており、これらは帯域内にスプリアスとして現れる可能性があります。例えば、15.55GHzの信号は、必要とされる12GHz~16GHzの範囲内にあります。入力の15.55GHzのトーンはLOとミキシングされて5.1GHzのトーンを生成します(18.1 × 2 – 15.55 × 2 = 5.1GHz)。ハイライト表示されていない他の行も問題となる可能性がありますが、これらは帯域外にあるので、入力バンドパス・フィルタで除去できます。

スプリアスのレベルは、いくつかの要素に依存します。メインとなる要素は、ミキサーの性能です。ミキサーは本質的に非線形デバイスなので、内部で生成される高調波が多数存在します。出力のレベルは、ミキサー内部のダイオードのマッチングがいかにうまくとれているか、また、ミキサーのスプリアス性能がどの程度、最適化されているかに応じて決定されます。通常、データシートにはミキサーのスプリアス・チャートが含まれており、これらのレベルを決定する際の助けとなります。ミキサー・スプリアス・チャートの例を表2に示します。これはHMC773ALC3Bのチャートです。このチャートは、必要とされる1 × 1トーンを基準として、スプリアスのdBcレベルの仕様を規定しています。

| n × LO | |||||||

| 0 | 1 | 2 | 3 | 4 | 5 | ||

| m × RF | 0 | — | 14.2 | 35 | 32.1 | 50.3 | 61.4 |

| 1 | –1.9 | — | 17.7 | 31.1 | 32.8 | 61.2 | |

| 2 | 83 | 55.3 | 60 | 59.6 | 6 73.7 | 87.9 | |

| 3 | 82.6 | 86.1 | 68 | 68.5 | 61.9 | 85.9 | |

| 4 | 76 | 86.7 | 82.1 | 77.4 | 74.9 | 75.8 | |

| 5 | 69.3 | 74.7 | 85.3 | 87 | 85.1 | 62 | |

このスプリアス・チャートと表1で行った分析の延長から、m × nイメージ・トーンがレシーバーとどのように干渉するのか、また、そのレベルはどの程度なのかという点について、その全容を知ることができます。また、図8に示すものと同様の出力を使って、スプレッド・シートを作成することができます。

図 8. 12GHz~16GHzレシーバーのm × nイメージ

図8の青で示された部分が、必要とされる帯域幅です。各ラインは、様々なm × nイメージとそのレベルを示しています。このチャートから、干渉に関する要求事項を満たすには、ミキサーの前段にどのようなフィルタリングが必要かが容易に分かります。この場合は、帯域内に含まれ、フィルタで除去できないイメージ・スプリアスがいくつかあります。それでは、ハイIFアーキテクチャの柔軟性によって、これらのスプリアスのいくつかをどのように回避できるかという点に目を向けてみましょう。スーパーヘテロダイン・アーキテクチャでは、このような対応は望めません。

レシーバー・モードでの干渉源回避

図9のチャートに、範囲が8GHz~12GHz、デフォルトIFが5.1GHzの、2つの同様の周波数プランを示します。このチャートはミキサー・スプリアスを別の形で表したもので、前の図がスプリアス・レベルを示していたのに対し、こちらは中心調整周波数とm × nイメージ周波数の関係を示しています。チャートに太線で示した1:1の対角線は、必要な1 × 1のスプリアスを示しています。グラフ上の他の線は、m × nイメージを表しています。この図の上側は、IF調整に柔軟性がない状態での特性を表しています。この場合、IFは5.1GHzに固定されています。調整周波数が10.2GHzの位置で、2 × 1イメージ・スプリアスの線と必要信号の線が交差しています。これは、10.2GHzに調整した場合は、その付近の信号が必要信号の受信をブロックする可能性があることを意味します。下側のプロットは、柔軟なIF調整によるこの問題へのソリューションを示しています。この場合は、9.2GHz付近でIFが5.1GHzから4.1GHzに切り替わっています。これがクロスオーバー・スプリアスの発生を防ぎます。.

図 9. IFを調整しない場合のm × nクロスオーバー・スプリアス(上)と、IFを調整してクロスオーバーを回避した場合(下)

これは、ハイIFアーキテクチャによって信号ブロッキングをどのように回避できるかを示す単純な例に過ぎません。インテリジェント・アルゴリズムと組み合わせて干渉を特定し、新たなIF周波数の可能性を計算する場合、あらゆるスペクトラム環境に適応させ得るレシーバーを作成するために考えられる方法は数多くあります。これは難しい作業ではなく、所定の範囲(通常は3GHz~6GHz)に適したIFを決定し、その周波数を基にLOを再計算してプログラムするだけです。

ハイIFアーキテクチャによるトランスミッタの周波数プランニング

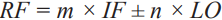

レシーバーの周波数プランニング同様、ハイIFアーキテクチャの柔軟な特性の利点を利用して、トランスミッタのスプリアス性能を改善することができます。レシーバー側では周波数成分を予測しにくい傾向が多少ありますが、送信側ではトランスミッタの出力におけるスプリアスを容易に予測することができます。このRF成分は次式で予測できます。

ここで、IFは予め定義されていてAD9371の調整周波数によって決定され、LOは目的の出力周波数によって決定されます。

ミキサー・チャートは、レシーバー・チャンネルに関して作成したものと同様のものを、トランスミッタ側でも作成することができます。その一例を図10に示します。このチャートにおける最大のスプリアスはイメージとLO周波数で、これはミキサー後段のバンドパス・フィルタを使って、必要なレベルまで減らすことができます。スプリアス出力が近傍のレシーバーの感度を低下させる可能性があるFDDシステムでは、帯域内スプリアスが問題となることがありますが、これはIF調整による柔軟性が効果を発揮する部分でもあります。図10の例で5.1GHzの静的IFを使用した場合は、15.2GHz付近でトランスミッタの出力にクロスオーバー・スプリアスが発生します。このクロスオーバー・スプリアスは、14GHzの調整周波数でIFを4.3GHzに調整することによって回避できます。これを図11に示します。

図 10. フィルタリングなしでの出力スプリアス

図 11. 静的IFによるクロスオーバー・スプリアスの発生(上)と、クロスオーバー・スプリアスを回避するためのIF調整(下)

設計例—広帯域FDDシステム

このアーキテクチャで実現できる性能を示すために、市販のアナログ・デバイセズ製部品を使ってレシーバーおよびトランスミッタからなるFDDシステムを試作し、12GHz~16GHzの受信帯域と8GHz~12GHzの送信帯域で動作するように構成しました。性能データの収集には、5.1GHzのIFを使用しています。また、LOは、受信チャンネルで17.1GHz~21.1GHz、送信チャンネルで13.1GHz~17.1GHzの範囲に設定しました。この試作システムのブロック図を図12に示します。この図では、XおよびKuコンバータ・ボードが左側、AD9371評価用カードが右側に示されています。

図12. XおよびKuバンドのレシーバーとトランスミッタのFDD試作システム

ゲイン、ノイズ指数(NF)、IIP3のデータは、受信ダウンコンバータ上で収集しました。これを図13(上)に示します。全体的なゲインは、約20dB、NFは約6dB、IIP3は約−2dBmでした。イコライザを使用すれば、ある程度の追加的なゲイン・レベリングを行うことができます。あるいは、AD9371の可変減衰器を使用してゲインのキャリブレーションを行うことができます。

図 13. Kuバンド・レシーバーのデータ(上)と、Xバンド・トランスミッタのデータ(下)

トランスミッタのアップコンバータでも測定を行い、そのゲイン、0 P1dB、およびOIP3を記録しました。このデータを周波数に対してプロットしたものが図13(下)です。ゲインは約27dB、P1dBは約22dBm、OIP3は約32dBmでした。

このボードを集積化トランシーバーと組み合わせた場合、その全体的な送受信仕様は表3に示すようなものになります。

表3. システム全体の性能| Rx、12GHz~16GHz | Tx、8GHz~12GHz | |||

| ゲイン | 36 dB | 出力電力 | 23 dBm |

|

| ノイズ指数 | 6.8 dB | ノイズ・フロア | –132 dBc/Hz | |

| IIP3 | –3 dBm | OIP3 | 31 dBm | |

| Pin、max(AGCなし) | –33 dBm | OP1dB | 22 dBm | |

| 帯域内m × n | –60 dBc | 帯域内スプリアス | –70 dBc | |

| 消費電力 | 3.4 W | 消費電力 | 4.2 W |

全体としてのレシーバー性能は、スーパーヘテロダイン・アーキテクチャと同じですが、消費電力は大幅に減少します。同等のスーパーヘテロダイン設計では、レシーバー・チェーンで5W以上の電力を消費します。更に、試作ボードは小型化を優先することなく作成されています。適切なPCBレイアウト手法を使用した上でAD9371をダウンコンバータと同じPCB上に組み込めば、ソリューションの全体的なサイズをわずか4~6平方インチに収めることができます。これは、8~10平方インチ近くになる同等のスーパーヘテロダイン・ソリューションよりも大幅な小型化が可能であることを示しています。更に、マルチチップ・モジュール(MCM)やシステム・イン・パッケージ(SiP)などの先進のパッケージング技術を使用すれば、より小型化が可能です。これらの先進的技術を利用することにより、サイズは2~3平方インチにまで縮小可能です。

まとめ

本稿では、ハイIFアーキテクチャという実行可能な代替アーキテクチャを示しました。これを使用することによって、従来の手法に比べてSWaPを大幅に改善することができます。ここでは、まずスーパーヘテロダインの概要を示し、レシーバー設計における重要な仕様について説明しました。続いてハイIFアーキテクチャを紹介し、フィルタリング条件と集積度に関する利点を示し、全体的な部品数を削減できることを説明しました。説明には、周波数プランの作成や、調整可能IFを利用するレシーバーの干渉信号回避に関する詳細な方法が含まれています。出力スプリアスを減らすことが目標となる送信側に関しては、帯域内スプリアスを回避する方法と、出現が予想されるすべての出力スプリアス成分を予測するためのアプローチを示しました。

このアーキテクチャを可能にしたのは、近年における集積化ダイレクト・コンバージョン・レシーバーの急速な進歩です。AD9371の出現は、その高度なキャリブレーションと高い集積度によって、より高い性能の実現を可能にしました。このアーキテクチャは、近い将来、低SWaP市場において特に重要性を増すことが予想されます。