高電圧フェーズ・ロック・ループ周波数シンセサイザ回路のVCOを駆動する

フェーズ・ロック・ループ(PLL)回路は電圧制御発振器(VCO)と位相検出器を組み合わせた帰還システムで、発振器の信号が、適切な周波数と位相で、印加された周波数変調信号または位相変調信号に追随するように構成されます。PLLは、固定された低周波数信号から安定した高い出力周波数を生成する必要がある場合や、急速な周波数変化が必要な場合に使われます。代表的な用途としては、高周波、電気通信、測定などの技術分野において、フィルタ、変調、復調、周波数合成を行う場合が挙げられます。

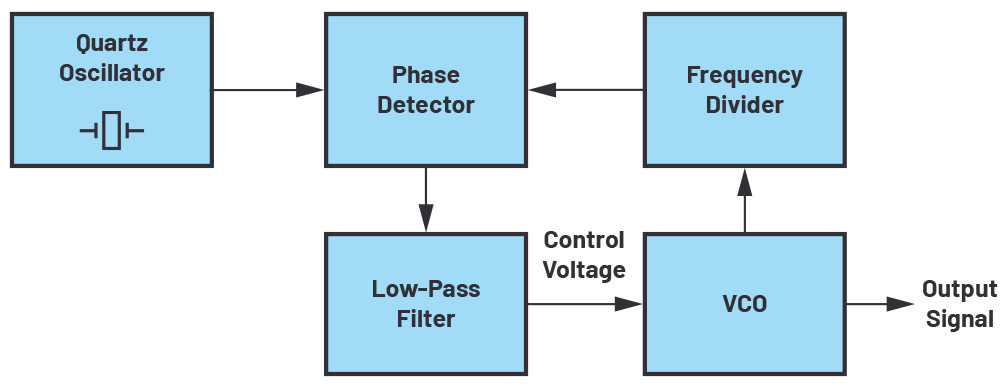

PLLに基づく周波数シンセサイザのブロック図を図1に示します。VCOは出力信号を生成します。この信号はPLLによって設定された周波数に維持され、リファレンス周波数にロックされます。通常、このリファレンス周波数は、極めて高精度の水晶発振器によって供給されます。フェーズ・ロック・ループ回路の帰還パス内にある位相検出器の前には、調整可能な係数分だけVCO周波数を下げる分周器が置かれています。

図1 フェーズ・ロック・ループのブロック図.

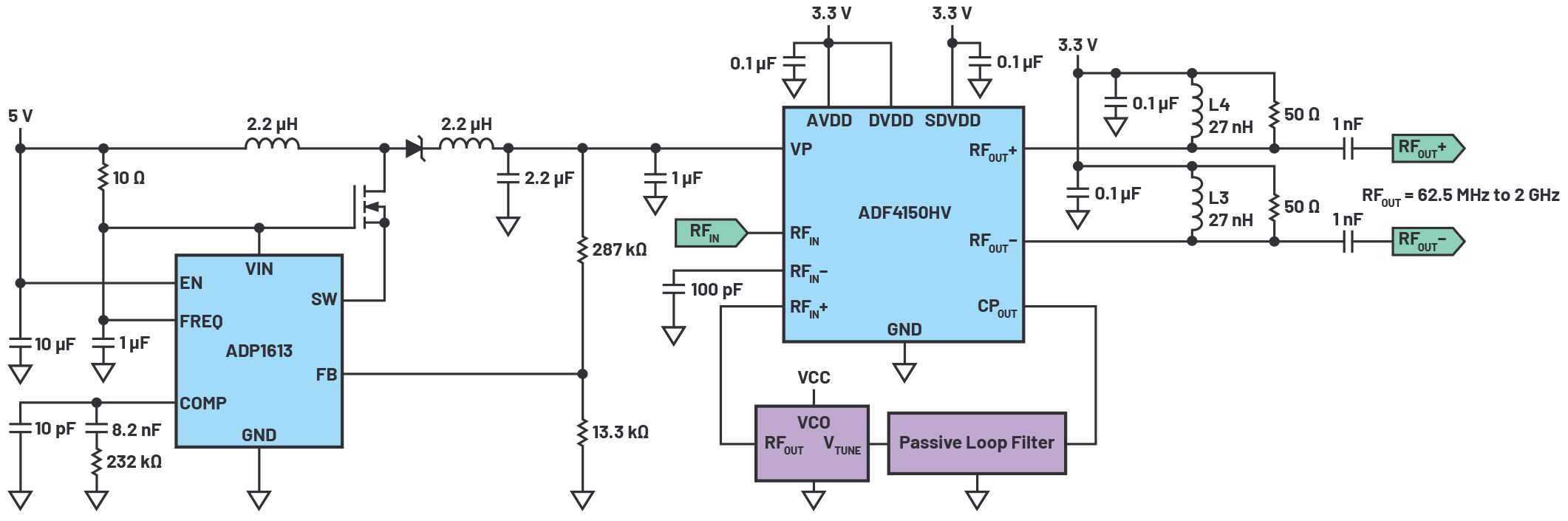

VCOには、入力電圧に応じて容量が変化するバラクタ・ダイオードなどの、調整可能なチューニング素子が含まれています。したがって、このPLL回路はVCO用の帰還制御システムの一種です。VCOに必要な入力、つまり制御電圧は、多くの場合、PLL回路に使用できる電源電圧より高くなります。電源電圧は通常3.3Vか5Vですが、必要な周波数によっては、20Vを超える電圧をVCOに加えなければならない場合があります。より広範な周波数を生成するには、チューニング範囲の広いVCOを使用する必要があります。ギガヘルツ範囲のVCOに対応した回路の例を、簡略化して図2に示します。

図2 ADF4150HV用高電圧チャージ・ポンプ電源の簡略回路図

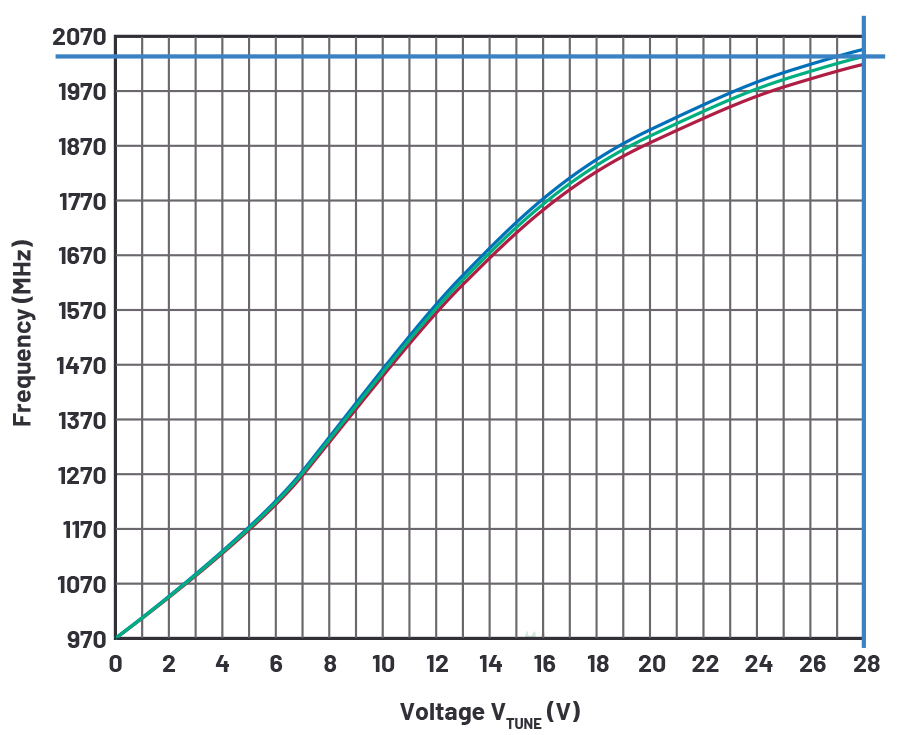

VCOには、Synergy Microwave CorporationのDCYS100200-12を使用できます。図3のグラフに示すように、このVCOは28V(VTUNE)で2GHzの周波数を生成できます。

図3 DCYS100200-12の制御電圧と周波数の関係1

高い制御電圧を生成する方法は複数あります。その1つがアクティブ・ループ・フィルタを使用することで、これは基本的に高速アンプとローパス・フィルタで構成され、位相検出器からの出力パルス(CPOUT)をクリーンなDC電圧にします。これに代わる方法として、チャージ・ポンプ内蔵のPLL周波数シンセサイザを使用することができます。このようなシンセサイザの例としてアナログ・デバイセズのADF4150HVがあります。このデバイスにはアクティブ・ループ・フィルタを追加する必要がありません。いずれのソリューションも高電圧の電源が必要ですが、ADF4150HVを使用すれば部品数を減らすことができます。また、アクティブ・フィルタ・アンプによって生じる歪みと位相ノイズも回避できます。更に、ADF4150HVを使用すれば、フラクショナルNまたはインテジャーNフェーズ・ロック・ループ周波数シンセサイザを実装することができます。この結果、VCO周波数を1、2、4、8、または16分周することが可能で、最小31.25MHzの出力周波数を生成できます。

ADF4150HVの内蔵チャージ・ポンプに必要な高電圧は、DC/DCコンバータADP1613を使って、PLL性能を犠牲にすることなく生成することができます。ADP1613は、最大20Vの出力電圧を容易に得られるようにパワー・トランジスタを内蔵した、効果的なスイッチング・レギュレータです。外付け部品、特に外部パワー・トランジスタを追加することによって、より高い出力電圧を生成することも可能です。ADP1613のスイッチング周波数は、650kHz~1.3MHzの範囲で調整できます。これによって過渡応答が改善され、ノイズ・フィルタリングも単純化されます。一般に、PLLループ・フィルタによってスイッチング・ノイズを低減するために、1MHz以上のスイッチング周波数を選択することが推奨されます。

ADF4150HVを使用したフェーズ・ロック・ループ周波数シンセサイザ回路は、内蔵RF分周器を使用することによって超高帯域のPLL機能を実現し、62.5MHz~2GHzの周波数範囲に対応することを可能にします。同じPLLハードウェア設計で、システム内の多数の異なるハードウェア・プラットフォーム用に様々な周波数を生成できます。ただし、様々なVCOタイプ用の設計が求められる場合は、その設計に対応するループ・フィルタを採用するのが合理的な方法です。そうすることによって、信頼性の高いフェーズ・ロック・ループ動作を確保できます。出力周波数と、それに対応するより高い出力を、比較的広い範囲で調整できるようにするには、ADF4150HVの各RF出力上に小型のフィルタ構造を設ける必要もあります。27nHのインダクタを50Ωの抵抗と並列に使用すれば、最大3GHzまでの周波数を十分に調整できます。この抵抗は、定められた出力インピーダンスを設定する役割を果たします。インダクタンスが小さくなると、周波数帯は低周波数側に広がります。

今日では、より広い周波数範囲のための(つまりPLL、フィルタ、VCOのための)各種集積化ソリューションを1つのハウジングにまとめたものもあります。しかし、これらのソリューションでは異なるコンポーネントが互いに近い距離に置かれるので、望ましくないカップリングを招く可能性があります。ディスクリート設計と、それによる物理的な距離は、このリスクを最小限に抑えます。

PLL周波数シンセサイザ・シミュレーション・ツールのADIsimPLL™も、HF機能ブロックとモデル化されたHFシグナル・チェーンを開発する有効な助けとなります。このツールを使用すれば、PLL性能に影響を与える可能性のあるすべての重要な非線形効果、例えば周波数合成プロセスから生じる不要なスプリアス(スプリアス周波数)を、比較的容易にシミュレーションすることができます。