概要

設計リソース

設計/統合ファイル

- Schematic

- Bill of Materials

- Gerber Files

- PADS Files

- Assembly Drawing

評価用ボード

型番に"Z"が付いているものは、RoHS対応製品です。 本回路の評価には以下の評価用ボードが必要です。

- EVAL-CFTL-6V-PWRZ ($23.01) Wall Power Supply for Eval Board

- EVAL-CFTL-LVDT ($112.34) Measurement Specialties LVDT Sensor

- EVAL-CN0301-SDPZ ($169.20) Universal LVDT Signal Conditioning Circuit

- EVAL-SDP-CB1Z ($134.00) Eval Control Board

デバイス・ドライバ

コンポーネントのデジタル・インターフェースとを介して通信するために使用されるCコードやFPGAコードなどのソフトウェアです。

機能と利点

- LVDT シングル・コンディショニング

- 調整不要

- 低消費電力

製品カテゴリ

マーケット & テクノロジー

使用されている製品

参考資料

-

CN-0301 Software User Guide2018/10/23WIKI

-

CN-0301: ユニバーサル LVDT シグナル・コンディショニング回路2013/12/05PDF692 K

回路機能とその特長

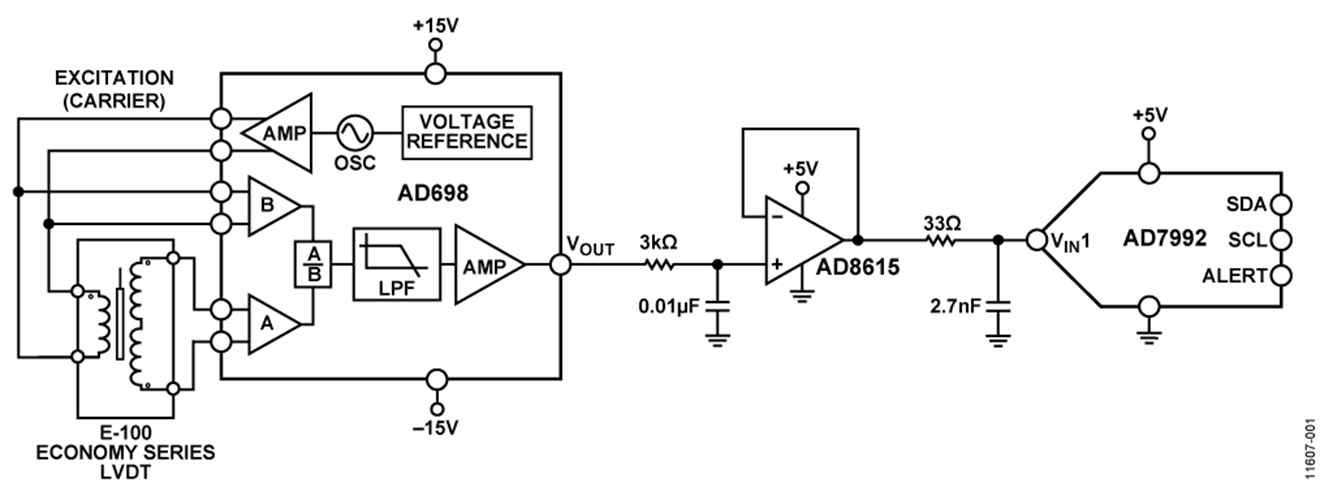

図1に示す回路は、無調整のリニア可変差動トランス(LVDT)シグナル・コンディショニング回路です。この回路は直線的な変位(位置)を高精度に測定することができます。

LVDTは、磁気コアが摩擦なしに動くことが可能であり、チューブ内部に接触することがないので、信頼性の高いセンサーです。このため、LVDTは、飛行制御帰還システム、サーボ機構の位置帰還、工作機械の自動計測など、長期的な信頼性が重要な多くの工業分野や科学分野の電気機械的なアプリケーションに適しています。

この回路は、サイン波発振器とパワー・アンプを内蔵してLVDTの1次側を駆動する励起信号を発生するAD698 LVDTシグナル・コンディショナを採用しています。また、AD698は2次側出力をDC電圧に変換します。AD8615レールtoレール・アンプはAD698の出力をバッファし、低消費電力の12ビット逐次比較A/Dコンバータ(ADC)を駆動します。このシステムは82dBのダイナミック・レンジと250Hzのシステム帯域幅を有しているので、高精度の工業用位置測定アプリケーションに最適です。

システムのシグナル・コンディショニング回路は消費電流が±15V電源から15mA、+5V電源から3mAとわずかです。

この回路ノートでは、ノイズ解析や部品選択に関する検討を含め、選択された帯域幅に対して図1の回路を最適化するのに用いるLVDTの基本動作原理およびデザイン・ステップを解説します。

回路説明

動作原理

LVDTは絶対変位トランスジューサで、機械的な基準(つまりゼロ)からの直線的な変位(位置)を、位相情報(方向)と振幅情報(距離)を含む比例電気信号に変換します。LVDTの動作では可動部品(プローブ、つまりコア・ロッドのアセンブリ)とトランスの間に電気的接触を必要としません。その代り、電磁結合に依存します。この理由と電子回路を内蔵せずに動作するという理由で、LVDTは、軍用や航空宇宙用のアプリケーションなど、過酷な環境で長寿命と高信頼性が要求されるアプリケーションにおいて幅広く用いられています。

この回路では、Measurement Specialties™のE-100エコノミー・シリーズLVDTセンサーをAD698とともに使用しました。全温度範囲で直線性が±0.5%のEシリーズは、適度な動作温度環境にある大部分のアプリケーションに適しています。

AD698はフル機能のLVDTシグナル・コンディショニング・サブシステムです。このデバイスは、LVDTのトランスジューサの機械的な位置を高精度で再現性の高いユニポーラDC電圧に変換します。全ての回路機能がチップ上に含まれています。周波数とゲインを設定するために若干の外付け受動部品を加えることで、AD698は生のLVDTの2次側出力をスケーリングされたDC信号に変換します。

AD698は、LVDTの1次側を駆動するための低歪みサイン波発振器を内蔵しています。サイン波の周波数は1個のコンデンサによって決まり、2V rms~24V rmsの振幅で20Hz~20kHzの範囲が可能です。

LVDTの2次側出力はAD698を直接駆動する2つのサイン波から成ります。AD698は、振幅変調された入力(2次側)Aと固定入力リファレンス(1次側、2次側の和、または固定入力)Bを同期して復調することにより、LVDTをデコードします。初期のソリューションに共通の問題は、LVDT駆動用発振器の振幅にドリフトが生じると、それに比例して出力にゲイン誤差が生じていたことです。AD698はドリフトの影響を相殺するため、入力励起に対するLVDT出力の比を計算することにより、これらの誤差を除去します。このデバイスは、回路の伝達関数が異なることと、LVDTの2次側の和(A + B)をストローク長に対して一定の値にする必要がないことが、AD598 LVDTシグナル・コンディショナと異なります。

AD698のブロック図を図2に示します。入力は2つの独立した同期復調チャンネルから成ります。BチャンネルはLVDTの駆動励起信号をモニタします。全波整流出力は計算回路に送られる前にC2によってフィルタされます。チャンネルAは、コンパレータのピンが外部で利用可能な以外はチャンネルBと同一です。LVDTがヌル(中心)位置のときにAチャンネルが0V出力に達する可能性があるため、Aチャンネルの復調器は通常、1次側電圧(Bチャンネル)によってトリガされます。さらに、LVDTの1次側から2次側への位相シフトを補償するために、Aチャンネルに位相リードや位相ラグを付加する位相補償回路が必要な場合があります。ハーフ・ブリッジ回路では位相シフトは重要ではなく、Aチャンネルの電圧は復調器をトリガするのに十分大きな大きさです。

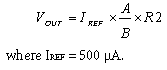

両方のチャンネルが復調されてフィルタされると、デューティ・サイクル乗算器で実装した分周回路を使って比率A/Bが計算されます。この分周器の出力がデューティ・サイクルになります。A/Bが1に等しい場合、デューティ・サイクルは100%に等しくなります。(この信号はパルス幅変調出力が必要なときにはそのまま使用できます。)このデューティ・サイクル信号は、デューティ・サイクルに比例させてリファレンス電流を変調してフィルタする回路を駆動します。出力アンプは500μAのリファレンス電流をスケーリングして電圧に変換します。出力伝達関数は次のとおりです。

部品の選択

AD698のデータシートに記載されている両電源動作(±15V)の設計手順では、励起周波数を2.5kHzに、システム帯域幅を250Hzに、出力電圧を0V~5Vに設定しています。

通常、AD698の内部発振器は出力に混入する少量のリップルを生じます。パッシブ・ローパス・フィルタを使って、このリップルを必要なレベルまで低減します。

システムの帯域幅を設定するためにコンデンサの値を選択する場合、トレードオフが必要になります。小さな値のコンデンサを選択するとシステムの帯域幅は大きくなりますが、出力電圧リップルは増加します。このリップルは出力電圧の設定に使用される帰還抵抗両端のシャント容量を大きくすることによって低減することができます。ただし、このことは位相ラグも大きくすることにもなります。

AD8615オペアンプがAD698の出力をバッファすることにより、AD7992 ADCを低インピーダンス・ソースで駆動させることができます(信号源インピーダンスが大きいとADCのAC性能に大きく影響します)。

AD698の出力とAD8615の入力の間のローパス・フィルタは次の2つの目的を果たします。

- AD8615への入力電流を制限すること

- 出力電圧リップルをフィルタすること

AD8615には内部保護回路があるため、電源を超える電圧を入力に印加することが可能です。AD698の出力電圧は±15Vの電源で±11Vの振幅が可能なため、このことは重要です。入力電流が5mA未満に制限されている限り、入力に高い電圧を印加することができます。これは主に、AD8615の入力バイアス電流がきわめて小さく(1pA)、大きな抵抗を使用することができるからです。このような抵抗を使用すると熱ノイズが加わり、アンプの総合出力電圧ノイズに影響を与えます。

AD8615は、入力過電圧保護機能があることと、入力と出力の両方でレールtoレールの振幅が可能なことから、AD7992 12ビットSAR ADCの入力のバッファと駆動に最適なアンプです。

ノイズの解析

選択した全てのシグナル・コンディショニング部品を使って、信号の変換に必要な分解能の大きさを決める必要があります。多くのノイズ解析のように、主要な要因のみを特定する必要があります。ノイズ源はrss(2乗和の平方根)で合算されるので、他のノイズより少なくとも3倍~4倍大きな単一のノイズ源が支配的になります。

LVDTシグナル・コンディショニング回路の場合、支配的な出力ノイズ源はAD698の出力リップルです。その他のノイズ源(抵抗ノイズ、AD8615の入力電圧ノイズと出力電圧ノイズ)は比較的かなり小さい値です。

AD698の出力電圧リップルは図3に示すように、0.39μFのコンデンサ値を使用し、帰還抵抗両端に10nFのシャント・コンデンサを接続すると0.4mV rmsになります。これらの部品および関連するピン接続は図1の簡略回路図には示されていません。詳細についてはAD698のデータシートを参照してください。

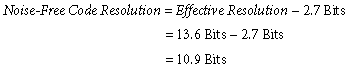

フルスケール出力をシステムの総合rmsノイズで割ることにより、分解可能なrmsカウントの最大数を計算することができます。

実効分解能は総合rmsカウントの底が2の対数をとることによって得られます。

![]()

ノイズフリー・コード分解能は、実効分解能から2.7ビットを差し引くことによって得られます。

システムの総合出力ダイナミック・レンジは、フルスケール出力信号(5V)を総合出力rmsノイズ(0.4mV rms)で割り、デシベルに変換することによって計算することが可能で、その値は約82dBになります。

AD7992は分解能が12ビットで、3.4MHzのシリアル・クロックを用いたときの1チャネルあたりのサンプリング・レートが188kSPSなので、このアプリケーションに適しています。

位相ラグ/リードの補償

AD698は、1次側に供給されるリファレンス発振器の信号とリターン信号を乗算することによる復調機能を用いて出力信号を生成します。少量の位相シフトで、出力にアンダーシュートとして現れる大きな直線性誤差を生じる可能性があります。

位相リード回路はE-100シリーズLVDTの1次側から2次側への−3°の位相シフトを補償します。2つの異なる位相補償回路を図4に示します。

適切な回路網を構成するため部品の値を選択する際には、励起信号がAD698の±ACOMP入力に達する前に励起信号の振幅を低減する抵抗分割器をRSとRT で効果的に構成するように考慮することが重要です。これはRTをRSよりかなり大きくする必要があることを意味します。また、位相ラグ/リード補償回路は励起出力に負荷として加わるため、大きな抵抗値を推奨します。最終的な目標は、AD698のACOMP入力において振幅低下の小さい、望みの位相ラグ/リードを実現することです。

位相ラグ/リードの大きさは、次式を使って計算することができます。

テスト結果

Measurement SpecialtiesのE-100エコノミー・シリーズLVDTをJ3に接続し、EVAL-CN0301-SDPZ評価ボードのJ6に生じるAD698の出力をデジタル・オシロスコープでモニタしたところ、実際の出力リップルは図5に示すように6.6mV p-pでした。

AD698の出力とAD8615の入力の間のローパス・フィルタ(3kΩ、0.01μF)は、−3dB帯域幅が5.3kHzでリップルを2mV p-pまで低減します。

AD698の出力段とAD8615の入力段の間にローパス・フィルタを実装したときのデータは、図6に示すように、EVAL-CN0301-SDPZ評価ボードから収集されました。

AD698から生じるリップルは2mV p-pまで減衰され、システムは11ビットのノイズフリー・コード分解能を実現することができました。

この回路ノートに関する完全な設計サポート・パッケージはhttps://www.analog.com/CN0301-DesignSupportで入手できます。

飛行制御面位置帰還のアプリケーション

無人自律走行車(UAV)や無人飛行機は、米国の国家安全保障における役割が増大し続けています。これらの高度な技術、複雑な航空プラットフォームは何マイルも離れたクルーによって制御され、マルチミッションが可能です。これらには航空偵察、戦闘用武器のプラットフォーム、戦場の指令や管理の監視、無人空中給油ステーションなどの役割があります。

UAVに用いられている複雑なシステムは、高精度な制御と帰還を行うために無数の電子センサーを使用しています。UAVの高度(ピッチ(左右回転)、ロール(前後回転)、ヨー(上下回転))を制御するため、アクチュエータを使って飛行制御面に力を与えます。これらのアクチュエータの位置を高精度に測定することは、適切な飛行経路を維持するのに非常に重要です。

アクチュエータの位置の測定に使われるセンサーは、高精度、高信頼性、軽量という3つの不可欠な条件を満たす必要があります。これら3つの特性は全てMeasurement Specialtiesによって設計されたLVDTに備わっています。

複数のLVDTの同期動作

複数のゲージ測定などの多くのアプリケーションでは、多数のLVDTがごく近接して使用されています。これらのLVDTが同じようなキャリア周波数で動作すると、浮遊磁気結合によってビートが生じる可能性があります。このビートはこのような条件で行われる測定の精度に影響を与える恐れがあります。このような状況にならないようにするため、全てのLVDTを同期動作させます。

EVAL-CN0301-SDPZ評価ボードは、ジャンパJP1、JP2、JP4に短絡ジャンパを実装し、JP3を未実装のままにすることで、2個のLVDTの間に1個のマスタ発振器が接続された構成にすることができます。それぞれのLVDTの1次側は専用のパワー・アンプで駆動されるため、熱負荷はAD698デバイスの間で分担されます。

バリエーション回路

選択された部品はAD698からの最大5Vのユニポーラ出力に対して最適化されたものですが、他の組合わせに置き換えることも可能です。

その他の適した単電源アンプはAD8565とAD8601です。これらのアンプは入力過電圧保護機能を備え、入力と出力の両方でレールtoレールの振幅が可能なため、AD8615の置換えに適しています。両電源動作が必要な場合、ADA4638-1やADA4627-1を推奨します。

AD698が±10Vのバイポーラ信号を出力する場合には、AD7321を推奨します。AD7321は、最大±10Vの真のバイポーラ・アナログ入力信号を受け入れることが可能な、2チャンネル、バイポーラ入力、12ビットADCです。

回路の評価とテスト

この回路は、EVAL-CN0301-SDPZ回路ボードとEVAL-SDP-CB1Z SDP-Bシステム・デモンストレーション・プラットフォーム・コントローラ・ボードを使用します。2枚のボードは120ピン・コネクタを備えているので、短時間で組み立てて回路の性能を評価することができます。EVAL-CN0301-SDPZは評価対象の回路を備えており、EVAL-SDP-CB1Z(SDP-B)はCN-0301評価用ソフトウェアとともに使用し、EVAL-CN0301-SDPZからデータをキャプチャします。

必要な装置

以下の装置が必要です。

- USBポート付きWindows® XP(32ビット)、Windows Vista®、またはWindows 7搭載PC

- EVAL-CN0301-SDPZ回路ボード

- EVAL-SDP-CB1Z SDP-Bコントローラ・ボード

- CN-0301評価用ソフトウェア

- EVAL-CFTL-6V-PWRZ DC電源または等価な6V/1Aベンチ電源

- Measurement SpecialtiesのE-100エコノミー・シリーズLVDT(EVAL-CFTL-LVDT)

評価開始にあたって

CN-0301評価用ソフトウェアのCDをPCのCDドライブにセットして、評価用ソフトウェアをロードします。マイコンピュータから評価用ソフトウェアCDを挿入したドライブを探します。

機能ブロック図

回路ブロック図については図1を、全体回路図についてはファイルEVAL-CN0301-SDPZ-PADSSchematic.pdfをご覧ください。このPDFファイルはCN-0301 Design Support Packageに含まれています。

セットアップ

EVAL-CN0301-SDPZの120ピン・コネクタをEVAL-SDP-CB1Z(SDP-B)のCON A コネクタに接続します。120ピン・コネクタの端部にある穴を利用し、ナイロン製の固定用部品を使って2枚のボードをしっかりと固定します。電源をオフにして、6V電源をボードの+6VピンとGNDピンに接続します。6VのACアダプタがある場合は、ボード上のACアダプタ用ジャックに接続して、6V電源の代わりに使用することができます。EVAL-SDP-CB1Zに付属のUSBケーブルをPCのUSBポートに接続します。このとき、USBケーブルをEVAL-SDP-CB1ZのミニUSBコネクタに接続しないでください。

テスト

EVAL-CN0301-SDPZに接続された6V電源(またはACアダプタ)をオンにします。評価用ソフトウェアを起動し、PCからのUSBケーブルをEVAL-SDP-CB1ZのミニUSBコネクタに接続します。

USBによる通信が確立されると、EVAL-SDP-CB1ZはEVAL-CN0301-SDPZとの間のパラレル・データの送受信およびキャプチャを行うことができます。

EVAL-SDP-CB1Zに接続されたEVAL-CN0301-SDPZの写真を図8に示します。EVAL-SDP-CB1Zについては、UG-277ユーザー・ガイドを参照してください。

テスト・セットアップと校正についての詳細、およびデータ・キャプチャ用評価ソフトウェアの使用方法については、CN-0301ソフトウェア・ユーザー・ガイドに記載されています。

プロトタイプ開発での接続

EVAL-CN0301-SDPZはEVAL-SDP-CB1Zを使用するように設計されていますが、マイクロプロセッサを使ってAD7992のI2C 2線シリアル・インターフェースとインターフェースすることができます。その他のコントローラをEVAL-CN0301-SDPZとともに使用するためには、サードパーティによるソフトウェア開発が必要になります。

アルテラやザイリンクスのフィールド・プログラマブル・ゲート・アレイ(FPGA)とのインターフェースに使用可能な既存のインターポーザ・ボードがあります。Niosドライバを使用することにより、アルテラのBeMicro SDKボードをBeMicro SDK/SDPインターポーザと併用することができます。FMCコネクタを備えたザイリンクスのどの評価ボードもFMC-SDPインターポーザ・ボードと併用することができます。

EVAL-CN0301-SDPZはディジレントのImodインターフェース仕様とも互換性があります。

システムの写真を図8に示します。