概要

設計リソース

設計/統合ファイル

- Schematic

- Bill of Materials

- Gerber Files

- PADS Files

- Assembly Drawing

デバイス・ドライバ

コンポーネントのデジタル・インターフェースとを介して通信するために使用されるCコードやFPGAコードなどのソフトウェアです。

ADF4350 IIO Wideband Synthesizer GitHub Linux Driver Source Code

機能と利点

- PLL/VCO内臓

- 低ジッタのファンアウト・バッファ

- LVPECL出力

参考資料

-

UG-435: Evaluation Board for the ADF4351 Fractional-N PLL Frequency Synthesizer (Rev. 0)2015/09/14PDF1043 kB

-

UG-068: Setting Up the Evaluation Board for the ADCLK9482009/11/16PDF211 kB

-

MT-101: Decoupling Techniques2015/02/14PDF954 kB

-

MT-031: データ・コンバータのグラウンディングと、「AGND」および「DGND」に関する疑問の解消2009/03/20PDF144 kB

-

CN0294: 低ジッタのLVPECLファンアウト・バッファによるクロック源からの出力数の増加2012/09/20PDF420 kB

回路機能とその特長

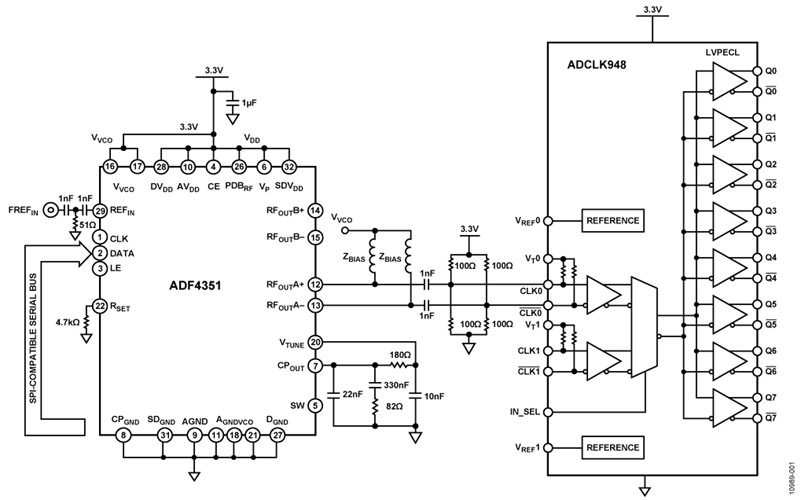

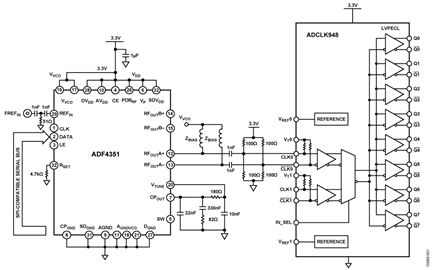

多くのシステムは、ミックスド・シグナル処理やタイミング処理のために複数の低ジッタのシステム・クロックを必要とします。図1に示す回路は、フェーズロック・ループ(PLL)と電圧制御発振器(VCO)を内蔵したADF4351とADCLK948のインターフェースを行います。ADCLK948は、ADF4351の差動出力の1つから最大8個の差動の低電圧ポジティブ・エミッタ結合ロジック(LVPECL)出力を供給します。

最近のデジタル・システムは、多くの場合、クロック源のロジック・レベルとは異なる多くの高品質クロックを必要とします。完全性を損なうことなく別の回路素子へクロックを高精度で分配するには、バッファリングの追加を要することがあります。この回路ノートでは、ADF4351クロック源とADCLK948クロック・ファンアウト・バッファのインターフェースについて説明し、測定結果からクロック・ファンアウト・バッファによる付加ジッタが75fs rmsであることを示します。

回路説明

ADF4351は広帯域PLLとVCOで構成されており、VCOは3つの別々のマルチバンドVCOから構成されています。各VCOは約700MHzの周波数範囲をカバーしています(各VCO間には、いくらかのオーバーラップがあります)。これにより、2.2GHz~4.4GHzのVCOの基本周波数範囲が可能になります。ADF4351の内部分周器を使って、2.2GHzより低い周波数を生成することができます。

クロックを生成するには、ADF4351のPLLとVCOをイネーブルし、必要な出力周波数を設定する必要があります。ADF4351の出力周波数は、シャント・インダクタ(またはシャント抵抗)とDC阻止コンデンサを必要とするオープン・コレクタ出力のRFOUTピンに供給されます。

ADCLK948はSiGeプロセスを採用した低ジッタのクロック・ファンアウト・バッファで、最大入力周波数(4.5GHz)がADF4351の最大入力周波数(4.4GHz)のすぐ上であるため、ADF4351と併用するのに最適です。広帯域のrms付加ジッタは75fsです。

ADCLK948のCLK入力に1.65VのDC同相バイアス・レベルを追加して、LVPECLロジック・レベルを再現する必要があります。これは抵抗バイアス回路網を使用することによって行われます。DCバイアス回路を追加しないと、ADCLK948の出力の信号の完全性が損なわれます。

バリエーション回路

この他に使用可能なVCO内蔵のシンセサイザとして、フラクショナルN型(137MHz~4400MHz)のADF4350とインテジャーN型のADF4360があります。

また、ADCLK948と同じファミリーで、他に使用可能なクロック・ファンアウト・バッファとして、ADCLK946(6個のLVPECL出力)、ADCLK950(10個のLVPECL出力)、ADCLK954(12個のLVPECL出力)があります。

回路の評価とテスト

この回路はクロック源としてEVAL-ADF4351EB1Zボードに多少の変更を加えたものを使って評価しました。EVAL-ADF4351EB1Z評価ボードは、標準のADF4351プログラミング・ソフトウェアを使っており、これは評価ボードに付属のCDに入っています。ADCLK948/PCBZ評価ボードも必要で、これは変更なしでそのまま使用することができます。

必要な装置

以下の装置が必要です。

- プログラミング・ソフトウェア付きEVAL-ADF4351EB1Z評価ボード・キット

- ADCLK948PCBZ評価ボード

- 3.3V電源

- 3.3V電源をADCLK948PCBZに接続する2本のケーブル

- 2本の同じ長さの短いSMA同軸ケーブル

- 高速オシロスコープ(帯域幅2GHz)または相当品

- R&S FSUP26スペクトル・アナライザまたは相当品

- AWindows® XP、Windows Vista(32ビット)、またはWindows 7(32ビット)搭載PC

EVAL-ADF4351EB1ZのRFOUTA+ピンとRFOUTA−ピンをそれぞれADCLK948PCBZのCLK0ピンとCLK0ピンに接続するために、SMA同軸ケーブルが必要です。

機能ブロック図

この評価ではADCLK948PCBZとEVAL-ADF4351EB1Z が使用されています。EVAL-ADF4351EB1Z評価ボードはSMAケーブルを介してADCLK948PCBZに接続されています。

評価開始にあたって

EVAL-ADF4351EB1Z評価用ソフトウェアのインストールと使用方法の詳細は、ユーザー・ガイドUG-435に記載されています。また、UG-435には、ボードのセットアップ方法、ボードの回路図、レイアウト図および部品表も含まれています。このボードに必要な変更は、DC阻止コンデンサの後に100Ω抵抗を挿入することです。この抵抗は3.3VとGNDの間に接続します。この措置はRFOUTA+ピンとRFOUTA−ピンの両方で行い、1.65Vの同相電圧(1.5V以上が必要)を供給する必要があります。このため場合によっては、これらの伝送ライン付近の半田マスクを取り去る必要があります。

UG-068ユーザー・ガイドには、ADCLK948/PCBZ評価ボードの動作に関連する同様の情報が含まれています。

ロジック・レベルの測定

この例では、Rohde & Schwarz RTO1024オシロスコープを2本のRT-ZS30アクティブ・プローブと併用して、高速ロジック・レベルを高精度に測定します。

以下の操作を行ってADF435xソフトウェアをPCにインストールします。

- EVAL-ADF4351EB1ZをPCに接続し、UG-435のハードウェア・ドライバの説明に従います。

- ADF435xソフトウェアのスクリーンショットに従ってADF4351のPLLを設定します(図3参照)。この例では、1GHzのRF周波数が選択されています。

- 2本の同じ長さの短いSMAケーブルを使用し、 EVAL-ADF4351EB1ZのSMAコネクタRFOUTA+とRFOUTA−をそれぞれADCLK948/PCBZボードのSMAコネクタCLK0とCLK0に接続します。

- ADCLK948/PCBZの差動出力OUT2とOUT2を高速オシロスコープに接続します。1GHz出力の標準的な波形を図4に示します。

位相ノイズとジッタの測定

- 「ロジック・レベルの測定」のセクションのステップ1からステップ4を繰り返します。

- 使用しないADCLK948/PCBZのCLK2出力を50Ωの負荷で終端します(図5参照)。

- CLK2出力をSMAケーブルを介して信号源アナライザに接続します(図5参照)。

- 信号のジッタ性能を測定します。

ADF4351の出力での位相ノイズを図6に示します。rmsジッタは325.7fsです。ADCLK948の出力での位相ノイズを図7に示します。rmsジッタは330.4fsです。

ADCLK948に付加されるジッタは√(330.42 − 325.72) = 55.5 fs rmsのように計算することができます。ADCLK948のデータシートから得られる規定値は75fs rmsです。