概要

設計リソース

デバイス・ドライバ

コンポーネントのデジタル・インターフェースとを介して通信するために使用されるCコードやFPGAコードなどのソフトウェアです。

機能と利点

- HDMIからVGAへの変換

- 低消費電力

製品カテゴリ

マーケット & テクノロジー

使用されている製品

参考資料

-

MT-101: Decoupling Techniques2015/02/14PDF954 kB

-

MT-031: データ・コンバータのグラウンディングと、「AGND」および「DGND」に関する疑問の解消2009/03/20PDF144 kB

-

CN0282: オーディオ抽出機能付きの、USBから給電されるDVI/HDMI-to-VGAコンバータ(HDMI2VGA)2012/08/03PDF267 kB

回路機能とその特長

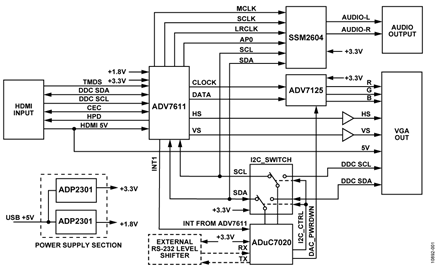

図1に示す回路は、HDMI/DVIからVGAへの変換(HDMI2VGA)の完全なソリューションで、アナログ・オーディオ出力を備えています。これには、165 MHzまでのビデオ・ストリームを受け取ることができるローパワーのADV7611高精細度マルチメディア・インターフェース(HDMI)レシーバが使われています。

この回路はUSBケーブルから給電され、最高1600 × 1200/60Hzの分解能で動作します。

この回路はEDID(拡張表示識別データ)情報を使って、HDMI/digital visual interface (DVI)ソースからのビデオ・ストリームが、HDMIソース、コンバータ、およびビデオ・グラフィックス・アダプタ(VGA)ディスプレイがサポートしている、最高の分解能になるように保証します。

HDMIレシーバは、輝度やコントラストなどのビデオの調整に使うこともでき、オーディオ・コーデックはオーディオ出力の音量設定に使うことができます。

この回路には多くの利点があります。高度に集積化されたビデオ・レシーバにより、FPGA(フィールド・プログラマブル・ゲートアレイ)を追加する必要なくビデオの調整が可能です。シンプルなI2C書き込みで輝度やコントラストの調整、オーディオ音量の変更が可能です。内蔵EDIDメモリは部品数と必要な実装面積を減らします。降圧スイッチング・レギュレータにより、USBポートから回路に給電することができます。業界標準のチップ間接続を使って、レシーバ、コーデック、およびビデオD/Aコンバータ(DAC)を相互に直接接続することができます。回路は2層プリント回路基板(PCB)に実装され、UXGAの分解能(1600 × 1200/60Hz)まで動作します。

回路説明

ADV7611はHDMI入力の受信ソリューションを提供し、5Vケーブル検出、活線挿入検出ラインのアサート、およびEDIDの目的に使用されるDDCラインを備えています。ADV7611はHDMIソースに対しディスプレイの機能を知らせる内部EDID RAM を内蔵しています。この回路の内蔵色空間コンバータ(CSC)はどんなHDMIの色空間でも、ADV7125ビデオDACの入力を駆動するのに適した8ビットのRGB444ワードに変換します。これには、RGB、YCrCb (601と709)、XVYCC (601と709)、およびHDMI仕様で規定された他の色空間の変換が含まれます。ADV7611は444と422のサンプリング方式間の変換も行うことができます。

ADV7125ビデオDACは受信したデジタル・ストリームをVGA互換のアナログ信号に変換します。

コンバータ内でのオーディオ処理は、オーディオ・パケット抽出ブロックを内蔵しているADV7611によって開始されます。このデバイスは実際にはどのHDMI規格でも出力することができます。ただし、バックエンドのSSM2604オーディオ・コーデックは、44.1 kHzまたは48 kHz のサンプリング・レートの線形パルス符号変調(LPCM)オーディオを搬送するI2S ストリームだけを受け入れます。このようなI2S ストリームが送られるのを保証するため、ADV7611は、LPCM機能だけを示す適切なEDID情報をHDMIソースに与える必要があります。

オーディオ・ラインの出力信号のインピーダンスは100 Ω なので、ヘッドホンまたはスピーカを接続するにはパワーアンプ段を追加する必要があります。

回路はADuC7020マイクロコントローラで制御されます。ADuC7020は、ADG736スイッチを介してVGAディスプレイのデータ・チャンネル(DDC)ラインまたはメインI2C バスのどちらかに接続されたI2C SDAラインとSCL ラインを使用します。スイッチにより、メインI2C バスをVGA I2C DDC ラインから分離することができ、(モニタが他のデバイスとDDC I2Cを共有しているか、またはVGA DDCラインに不具合が生じた場合)衝突のリスクを最小に抑えることができます。メインI2CバスにはADV7611とSSM2604 I2Cスレーブ・デバイスが接続されています。

ADuC7020はUART(汎用非同期送受信回路)のラインも備えています。これらは、実行可能コードで内蔵フラッシュ・メモリをプログラムするのに、(P0.0に接続された)シリアル・プログラミング・ボタンおよびリセット・ボタンとともに使用されます。通常動作では、UARTインターフェースを、デバッグ出力またはソフトウェア開発時の端子としても使用することができます。RS232規格を使っているPCに接続するには、追加のレベル・シフタ(たとえば、ADM3202)が必要です。ADuC7020は、ビデオDACを制御できるようにするため、ADV7611のINT1ピンとRESETピンおよびADV7125のPSAVEピンにも接続されています。

Tこのボードは、5 V USB電源からボードに給電するため、2個のADP2301降圧スイッチング・レギュレータを使用しています。これらの高効率レギュレータはボード上のデバイスに3.3 Vおよび1.8 Vを供給します。

ボードの初期化

ボードが最初に起動したとき、モニタからVGA EDIDを読み出し、HDMIストリームを受信するようにADV7611をプログラムし、DACを介してI2Sオーディオ信号を出力するようにSSM2604をプログラムします。

EDIDコンテンツの設定

HDMI2VGAコンバータは、ビデオ・ディスプレイが受け取ることができる適切なビデオ規格がHDMIリンクを介して送られるように保証します。HDMIの仕様では、ビデオ・ストリームを送る前に、サポートされているHDMIシンクのビデオ・モードをHDMIソースがチェックする必要があります。HDMIソースがEDID情報を読み出すと、ビデオ・ディスプレイによってサポートされている規格だけ(理想的にはディスプレイによって優先されている規格)を選択することができます。したがって、出力されるビデオがディスプレイにとって受け入れ可能であることを保証するために、EDID情報は不可欠です。

オーディオ規格も類似の方法で処理されます。HDMIシンクによってサポートされているオーディオ規格はEDID情報内に列挙されています。HDMIソースは、EDID情報に列挙されている規格の1つに合致するオーディオ・ストリームを送る必要があります。

ADuC7020はVGA情報を読んでモニタの機能を判断するのに使われます。標準的モニタのVGA EDIDはオーディオ機能を列挙しておらず、ADV7611によってサポートされていないビデオ分解能(たとえば、165 MHzを超えるピクセル・レートやVESA 1920 × 1200/60 Hz)を含んでいることがあります。

したがって、HDMIソースへ転送されたEDID情報がADV7611とVGAディスプレイによって共通にサポートされているビデオ・モードだけを含んでいることを保証することが重要です。

ADV7611のためのEDIDの準備

HDMIソースへ送られた新しいEDID情報の初期ソースはVGAモニタから取得されて修正されたEDIDを含んでいます。取得されると、VGA EDID の以下のバイトが修正のために内部ADuC7020 RAM へコピーされます。修正されると、(ADV7611の内部EDIDを介して)HDMIソースへ与えられます。

- バイト[0:19]、ヘッダ情報

- バイト[19:24]、基本的ディスプレイ情報

- バイト[25:34]、色度座標

- バイト[35:37]、確定したビットマップ設定(全てADV7611によってサポートされています)

EDIDのバイト20(ビデオ入力パラメータ)は、HDMI2VGAコンバータがデジタル・ビデオ入力であることを表示するために0へ修正されます。

EDIDのバイト[38:54]には標準的なタイミング情報が含まれます。列挙されているどのモードも165 MHzの最大ピクセル・クロック周波数を超えないことを保証するため、STDタイミング情報ブロックに列挙された各モードは、次式を使ってピクセル・クロック周波数が計算されます。

上の式はビデオを転送するのに必ず使う最小ピクセル周波数を見積もります。見積りは、ビデオにはライン毎に1ピクセル幅だけの水平syncパルスが1個だけ、およびフレーム毎に1ラインだけの垂直ブランキング期間(VBI)が含まれると仮定しています。現実のアプリケーションでは、このタイプのビデオは使用されず、見積りは単なる近似にすぎません。正確なPCLK値に関しては、実際のVESA規格に基づいた対照表を使用してください。

計算したPCLK周波数が165 MHzを超えると、そのビデオ・モードはEDIDから除外されます。

EDIDの次の部分(バイト[54:125])は4ブロックのディスクリプタ([54:71]、[72:89]、[90:107]、および[108:125])によって占められています。アプリケーションは4つのディスクリプタの全てをチェックし、2つのタイプのディスクリプタを識別します。

- ピクセル・クロック周波数の詳細タイミング・ディスクリプタ(最初の2バイトの少なくとも1つはゼロと異なる)

- モニタによってサポートされる最大ピクセル・クロック周波数のモニタ範囲ディスクリプタ(最初の2バイトはゼロ、4番目のバイトは253に等しい)

詳細タイミング・ディスクリプタ(DTD)はモニタの本来のビデオ・タイミングを示します。最初の2バイトにはピクセル・クロック周波数の値が含まれます。それが165 MHzを超えていると、ディスクリプタ全体が640 × 480/60 Hzのビデオ・モードに適したDTDブロックに置き換えられます。

モニタ範囲ディスクリプタにはモニタが扱える最大PCLK 周波数に関する情報が含まれます。それが165 MHzを超えている場合は165 MHzに設定されます。

標準EDIDの最後のブロックには以下の2バイトが含まれます。

- バイト126は追加のEDIDブロックの数を与えます。アプリケーションはこのバイトを1で上書きし、追加のEDIDを与えます。

- バイト127はチェックサム・バイトです。

追加のEDIDブロック(CEA-861タイプ)は128バイト長で、サポートされているビデオ規格として640 × 480ピクセルを記述するとともに、オーディオ機能に関する情報を含んでいます。このブロックの主な目的として、HDMIソースにオーディオ機能(ステレオLPCM、44.1 kHz、48 kHz、および32 kHz、左前方と右前方のスピーカ付き)を知らせます。CEA-861ブロックには、サポートされるビデオ規格(標準RGBとともにYCbCr444やYCbCr422など)に関する追加情報も含まれています。

詳細に関しては、https://www.analog.com/CN0282-DesignSupportの設計支援ファイルのCソース・コードを参照してください。

HDMIソースとVGAディスプレイの検出

HDMIケーブル信号からの5 V 信号は、入ってくるビデオをVGAモニタに知らせるのに使用されます。ADuC7020はVGAが接続されているものと仮定し、チェックを行ないません。モニタの検出はEDID情報を読み出すことで実現できます。I2Cアクノリッジがないと、モニタは接続されていないと見なすことができます。

HDMIソース検出は不要です。HDMIコンテンツを受け取るようにADV7611がプログラムされると、ケーブルが接続される度に、また入力ビデオ規格が変更されたときに作動します。ケーブルが外されると、HDMIレシーバは最後に受信されたビデオの解像度でブルー・スクリーンを表示します。

HDMIソース検出はADV7611によって行われます。接続状態はIOマップのレジスタ0x6F (デバイス・アドレス0x98)を読み出すことによって判断することができます。 Hardware User Guide (UG-180)を参照してください。

HDMI2VGAコンバータの制限事項

データ・コンテンツの保護について考慮する必要があります。標準VGA信号は暗号化されていないビデオ信号で、アナログ・レコーダを使って記録することができ、コンテンツ保護機構が何もなくても再生できます。したがって、VGAビデオは著作権のあるものに対して安全ではありません。HDMI-to-VGAコンバータは元データに著作権のあるビデオ・ストリームのコンテンツ保護ができないので、それは受信できないようにしなければなりません。

ADV7611はこの問題を解決します。2つのシリコン・バージョン(ADV7611とADV7611-P)がリリースされています。ADV7611は暗号化されたコンテンツの復号を可能にしますが、ADV7611-Pにはその機能がなく、暗号化されていないビデオ・コンテンツだけを受信することができます。HDMI2VGAコンバータはADV7611-Pを使用する必要があります。

図1に示されている回路は、ユーザーが復号化されたビデオ・ストリームに容易にアクセスできないような方法で回路が修正される限りは、既存のVGAモニタ内で暗号化されたコンテンツを受信するように修正および改造することができます。

レイアウト時の考慮事項

ADV7611BSWZ-PとADV7125BCPZ間の配線に注意すれば、回路を2層ボードに構成することができます。このボードは165 MHz までのピクセル・クロック周波数のビデオ・ストリームに対して動作することが実証されています。PCBのボトム層は主に単一のグランド・プレーンで、いくつかのトレースがボトム層へ配線されています。トップ層とボトム層のグラウンドを接続する多数のビアにより、高速信号によるボードの電流トランジェント特性に起因するグラウンド・バウンスが最小に抑えられます。PCBのトップ面の写真を図2に示します。全体回路図、部品表(BOM)、およびレイアウトの詳細に関しては、設計支援ファイルhttps://www.analog.com/CN0282-DesignSupportを参照してください。

実際のシステムに使用するときは、4層PCBの方がいくつかの利点があります。HDMIのコンプライアンス・テストは、HDMIレシーバに入ってくる全てのTMDS(transition-minimized differential signaling-遷移時間最短差動信号伝送方式)ラインの特性インピーダンスが100 Ω ± 10%であることを要求します。トレースの特性インピーダンスの維持は、2層PCBに比べて4層PCBの方が一般に簡単です。さらに、4層PCBは、電磁干渉(EMI)/無線周波数干渉(RFI)の影響を避けるためや電磁コンプライアンス(EMC)を達成するための、より多くのオプションを提供します。

高速の立ち上がりエッジ、立ち下がりエッジを持つ高速デジタル信号はEMI/RFI の影響のリスクを生じます。ボード上の高速信号は、ADV7611の出力をADV7125 DACの入力に接続するピクセル・バス・リンク上に主に存在します。直列抵抗をこれらのラインに追加して高速エッジを遅くすることで、EMI/RFI の影響を小さく抑えることができる場合もあります。2層レイアウトでは、ADV7611とADV7125の接続が比較的短いので、直列抵抗は不要です。

EMI/RFI放射の影響を小さく抑えるため、ピクセル・バスのドライバとオーディオ出力の駆動強度を設定するオプションが与えられています。駆動強度の低減はADV7611の内部で達成されます。詳細については、UG-180 User GuideのDrive Strength Selection(駆動強度の選択)のセクションを参照してください。

評価とテスト

以下のHDMIソースを使って回路をテストしました。

- DVD-S97 DVD/CDプレーヤ(640 × 480p)

- Dell E6520ラップトップ(1280 × 1024または1600 ×1200 VGAモニタ分解能)

- Blu-ray Panasonic DMP-BDT100 (640 × 480p)

- Quantum Data 882ビデオ・ジェネレータ(UXGA 1600 × 1200/60 Hz、8 bpp)

以下のVGAモニタを使って回路をテストしました。

- Dell 1908FP (最大1280 ×1024/60 Hz)

- Dell 2007FP (最大1600 ×1200/60 Hz)

- Sun Microsystems GDM-5010PTモニタ

ボードの評価中、評価用ボードのプログラミングとデバッグ情報およびVGAモニタのEDID情報の表示の両方にUARTコネクタ(EVAL-ADuC-CABLE1Z)を使用しました。EVAL-ADuC-CABLE1ZはRS-232レベル・シフタで、LVTTLとRS-232のロジック・レベル間のインターフェースを可能にします。

テストには、図3に示されているようにケーブルを接続して(VGA、HDMI、オーディオ出力、およびUSB)、リセット・ボタンを押す必要があります。

民生用ビデオ・プレーヤ(DVDまたはBlu-ray)は、通常はXGA、SXGA、UXGAなどのVESAビデオ分解能をサポートしていません。テストの間、それらのソースは標準VGAを出力しました。

Dell E6520ラップトップは本来VESA規格をサポートするビデオ・ソースとして使うことができ、HDMI2VGAコンバータによって与えられるコンテンツを正しく読み出します。これは、Dell 1908FPモニタの場合の1280 × 1024/60 Hz、Dell 2007FPモニタの場合の1600 × 1200/60 Hzのどちらかを出力します。

両方のビデオ・プレーヤともEDID に従ってLPCMオーディオ情報を供給し、オーディオ・コーデックにより問題なく復号化されて出力されました。