クロックIC & タイマー

アナログ・デバイセズのクロックICとタイマーは、新しいアーキテクチャ、開発/製造コストの削減、設計期間の短縮を可能にします。同製品は、クロックのクリーンアップ、同期、生成、遅延、分配のための低ジッタと位相ノイズを特長としています。同様に、アナログ・デバイセズのクロックに関する専門知識は、有線ネットワーク・クロックICのポートフォリオに反映されています。有線ネットワーク・クロックICは、有線アプリケ

Viewing:

サブカテゴリ

クロック

アナログ・デバイセズは、さまざまなアプリケーション向けに超低ジッタのクロック生成、分配、同期製品を提供しています。アナログ・デバイセズのクロック製品は、高性能アナログ・デジタル・コンバータ(ADC)、

デジタル・アナログ・コンバータ(DAC)、またはペリフェラル・デジタル・デバイスのクロックに最適です。アナログ・デバイセズのクロックICは、PLLコア、分周器、位相オフセット、スキュー調整、クロック・ドライバ、時間-デジタルコンバータ、その他の機能を小型チップ・スケール・パッケージに集積しています。

クロック&データ再生/リタイミング

アナログ・デバイセズは、メトロ、ロングホール、DWDM、FSOアプリケーションなどの各種装置の設計のために、ディスクリート・レート、マルチレート、連続調整のクロック&データ再生ICを提供しています。当

社のCDRは、プロトコル非依存のアプリケーションに簡単に組み込むことができ、基準クロックを使用せずに12.3Mbps~2.7Gbps間の任意の速度で自動的に着信データ・ストリームにロックし、同時に取得したデータレートをI2Cインターフェースにより伝送します。

パルス & PWMジェネレータ

アナログ・デバイセズの設定可能なパルス幅変調器(PWM)およびパルス・ジェネレータは、単一の入力電圧で出力のデューティ・サイクルを容易に制御する機能を提供します。これらの小型低消費電力デバイスは、0%

~100%のデューティ・サイクルと幅広い調整可能な出力周波数を提供し、調光、絶縁型の比例制御、効率的な負荷制御などのアプリケーションを簡素化する上で最適です。

ファンアウト・バッファ

ファンアウト・バッファは、入力信号の複数のコピーをその出力で作成し、複数の負荷に分配することができます。アナログ・デバイセズは、高速立上り/立下り時間、低ジッタ、調整可能な出力電圧、複数のインターフェ

ースを備えた幅広いポートフォリオを提供しています。

リアルタイム・クロック & タイマー

リアルタイム・クロック(RTC)ICは、電子回路で実世界を基準にして時間を追跡管理するために使用されます。高精度な時間の維持は、とりわけシステムに多大な負荷がかかっている時や、メイン・デバイスの電源が

オフの時に重要です。消費電力、精度、堅牢性、そして小型パッケージは重要な要素です。アナログ・デバイセズは、あらゆるソリューション・ニーズに対応する高精度、低消費電力、小型パッケージ、堅牢なマイクロエレクトロメカニカル・システム(MEMS)ベースのリアルタイム・クロックを幅広く提供しています。

発振器

アナログ・デバイセズは、優れた位相ノイズ性能、広帯域オプション、複数の出力選択肢を備えた電圧制御発振器(VCO)から、ピン設定、抵抗接続、シリアル・インターフェース(SPIまたはI2C)を介して周波数

を設定可能なシリコン発振器まで、幅広い発振器のポートフォリオを提供しています。シリコン発振器は、PGA、ASIC、マイクロプロセッサなどの一般的な用途に適したソリッドステート・クロックであり、同期とEMIの低減(スペクトラム拡散経由)を実現するため、スイッチング・レギュレータのクロックにも最適です。

関連ツール

ADIsimDDSは、数学の方程式を用いて、選択したデバイスの全体的な性能をモデル化し、表示します。ADIsimDDSは、リファレンス・クロック周波数と求められる出力周波数が与えられた場合に、必要なFTWを計算します。このツールは総合的なスペクトル性能全体の推定値もモデル化できるため、外付け再構成フィルタの効果を確認できます。

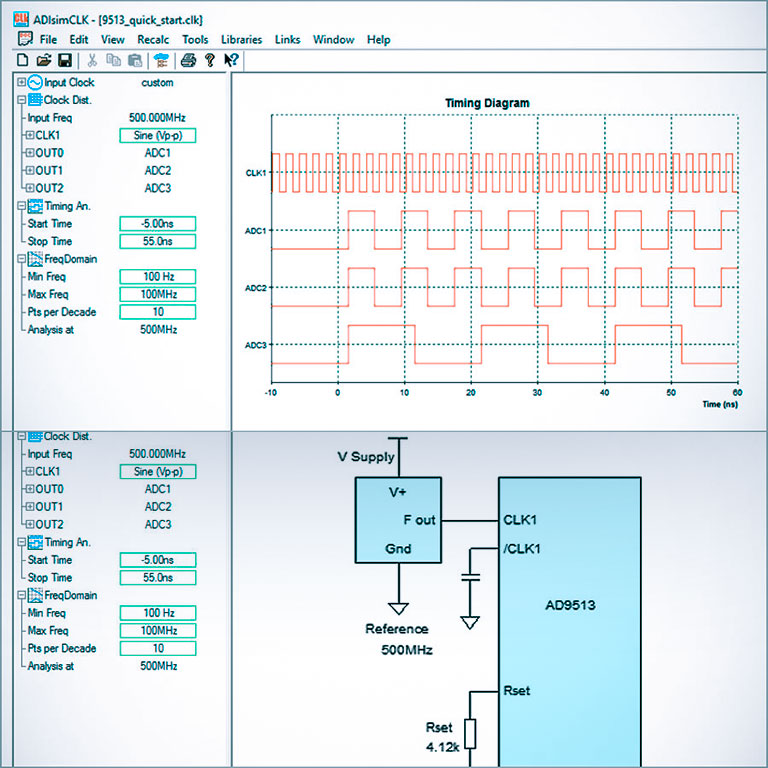

ADIsimCLKはアナログ・デバイセズの超低ジッタのクロック分配器とクロック生成製品向けに開発された設計ツールです。ADIsimCLKを使用すれば、ワイヤレス・インフラストラクチャ、計測器、ネットワーキング、ブロードバンド、ATE(自動試験装置)あるいはクロック性能が予測可能であることが求められるあらゆる分野のアプリケーションで、設計を迅速に開発、評価、最適化できます。

アナログ設計ツール:ADIsimCLK™

{{modalTitle}}

{{modalDescription}}

{{dropdownTitle}}

- {{defaultSelectedText}} {{#each projectNames}}

- {{name}} {{/each}} {{#if newProjectText}}

-

{{newProjectText}}

{{/if}}

{{newProjectTitle}}

{{projectNameErrorText}}