TNJ-024:電子回路で生じるコモンモード・ノイズと差動回路の活用

2016年11月7日公開

はじめに

TNJ-022, TNJ-023での広帯域アッテネータ回路を構成する話題で、「広い減衰範囲を実現するうえでの、飛び込みや迷結合の問題」ということを、何度もお話させていただきました。「具体的には、それらをどう考えるのか?」というのはもっともな疑問と思われます。

これは主に「コモンモード(同相モード)の飛び込みや迷結合」が原因です。しかしコモンモード、これが余計な成分となってしまうコモンモード・ノイズのしくみは、なかなか理解できないところではないかと思います。

このことについて、この技術ノートで考えてみたいと思います。

伊藤健一先生の名著「アースシリーズ」

私も若い、技術者駆け出しのころに、元大学教授、現在イトケン研究所の伊藤健一先生の、アナログ回路で一番大切なグラウンド = アースに関する名著、「アースシリーズ」(日刊工業新聞社)を、それも何冊も買い込み、むさぼるように読みました。先生のモノ(電子回路)への見方に「目から鱗」という感じでした。解説はイメージからの導入であり、わかりやすく、回路の動きが理解できる書籍でした。

この「アースシリーズ」を、あらためて最近、全15冊セットで入手できました(図1。◎フオクからです^^;)。さすがに現在は、これらの書籍は絶版なのでしょう…。

この「アースシリーズ」のなかで出てきた「コモンモード・ノイズ」と「ノルマル(ノーマル)モード・ノイズ」との違いについては、当時は理解できませんでした。しかしこれがTNJ-022とTNJ-023で出てきた「コモンモード・ノイズ」の原理だったわけです。

なお「コモンモード」は同相モードとか同相成分とも呼びます。一方「ノルマル(ノーマル)モード」は一般的な電圧(電位差)の考えで、対グラウンド(対地)を基準として電圧がどれだけあるかを示すものです。

一方で「コモンモード」はちょっとイメージが掴みにくいものかもしれません。

イトケン先生との思い出

伊藤先生が「イトケン先生」と呼ばれているのを知ったのは、「アースシリーズ」を読んでからのことでした。

私は、伊藤健一先生がいらっしゃった大学に1982年に入学しました。伊藤先生は電子工学科の教授で、私は電気工学科の学生と、別の学科でありました。

なぜ先生を存じ上げていたかは記憶がありませんが、当時から伊藤先生のお名前は知っており、2年生のときに先生の講義に(電子工学科の学生に混じって)出席した記憶があります。とても分かりやすい講義で、「象より重い象はいない」というお言葉を今でも覚えていますが、たしか「適切なサイズ(寸法という意味ではなく、電気的にという意味もあったかと思います)がモノにはある」というようなお話だったような記憶があります。

伊藤健一先生は、長らく東芝で実務をご担当され、それからアカデミックの世界に移られたようです。現在は退官され、退官後はイトケン研究所という会社を立ち上げて、コンサルティングをされていたようです。ネットでサーチすると研究所のHPは出てきませんが、活動されていたごようす。現在はご高齢なようですが、まだお元気でいらっしゃるのでしょうか。

貸した本は帰ってこない(汗)

その若い、駆け出しのころ、この「アースシリーズ」に多大なる影響(感銘)を受けた私は、自分が購入したこの数冊の本を後輩数人に「有益だから」と貸してあげました。「貸した」のですが、後になっても一冊も帰ってきませんでした(笑)。皆様、書籍は貸さずにその人に買ってもらいましょう(笑)。

ということで一冊も無くなっていた「アースシリーズ」。最近ワンセットで入手できたわけで、うれしいです(再度…図1)。でも読む時間もなさそうで、本棚に何年間並べておくことになるのでしょうか…。

撮った写真は、バックグラウンドのようすなど、それはまるで…、◎フオクの出品商品を見るような!?(笑)

コモンモード電圧は2点間のグラウンド電圧差異

コモンモード電圧は、異なる2点間のグラウンド電位が異なるために生じるものです。図2にそのしくみを示します。回路のうごきとしては、信号源VS(VSのSはSource; 「源」のS)に対して、付加電圧VC(VCのCはCommon; 「共通・同相」のC)が直列に接続されたものとして考えることができます。つまり、VSのプラス側とマイナス側が同じ電圧VC分だけオフセットして動いていると考えることができます。

このようにVSの端子両端が同じ電圧、同じ方向に動くことで「コモン(共通・同相)」な「モード」という感じで、コモンモード電圧を考えることができます。そしてこれが回路に対しては「コモンモード・ノイズ」となって悪影響を与えることになります。

この回路はシングルエンドですが、負荷端(一般的にはOPアンプなどのアナログ信号処理回路部分)で、VCがノイズとなって検出されてしまうという問題があります。

「こんなノイズ(電圧)、どうすれば発生するの?」と思われる方も多いかと思います。一般的にふたつの原因が考えられると思います。

ひとつめの原因「鎖交磁束による起電力」

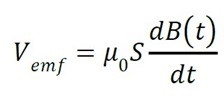

ひとつは図3のように、2点間のグラウンド配線と、信号配線とでできる、広いループの面積Sの中を変動磁界B(t)が通り抜け(これをより専門的には「鎖交磁束」と呼びます)、それが電磁誘導で、以下の式で電圧Vemfとして現れるものです。

ここでμ0は真空の透磁率、tは時間です(ガラエポ誘電体や銅パターンの比透磁率μrは約1なので、μ0のままで計算できます)。このVemfは回路がオープンになったときに、回路端子に現れる電圧で、閉回路一巡がインピーダンスZを持っている場合(もっと簡単にいうと「回路内に抵抗やインダクタンスが接続されている場合」)には、電磁誘導による回路全体の電流Iが

のように決定すると考えることができます(簡単化してイメージで考えるため、式中では複素数として示していません)。回路のインピーダンスZには、Vemfを生じる相互インダクタンスMに関わる、もれ磁束による自己インダクタンスも含まれます。

このように回路にノイズ電圧やノイズ電流が発生するわけです。

また鎖交磁束B(t)は周囲の電流変動により生じますが、一般的には50Hz/60Hzの商用電源による影響、機器内のスイッチング電源回路に流れる過渡的な電流による影響、そして機器内のデジタル回路部分の論理変化(スイッチング)による影響などが考えられるでしょう。

また以降でも出てきますが、Vemf=μ0 SdB(t)/dtであり、リアクタンスX = 2πfM (or 2πfL)なので、それぞれ周波数fに比例する(dB(t)/dtの影響は変動速度に比例する)ことから、周波数が高くなってくると厄介になってくるだろうということが分かると思います。これがコモンモードによるノイズになるわけです。

ふたつめの原因「グラウンド・ラインに流れる電流による電圧降下」

もうひとつの「コモンモード電圧」の発生する原因としては、グラウンド・ラインに別の回路の電流が流れることにより電圧が生じるというものです。このようすを図4に示します。

2点のグラウンド・ポイント間には「インピーダンスZG(ZGのGはGroundのG)」が当然生じます。物理的に位置が異なるわけで、またその間を接続するリード線やケーブルがあるわけですから、これらの導体には、導体抵抗と、導体に生じるインダクタンスが存在することになります。

これらが2点のグラウンド・ポイント間の「インピーダンス」となります。この「インピーダンス」に対して、他の回路(これも原因としてはひとつめで説明した、①商用電源、②スイッチング電源回路、③デジタル回路部分、などが理由として挙げられます)の電流が流れることにより、電圧降下が生じ、コモンモード電圧が発生することになります。

ここでもインピーダンスのうち、インダクタンス成分が厄介で、生じるリアクタンスはX = 2πfLなので、周波数fに比例することから、周波数が高くなってくると影響度が大きくなってしまいます。

「グラウンド・ラインに流れる電流による電圧降下」の影響をシミュレーションで見てみる

図の説明だけだとリアリティが少ないので、ADIsimPEを使ったシミュレーションでこのようすを再現してみたいと思います。

図5はADIsimPEで2点のグラウンド・ポイント間の「インピーダンスZG」をモデル化したものです。おおよそ100mmの信号ライン用のパターン(パターン幅は0.4mm程度の一般的な幅を想定)をグラウンドのパターンとして用意し、それにより2点のグラウンド・ポイント間を接続したものとして設定してみました。

さきの「他の回路」として説明した信号(電流I)は、1kΩの負荷抵抗に流れる5V CMOSデジタルのスイッチング信号とし、ここでは変動周波数が問題になるというより、論理変化(スイッチング)時に過渡現象的にインダクタンスが応答することのほうが問題になることが容易に予想できると思います。

過渡現象的に応答することを考慮して、意識的に、デジタル信号の立ち上り時間/立下り時間を10nsとして若干低速なロジック回路を設定してみました。アナログ信号源は200mVp-pです。

シミュレーションの結果を図6に示します。立ち上り時間/立下り時間が低速ぎみでもこんなに大きなノイズ(実際はコモンモード電圧/コモンモード・ノイズ)が観測されています!これが負荷端(アナログ信号処理回路部分)に加わるわけですから、とても嫌な成分が生じてしまうわけですね。「見ただけで厄介そうだなあ…」と思われるのではないでしょうか。これがコモンモードによるノイズになるわけです。

神の方式「差動伝送/差動回路」

2つの信号ラインを用いて、それも相互に逆相の信号を用いて、ひとつの信号情報を伝送する「差動伝送」とか「差動回路」と呼ばれる方式があります。これは図7のように表すことができます。この方式が、これまで示してきたようなコモンモードによる問題、「コモンモード・ノイズ」を低減させるために非常に有効なものとなります。それこそ「神の方式」なんて呼んでも良いかもしれません。

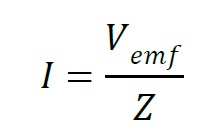

元々の信号情報をVD(VDのDはDifferential; 「差動」のD)とすると、差動信号ではV+ = +VD /2、V- = -VD /2の2信号を伝送します。ここにコモンモード電圧VCが加わったことを考えてみましょう。コモンモードが加わった差動回路のそれぞれの「基準電位から見た」端子電圧は、

となります。VP(VPのPはPositive; 「正極性」のP)は差動回路の正側Line(+)の受信端における対地(対グラウンド)電圧、VN(VNのNはNegative; 「負極性」のN)は同じく負側Line(-)の対地電圧です。

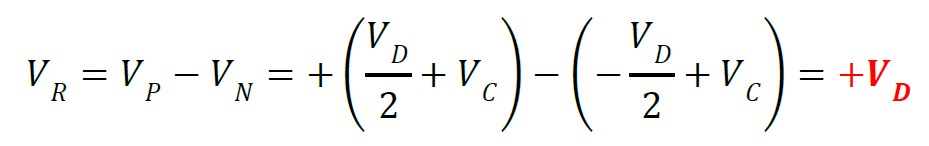

差動回路の受信端では、VPとVNを「引き算」の処理を行うことで、受信信号VRを

として得ることができます。VCが消えていますね!

このように差動回路の原理で、コモンモード電圧をキャンセルすることができるわけですね。

差動回路では偶数次歪みもキャンセルできる

もう少しオマケですが、差動回路では偶数次の歪みもキャンセルすることができます(奇数次はキャンセルできません)。たとえば、図8のような回路で送信端(出力端)から受信端(入力端)にかけて、途中に非線形な要素があったことを考えてみます。ここでは2次の成分があったとします。

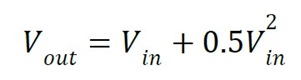

これをADIsimPEでモデル化してみたものを図9に示します。図中にあるARB1, ARB2ブロックは、

と自乗の要素を持っています。自乗の要素というのは、「2」乗であり、このために「偶数次」の項というわけです。

この「偶数次」の項は、自乗(もしくは4, 6, 8, …)の要素に対して、+1Vが入れば+1Vになりますが、-1Vが入っても+1Vになる、つまり絶対値の要素を持っているものです。そうすると差動の端子、VPとVNで同じ極性の信号、つまりコモンモード電圧VCと同じような成分が出来てしまうことになります。

この成分をVCとして先の引き算処理の式で考えれば、この偶数次歪みが重畳した差動信号を、受信端で差動受信(つまり引き算)することで、偶数次の歪み成分がキャンセルされることが分かります。

図9のADIsimPEのモデルでシミュレーションしてみたようすを図10に示します。VP, VN(図中下)には2次の成分による歪みが生じていますが、それを差動受信したVD(図中上)ではその2次の成分が消えて、本来の信号であるVD = 2×VSが得られていることが分かります。

本当に差動回路は神の方式なわけですね!といっても繰り返しますが、奇数次の歪みは(+1Vが入れば+1Vに、-1Vが入れば -1Vになるため)残念ながらキャンセルすることができません。

神の差動回路に生じる現実世界での限界

この単純理論だけで考えれば、差動伝送や差動回路は超素晴らしいものといえるでしょう。しかし現実は図11や図12に示すように、回路内にいろいろなアンバランスな要因が存在します。このアンバランスにより、「神の差動回路」も現実世界での限界が露呈してしまうことになります。

ひとつめの原因「各差動線路への結合度の違い」

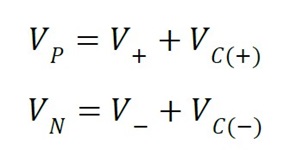

図11は差動の各線路Line(+), Line(-)に加わる(生じる)コモンモード電圧のレベル自体が異なる、つまりノイズ源からの結合度に違いがあるケースです。式で表すと

ここでVPは差動回路の正側Line(+)の受信端における対地(対グラウンド)電圧、VNは負側Line(-)の受信端における対地電圧です。また差動信号は|V+ |=|V- |ですが、コモンモード電圧が|VC(+) |≠|VC(-) |となるケースです。これはコモンモード電圧を発生させる要因が、各差動線路Line(+), Line(-)に結合する量として異なっているというものです。

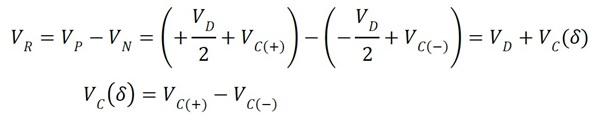

これにより差動受信したとしても、

となり、コモンモード成分VC (δ)が差動信号のオバケ成分(余計な成分)として、受信信号VRに混じってしまいます。

ふたつめの原因「各差動線路のアンバランス」

図12は差動の各線路Line(+), Line(-)の特性が異なる(アンバランスな)ケースです。各部分のインピーダンスが異なるものです。式で表してもいいでしょうが、これは直感的にも理解できると思いますので、式では示しません。

その替わりに、このようすをモデル化して、シミュレーションで特性の変化する様子を見てみたいと思います。

図13は図12をADIsimPEのうえでモデル化したものです。付加されているLやCは浮遊成分として考えられるもので、ケーブル/プリント基板パターンの浮遊インダクタンスや、プリント基板パターン間の浮遊容量などに相当します。

この系でコモンモード電圧VCが出力に現れる率をシミュレーションし、dBで表してみた結果を図14に示します。

このように「コモンモード電圧VCが差動出力に現れている」ことが分かると思います。このしくみにおいても、コモンモード信号成分が差動信号のオバケ成分(余計な成分)として、受信信号VRに混じってしまいます。

周波数が高くなってくると影響度が大きくなる

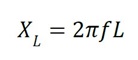

図14において、さらに興味深いこととして、周波数が高くなってくると「コモンモード電圧VCが差動出力(受信信号VR)に現れる量」が大きくなっていることが結果から分かります。これはインダクタンスL [H]はリアクタンスXLとなり(先にも示したように)、

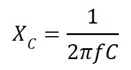

として周波数に比例して大きくなり、この浮遊インダクタンス成分に周波数f [Hz]の電流I(f)が流れると、同じ電流量でも周波数f に比例して電圧降下が大きくなる、つまり影響度が大きくなります。また容量C [F]もリアクタンスXCとなり、

として周波数に比例して小さくなり、このような浮遊容量成分は一般的に回路に対して並列に(シャントのかたちで)接続されることとなり、回路に周波数f の電流I(f)が流れると、この本来の回路以外である「並列に接続されたかたちの浮遊容量成分」に電流が流れ出てしまうことで、同じ電流量でも周波数に比例して影響度が大きくなることが分かります。

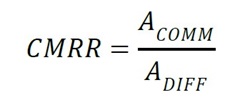

差動回路で重要な概念「CMRR」

ここで重要な概念が出てきます。CMRR(Common Mode Rejection Ratio)というものです。考え方は簡単で、図12のような回路で、差動信号成分に対する利得をADIFFとし、コモンモード電圧成分に対する利得をACOMMとすれば、

と計算できます。図12ではADIFF=1として記載しています。CMRRは日本語で言うと「コモン(同相)モード除去比」で、結局、系としてどれだけコモンモードの影響を低減できるのか、というものだということも分かります。

図15にADA4891-1のCMRRの特性グラフを示します。このように周波数が上昇してくるとCMRRが低下してくることが分かります。これは結局ICの内部であっても、先に示した

- 周波数が高くなってくると「コモンモード電圧VCが差動出力(受信信号VR)に現れる量」が大きくなる

- 浮遊インダクタンスに電流I(f)が流れると、同じ電流量でも周波数に比例して電圧降下が大きくなる

- 並列に接続されたかたちの浮遊容量成分に電流が流れ出てしまうことで、同じ電流量でも周波数に比例して影響度が大きくなる

という話しと同じであることがお分かりいただけると思います。

TNJ-023で示したCMRR向上やコモンモード・ノイズ低減のための戦略とその意義

TNJ-023で3つの点、

- 同相モードによる出力への影響を避けるために、TNJ-023での図8の回路図のように、出力アンプは一旦差動で受けて、シングルエンドに変換する構成にした

- 出力アンプとして使っているADA4891-1はCMRR @30MHz = -27dB程度なので、これに合わせて入力の抵抗4本は絶対精度0.5%(相対マッチングはさらに良いはず)のVISHAYのACASA100121001P100というものを使った

- グラウンドも網目のようにしてビア接続し、できるだけL1 - L2間で低いインピーダンスが実現できるように、ベタの配置、ビアでの接続を心がけた

を記載しておりました。

①はこれまでの説明で、シングルエンドの回路と比較して、「いかに差動回路が有効か」でご理解いただけるものと思います。

また②については、この数値的な比率関係を説明すると話が長くなってしまいますが、ADA4891-1の持つCMRR特性を低下させないようにしているためで、この技術ノートでも図12で示した「各差動線路Line(+), Line(-)の特性が異なる(アンバランスな)場合」と同じしくみになります。詳細は参考文献[1]のp. 161以降に記載がありますので、ご興味あるかたはご覧ください。

最後に③についてご説明しておきましょう。

グラウンドのインピーダンスを下げることでのコモンモード・ノイズ低減へのメリット

これも本当はここまでの議論からすれば、詳しく説明するほどでも無いかもしれません。

電流によって生じる電圧降下(グラウンド間電位差)がコモンモード電圧VCのひとつの原因になりますが、これが図12で示した「各差動線路Line(+), Line(-)の特性が異なる(アンバランスな)ケース」のしくみにより、差動出力(受信信号VR)の上に現れてしまいます。

ここでもし、「各差動線路Line(+), Line(-)のアンバランス」を良化させることに限界があり、差動出力(受信信号VR)に現れるコモンモード電圧VCを低く抑えたいのであれば、コモンモード電圧VC自体を低下させればいいのです。しくみは図16のとおりです。これが先に示した、「グラウンドも網目のようにしてビア接続し、できるだけL1 - L2間で低いインピーダンスが実現できるように、ベタの配置、ビアでの接続を心がけた」ということなのです。

コモンモード電圧VCのひとつのしくみ(要素)は、「電流によって生じる電圧降下」ですから、グラウンドのインピーダンスを下げれば、電圧降下を低減でき、差動出力に現れる量を低減できるわけですね。

またグラウンドに流れるリターン電流は、図17のように、たとえベタ・グラウンドであっても、導体を形成する銅に抵抗率が存在するために、電流は2点間を直線的に流れず、周囲にも流れていくことになります。離隔すればするほど当然電流量は低下していきますが、ゼロではありません。

高精度、高ダイナミックレンジのシステムでは(それもTNJ-022やTNJ-023で取り上げたような高減衰量のアッテネータなどは)、余計な迷結合を十分に防ぐ必要もあるわけで、この広い面を広がって流れる電流の影響にも注意する必要があります。

ここまでの話しと、それぞれ原理的にも相互に繋がっていることが分かります。

まとめと参考文献

これらの話題は、拙書「アナログ・センスで正しい電子回路計測[2]」にも非常に詳しく記載しております。よろしければご覧ください。「回路の動作」も「正しい計測」も全く同じということなんですね。

参考文献

[1] アナログ・デバイセズ; OPアンプによる増幅回路の設計技法, OPアンプ大全第4巻, CQ出版社

[2] 石井 聡; アナログ・センスで正しい電子回路計測, CQ出版社

著者について

デジタル回路(FPGAやASIC)からアナログ、高周波回路まで多...