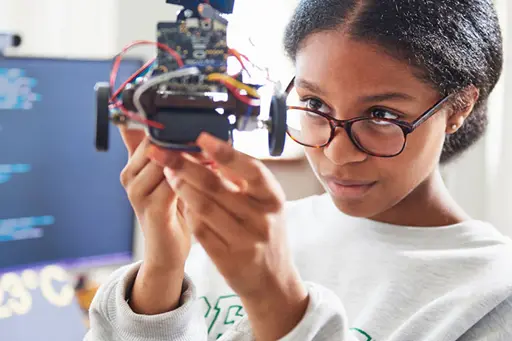

AIが現実になる場所

アナログ・デバイセズがフィジカル・インテリジェンスを解き放ち、自律型工場、知能ロボット、ソフトウェア・デファインド・ビークル、予測ヘルスケア・システムにおける新たなフロンティアを可能にする仕組みをご覧ください。

AIが現実になる場所

アナログ・デバイセズがフィジカル・インテリジェンスを解き放ち、自律型工場、知能ロボット、ソフトウェア・デファインド・ビークル、予測ヘルスケア・システムにおける新たなフロンティアを可能にする仕組みをご覧ください。

データセンターの800Vホットスワップ

AIが48Vから800Vへの電力供給移行を進める中、アナログ・デバイセズは次世代の高電圧ホットスワップ保護を提供し、堅牢でスケーラブルなデータセンター電源を確かなものとします。

データセンターの800Vホットスワップ

AIが48Vから800Vへの電力供給移行を進める中、アナログ・デバイセズは次世代の高電圧ホットスワップ保護を提供し、堅牢でスケーラブルなデータセンター電源を確かなものとします。

パワー・マネージメント・ツール

ADI Power Studio™は、電源設計の全工程に対応する包括的なツール・ファミリです。設計プロセスのあらゆる段階において、設計の早期検証、効率的なアーキテクチャの最適化を支援します。

パワー・マネージメント・ツール

ADI Power Studio™は、電源設計の全工程に対応する包括的なツール・ファミリです。設計プロセスのあらゆる段階において、設計の早期検証、効率的なアーキテクチャの最適化を支援します。