AN-2625: 使用多片ADE ADC进行设计

引言

本应用笔记阐述了如何设计和配置一个采用多片ADE 系列ADC的系统。

受支持的器件

配置

菊花链SPI

要求

以下列表概述了菊花链串行外设接口(SPI)配置的各项要求:

- 所有器件必须使用同一时钟源运行。

- 所有器件必须共用一个片选(CS)信号。

- 仅需单个器件提供数据就绪(DREADY)信号输出。

- 有关更多信息,请参见数据就绪引脚(DREADY)部分。

多片选SPI

要求

以下列表概述了多片选SPI配置的各项要求:

- 每个器件都必须接入独立的片选(CS)信号。

- 若要实现ADC同步,请参见以下要求:

- 所有器件必须使用同一时钟源运行。

- 所有CS线路必须能够同步切换。

- 仅需单个DREADY信号输出。

- 如果无需ADC同步,请参见以下要求:

- 所有器件可使用不同的时钟源运行。

- CS线路无需同步。

- 所有DREADY 信号输出必须分别接入微控制器。

- 有关更多信息,请参见数据就绪引脚(DREADY)部分。

设计/软件考量

以下部分概述了在设计搭载多片ADC的电路板时,需注意的部分设计考量要点。

缓冲SPI SCLK

如果多片ADC间距较大,建议使用1:x扇出缓冲器(x为链路中的ADC数量)。这可消除SCLK走线的分支;在SPI高速运行时,分支可能导致信号反射和信号完整性问题。同时,这也能缩短单条走线所需的最大长度。对于高速SPI场景,需使用低延迟的扇出缓冲器;详见图3。

缓冲MCLK

与缓冲SPI SCLK类似(参见缓冲SPI SCLK部 分 ),建议对MCLK信号进行缓冲,以减少分支和走线长度。实现方式有两种:一是使用与SPI SCLK相同的低延迟扇出缓冲器,二是利用 ADC 自身对其时钟进行缓冲。所有受支持的 ADC(ADEMA12x 和ADE91xx)均具备在CLKOUT/DREADY引脚上输出MCLK 的功能(详见受支持的器件部分)。在图4中,ADC1的XTALIN/XTALOUT引脚连接了晶体,用于生成 MCLK。ADC1 和 ADC2 被配置为在其CLKOUT/DREADY 引脚上输出 MCLK,用于为下一个器件的XTALIN供电。链路中的最后一个器件(本例中为ADC2)被配置为输出DREADY(数据就绪),该信号被馈入MCU,用于向 MCU示意可从ADC读取新数据。

注意,如果链路中存在ADE91xx器件,请勿将其用作时钟源(图4中的ADC1)。使用ADEMA12x提供时钟。

ADC同步

当多片ADC 连接至同一SPI 总线时,所有器件的ADC 采样可实现±1个MCLK周期的同步。所有ADC需采用相同的MCLK源,并以相同的输出数据速率运行。在多片选配置中,所有片选线必须能够同时置为低电平。有关多片 ADC 同步的更多信息,请参见ADEMA124/ADEMA127 数据手册中的“多器件同步”部分,以及ADE9103/ADE9112/ADE9113 数据手册中的“ 多 ADE9103/ADE9112/ADE9113 器件同步”部分。此外,本应用笔记中的同步/快照流程部分提供了同步操作的分步指南。

使用 ADEMA124/ADEMA127 搭建菊花链时的注意事项

如果菊花链中包含ADEMA124或ADEMA127器件,每当DATAPATH_CONFIG_LOCK 被切换时,ADC转换都会暂停后再恢复(详见ADEMA124/ADEMA127数据手册的“配置锁定与访问位”部分),这可能导致ADC之间的同步丢失。

以下部分探讨了两个解决方案,可以确保在切换 DATAPATH_CONFIG_LOCK 后仍能保持ADC同步。

解决方案1(推荐)

在切换任何器件的DATAPATH_CONFIG_LOCK 后,重新同步所有ADC。该解决方案适用于所有器件组合(ADEMA12x和ADE91xx)。此方法受 ADC服务支持。能源ADC 服务提供了一套可用于与ADI 计量 ADC 通信的 API。ADC 服务链接: https://github.com/analogdevicesinc/energy-adc-service。

解决方案2:

如果链路中的所有器件均为ADEMA12x系列,则可通过单次 SPI 事务禁用并重新启用 DATAPATH_ CONFIG_LOCK(即所有器件同步解锁与锁定),从而保持ADC同步。此方法未在ADC服务中实现。

同步/快照程序

本节将分步介绍如何在菊花链和多片选SPI两种配置下实现ADC同步,并验证同步对齐情况。

菊花链SPI配置

对齐和测量

以下步骤概述如何执行 ADC 同步,并通过测量验证对齐效果:

向所有器件的 SYNC_SNAP 寄存器(0x14)写入0x2。

- 将ALIGN位设置为1。

2. 读取所有器件的SNAPSHOT_COUNT_HI (0x17)和SNAP-SHOT_COUNT_LO (0x18)寄存器。

3. 向所有器件的 SYNC_SNAP 寄存器(0x14)写入 0x1。

- 将SNAPSHOT位设置为1。

4. 读取所有器件的SNAPSHOT_COUNT_HI (0x17) 和SNAP-SHOT_COUNT_LO (0x18)寄存器。

5. 比较各 ADC 同步后的 SNAPSHOT_COUNT_x 寄存器值,以确认同步操作是否正确执行。

- 所有数值偏差必须在±1个计数范围内。

仅测量

1.向所有器件的 SYNC_SNAP 寄存器(0x14)写入 0x1。

- 将SNAPSHOT位设置为1。

2. 读取所有器件的SNAPSHOT_COUNT_HI (0x17) 和SNAP-SHOT_COUNT_LO (0x18)寄存器。

3. 比较各ADC的SNAPSHOT_COUNT_x寄存器值,确认同步状态。

多片选SPI配置

对齐和测量

以下步骤概述如何执行 ADC 同步,并通过测量验证对齐效果:

1. 向所有器件的 SYNC_SNAP 寄存器(0x14)写入 0x6。

- 将ALIGN位设置为1。

- 将PREP_BROADCAST位设置为1。

2.同时读取所有器件的 SNAPSHOT_COUNT_HI (0x17)和 SNAP-SHOT_COUNT_LO(0x18)寄存器。

- 所有器件的CS信号必须同时从高电平切换至低电平。

向所有器件的 SYNC_SNAP 寄存器(0x14)写入 0x5。

- 将SNAPSHOT位设置为1。

- 将PREP_BROADCAST位设置为1。

4. 同时读取所有器件的SNAPSHOT_COUNT_HI (0x17)和SNAP-SHOT_COUNT_LO (0x18)寄存器。

5.比较各ADC同步后的SNAPSHOT_COUNT_x 寄存器值,以确认同步操作是否正确执行。

- 所有数值偏差必须在±1个计数范围内。

仅测量

“仅测量”模式可用于定期测量ADC之间的同步状态。如果同步偏差超出预期范围,应用可据此进行重新同步。

1.向所有器件的SYNC_SNAP寄存器(0x14)写入0x5。

- 将SNAPSHOT位设置为1。

- 将PREP_BROADCAST位设置为1。

2.读取所有器件的SNAPSHOT_COUNT_HI (0x17) 和SNAPSHOT_COUNT_LO (0x18)寄存器。

3. 比较各ADC的SNAPSHOT_COUNT_x寄存器值, 确认同步状态。

数据就绪引脚(DREADY)

每个受支持的ADC均配备一个名为CLKOUT/ DREADY的数据就绪引脚(DREADY)。顾名思义,该引脚可配置为输出MCLK或数据就绪信号。当数据就绪信号从高电平跳变为低电平时,表明可从ADC读取新的ADC数据。此信号的频率取决于ADC运行的数据速率(详见受支持的器件部分)。若要实现同步,所有ADC必须使用相同的MCLK源,并以相同的数据速率运行。因此,如果在菊花链配置中同时使用ADEMA12x和ADE91xx ADC,仅支持特定的数据速率(参见表1)。一旦所有ADC完成同步(参见ADC同步部分),所有器件的数据就绪信号也将同步。因此,只需将一个DREADY输出信号接入主机MCU即可。如果无需ADC同步,则必须将所有DREADY引脚均接入微控制器。

| 数据速率 | ADEMA12x2 | ADE91xx2 |

| 64ksps | X | |

| 32ksps | X | X |

| 16ksps | X | |

| 8ksps | X | X |

| 4ksps | X | X |

| 2ksps | X | X |

| 1ksps | X | X |

| 500sps | X | |

| 250sps | X |

菊花链配置下的ADC最高采样率

在菊花链配置中,所有ADC共用同一条SPI总线。因此,链路中的ADC数量越多,SPI帧需要传输的数据量就越大。基于此,在特定SPI速率和ADC数量下,系统支持的最高输出数据速率会受到限制。所有ADC必须配置为以长格式输出数据(详见受支持的器件部分)。如需使用SPI隔离器,务必在计算中纳入隔离器的传输延迟(有关使用隔离器时的注意事项,详见AN-1478应用笔记《满足不同系 统要求的隔离式SPI总线》)。

计算步骤如下:

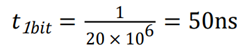

1. 计算1位传输时间,即传输1位数据所需的时间(单位:秒)。

2. 计算帧长度,即整个传输帧的总位数。

| ADC | 帧长度(位) |

| ADEMA124 | 160 |

| ADEMA127 | 256 |

| ADE9113 | 128 |

| ADE9112 | 128 |

| ADE9103 | 128 |

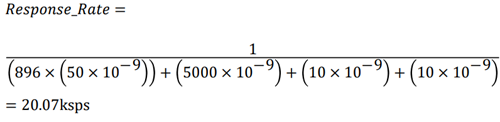

3.计算响应速率,即为了支持目标配置所需达到的最低采样率,单位为“次采样/秒”。

其中,

tCH = SPI事务之间的CS高电平时间(ns)。

tSS = CS至SCLK上升沿的时间(ns)。

tSFS = SPI事务之间的CS高电平时间(ns)。

4. 可通过查询表,选择受支持的数据速率(受支持的数据速率参见表1)。

成功范例

链路中包含4片ADC:1片ADE9113 + 3片ADEMA127,

其中

SCLK = 20MHz、 tCH = 5000ns、 tSS = 10ns和 tSFS = 10ns。

计算过程如下:

1.

2. 帧长度 = 128 + 256 + 256 + 256 = 896 位

3.

4.由于ADE9113 与ADEMA127 搭配使用时,仅支持特定的数据速率;且ADE9113不具备16ksps(千采样/秒)选项,因此支持的最高数据速率为8ksps。

| 数据速率 | ADEMA12x1 | ADE91xx1 |

| 64ksps | X | |

| 32ksps | X | X |

| 16ksps | X | |

| 8ksps | X | X |

| 4ksps | X | X |

| 2ksps | X | X |

| 1ksps | X | X |

| 500sps | X | |

| 250sps | X |

示例

以下部分将以1片ADE9113与3片ADEMA127组成的菊花链配置为例进行说明。

硬件设置

按照图6所示,将主机微控制器(MCU)与4片ADC连接。

ADC配置

以下列表概述了如何为菊花链配置对ADC进行设置:

- 配置所有 ADEMA127 器件,使其在 CLKOUT/

DREADY 引脚上输出 MCLK。具体操作是向

ADE-MA127 器件的 CONFIG0 (0x2)寄存器中的

CLKOUT_EN 位写入0x1。

需按“ 链路中第1片ADC(与主机MCU的MOSI引脚直接连接的器件)→ 第2片ADC → 第3片ADC”的顺序写入配置,确保后续待配置的ADC 在通信前已获取MCLK。 - 配置所有器件,使其采用相同的输出数据速率(详见数据就绪引脚(DREADY)部分和菊花链配置下的ADC最高采样率部分)。

对于ADEMA127,通过向DATARATE (0x03C)寄存器写入数据来设置输出数据速率(详见ADEMA124/ADEMA127 数据手册的“输出采样率”部分)。

对于ADE9113,通过向CONFIG_FILT (0x3)寄存器的 DATA-PATH_CONFIG[2:0]位写入数据来设置输出数据速率。 - 对ADC进行同步。有关更多信息,请参见ADC同步部分。

软件配置

能源ADC服务提供了一套可用于与ADI计量ADC通信的API。ADC服务链接: https://github.com/analogdevicesinc/energy-adc-service。