アプリケーション・ノート使用上の注意

本アプリケーションノートの英語以外の言語への翻訳はユーザの便宜のために提供されるものであり、リビジョンが古い場合があります。最新の内容については、必ず最新の英語版をご参照ください。

なお、日本語版のアプリケーションノートは基本的に「Rev.0」(リビジョン0)で作成されています。

AN-2020: 電源の自動化アプリケーション向けに優れた EMC 性能を備えた、AD7606B ADC ベースの PCB 設計

はじめに

AD7606Bは、8チャンネル同時サンプリングの16ビットA/D変換データ・アクイジション・システム(DAS)です。各チャンネルには、1個の逐次比較レジスタ(SAR)A/Dコンバータ(ADC)が内蔵されています。AD7606Bは、保護リレー・システム、マージング・ユニット・システム、その他の過酷な環境で使用される2次側電源の自動化デバイスなど、電源の自動化システムで使用できるように設計されています。これらのシステムでは、電磁両立性(EMC)の設計が最も重要です。

このアプリケーション・ノートでは、EMCボード・レベルの設計と、電流・電圧検出回路のインターフェースにおいてAD7606Bを標準的なアナログ・フロント・エンド(AFE)として使用する場合のガイドラインについて説明します。

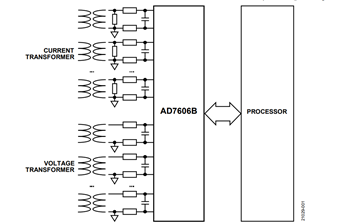

電源の自動化システムにおけるAD7606Bの代表的な使用例

図1に、電源の自動化システムにおけるAD7606Bの代表的な使用例を示します。標準的な構成では、AD7606Bは、シンプルなRCベースのローパス・フィルタを介して電流トランスまたは電圧トランスに接続します。

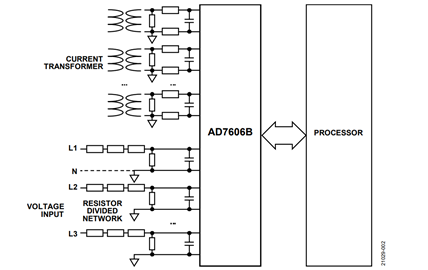

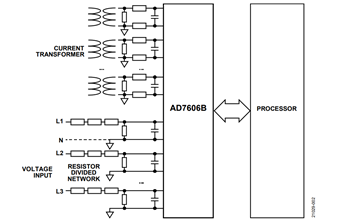

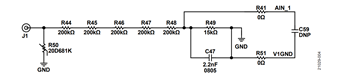

AC220V~380Vの電力量計システムのような低電圧アプリケーションでは、電圧トランスの代わりに抵抗分圧ネットワークを使用して電圧を測定することもできます(図2参照)。この回路の入力はアイソレーションなしに直接送電系統と接続されているため、AFE部品には送電系統からの電気的な衝撃に耐えられるだけの堅牢性が必要です。

EMC規格

一般に、商用AC電源には電気的な衝撃が数種類存在します。AD7606Bの堅牢性の試験では、EMC規格に基づく3種類の電気的衝撃をAD7606BベースのEMCテスト・ボードに加えます。

IEC 61000-4-2:静電放電(ESD)

AD7606BベースのEMCテスト・ボードに加える電気的衝撃の1つめは、IEC 61000-4-2で規定される静電気放電(ESD)です。ESDサージは、ほとんどの電源自動化装置に影響を与えます。ESD試験では、接触、短絡、または絶縁破壊によって2つの帯電した物体間に発生する急激な電気の流れをシミュレートします。

IEC 61000-4-2規格では接触放電法と気中放電法で試験が行われます。接触放電法は、2kV~8kVの範囲で規定された4つのレベルで試験します。気中放電法では、2kV~15kVの試験が行われます。電源自動化装置は、レベル4のESD試験に合格する必要があります。そのため、8kVの接触放電と15kVの気中放電をAD7606Bテスト・ボードに適用してデバイスの堅牢性を検証します。ESD試験のセットアップとESDの試験波形については、IEC 61000-4-2規格を参照してください。

IEC 61000-4-4: 電気的ファスト・トランジェント(EFT)/ バースト・トランジェント

AD7606BベースのEMCテスト・ボードで行うもう1つの電気的衝撃試験は、IEC 61000-4-4に規定された電気的ファスト・トランジェント(EFT)/バースト・トランジェントです。この規格では、送電系統で繰返し発生するEFTとバーストに対する装置の耐性を調べます。

IEC 61000-4-4規格では、2つの繰返し周波数による4つの試験電圧レベルが定義されています。また、システムのポートを電源ポートと信号入出力ポートに分類しています。AD7606Bの一般的な用途は、送電系統の電圧および電流測定であるため、AFE回路は送電系統に直接接続されます。したがって、AD7606BベースのAFE回路に関しては、すべての入力ポートが電源ポートとみなされます。

電源自動化装置はレベル4のEFT/バースト試験に合格する必要があります。そのため、4kVの電圧をAD7606B EMCテスト・ボードに印加してデバイスの堅牢性を検証します。

IEC 61000-4-5:サージ

AD7606BベースのEMCテスト・ボードで行う3つめの電気的衝撃試験は、IEC 61000-4-5のサージ試験です。サージ試験では、雷や産業活動によって発生する送電系統からのサージに対する装置の耐性を調べます。

IEC 61000-4-5規格では、波形の組み合わせが2種類規定されています。それぞれの波形は、試験するポートの種類に応じて異なります。10/700μsの波形の組み合わせは、対称通信線に接続されたポートの試験に使用します。1.2/50μs(電圧)または8/20μs(電流)の波形の組み合わせは他のすべての場合に使用します。特に、1.2/50μsまたは8/20μsの波形は、電力線や距離の短い信号線との接続用に用意されたポートの試験に使用します。AD7606Bが対象とするアプリケーションは電力線の測定です。したがって、EMC試験では1.2/50μs(電圧)または8/20μs(電流)の波形の組み合わせを使用します。

電源の自動化システムにおけるAFEでは、電圧チャンネルの入力は高インピーダンスです。したがって、電圧チャンネルの入力には1.2/50μsの電圧波形を印加します。また、通常、電流チャンネルは低入力インピーダンスです。したがって、電流入力チャンネルには8/20μsの電流波形を印加します。

電源自動化装置はレベル4のサージ試験に合格する必要があります。4kVのコモンモード電圧と2kVの差動電圧をAD7606B EMCテスト・ボードの入力ポートに印加して、装置の堅牢性を検証します。

EFT/バースト試験のセットアップとESDの試験波形については、IEC 61000-4-5規格を参照してください。

EMC試験で起こりうるADCの故障

このアプリケーション・ノートで使用するEMC試験用プリント回路基板(PCB)は、EMCに関する3種類の電気的衝撃に対するAD7606Bの堅牢性の検証を目的に設計されています。PCBを設計する前に、SAR ADCがEMC試験によってどのように故障するか、および故障をどのように監視するか検討します。

代表的な故障の1つに、ADCの内部ロジックのラッチ・アップが挙げられます。この故障が発生していると、SAR ADCはホストから変換信号を受信したときに、適切にビジー信号を駆動してホストにアクノレッジすることができません。AD7606Bにこのような故障が発生していることを監視するため、ホスト・プロセッサは変換トリガをADCに定期的に送信します。変換トリガを送信した後、プロセッサはビジー信号がハイになるかどうかチェックするために約50ns待ちます。そして次に、ビジー信号がローになるかどうかチェックするために更に5μs待ちます。ビジー信号をチェックすることで、プロセッサはこのタイミングがAD7606Bデータシートの仕様の範囲内にあるかどうかを判断します。

他に、電源投入時に強い外部干渉が発生するとSAR ADCの内部レジスタが誤って初期化されてしまうという故障があります。この故障は、SAR ADCが自己診断機能を備えていないと監視が困難です。しかし、AD7606Bは、内部メモリのデータ破損を特定するステータス・レジスタを1つ備えており、電源投入時にデータが冗長巡回検査(CRC)をパスできるかどうかを識別します。

ADCは、EMC試験中に誤ってリセットされることがあります。AD7606Bのステータス・モニタ機能は、ステータス・レジスタを定期的にチェックすることでEMC試験中にトリガされるパーシャル・リセットを特定します。また、ステータス・レジスタをホスト・プロセッサで監視することによって、AD7606Bが誤ってリセットされたかどうか知ることも可能です。

EMC試験中に、電圧リファレンスや内部電源など、ADCの内部信号にエラーが発生することがあります。AD7606Bは、内部信号と内部LDO出力をサンプリングして変換することができます。ホスト・プロセッサでADCに内部信号とLDO出力をサンプリングさせることが可能で、これもEMC試験中にADCの状態を監視する方法の1つです。

EMC試験用PCBの機能およびシステムの説明

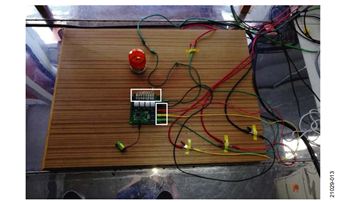

EMCテスト・ボードには、抵抗分圧ネットワークを使用する4個の電圧チャンネルが搭載されており、100V AC信号の減衰と測定を行うことができます。この回路は、抵抗分圧ネットワークを使用していることで絶縁バリアがなく、AD7606Bの入力がEMC干渉の入力に直接接続されるため、EMC試験において重要となります。

また、EMCテスト・ボードには標準的な電流トランスを使用する4個の電流チャンネルが搭載されており、20Aの電流信号を検出できます。電流トランスによってシステムの入力ポートとAD7606Bの入力の間に絶縁バリアがあるため、EMC干渉のほとんどはブロックすることができます。

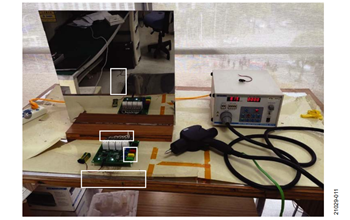

内蔵のマイクロプロセッサがサンプリングを制御し、変換データ、タイミング、ステータスをチェックします。プロセッサがADCの故障を発見すると、故障LEDが点灯します。故障LEDの色によってどのような故障が発生したかが分かります。故障LEDが試験中に光らなければ、AD7606Bは堅牢です。故障LED以外に、試験中に点滅し続けるもう1つのLEDがあります。この2個目のLEDの点滅は、プロセッサが正常に動作していることを示します。

アナログ入力保護回路

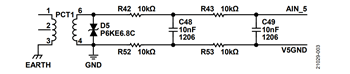

通常、AD7606Bは電流トランスの2次コイルに直接接続します。AD7606Bの入力と電流トランスの2次コイルの間にはRCローパス・フィルタが配置されており、送電系統からの高周波の干渉の低減、高周波EMC干渉の減衰、および入力に求められる過電圧保護の条件緩和を実現します。

PCBのセンサー出力には電圧トランジェント圧縮(TVS)ダイオードのP6KE6.8Cが配置されており、電流トランスからの過電圧をクランプします(図3参照)。EMC試験中はTVSをPCBから外します。それでもAD7606BはEMCの衝撃に耐えることができます。これは、RCローパス・フィルタのおかげで、電流トランスの2次コイルからの衝撃に対して内部の過電圧保護が十分に強力であることを示しています。

抵抗分圧ネットワークは、入力電圧を100VからAD7606Bの入力範囲まで減衰させます。抵抗R49(図5参照)は、2.2nFのコンデンサC47と共に信号のアンチエイリアシング用のローパス・フィルタを構成します。このローパス・フィルタはEMC信号の減衰器として機能します。また、過電圧が発生した場合、抵抗分圧ネットワークは入力電流を制限し、AD7606Bの入力を保護します。

更に、電圧チャンネルの入力にはそれぞれバリスタが1個内蔵されており、電圧サージによる衝撃を吸収します。バリスタは、抵抗分圧ネットワークのトポロジを採用した場合の標準的な電圧チャンネルのEMC保護部品です。

回路レイアウト時の考慮事項

堅牢なEMC性能のPCBを設計するには、以下を考慮することが重要です。

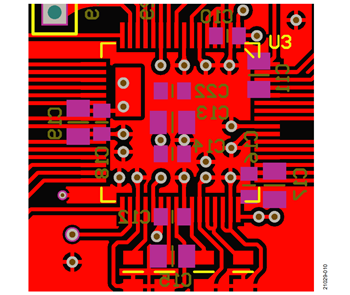

全体を考慮した配置

基板全体を考慮して部品を配置するには、信号の流れに従う必要があります。すべてのセンサー入力ポート(電圧入力チャンネルと電流入力チャンネル)は、EMCテスト・ボード上の上側と右側に配置します。センサーの出力信号は、PCBの中央に配置したAD7606Bの入力に接続します。プロセッサは、PCBの左側からAD7606Bのデジタル入出力側に接続します。これにより、全体的な信号の流れは、PCBの上側と右側(センサー入力)から中央のAD7606Bへ、そして左側のプロセッサへと向かいます。この基板全体を考慮した配置によって、アナログの高電圧回路とデジタルの低電圧回路を分割することができます。アナログ高電圧エリア(センサー入力)からの導電性のEMC干渉を、低電圧のデジタル・エリアに流入する前にブロックするかバイパスすることができれば、PCBはEMCに関して安全です。分割と全体的な信号の流れを明確にすることが導電性の干渉をPCB上で制御するための前提条件です。

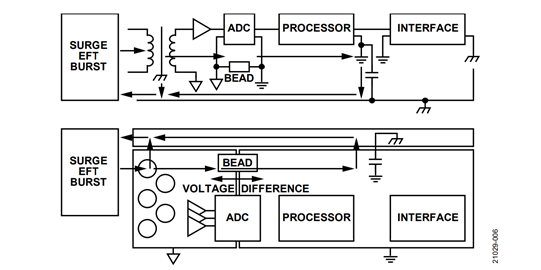

スプリット・グラウンドは使用しない

アナログ・グラウンドとデジタル・グラウンドの分離はAD7606BのS/N比性能を向上させますが、EMCサージによるリスクが非常に高くなります。特に、フェライト・ビーズを使用してアナログ・グラウンドとデジタル・グラウンドを1つの接続ポイントで接続すると危険です。図6に、スプリット・グラウンドが原因で生じるEMCの問題について示します。

ほとんどのEMC干渉信号は、EFT/バーストなどのコモンモード信号です。コモンモードのEMC試験では、EMC信号発生器が高速・高電圧の干渉信号を生成します。発生器は、テスト対象デバイス(DUT)の入力ポートとグラウンドの間に干渉信号を印加します。

コモンモード電流は、DUTのアナログ部分を流れ、デカップリング・コンデンサを介してPCBのアナログ・グラウンドに流入します。このとき、コモンモード電流は最小のインピーダンスでアース・グラウンドに達する経路を探してEMCの信号発生器まで流れようとします。

DUTのアース・グラウンドがシステムのデジタル側の近くにあることも多く、この場合、コモンモード電流は必ずシステムのアナログ側からデジタル側を経由してグラウンドまで流れることになります。スプリット・グラウンドが使用されていると、コモンモード電流は必ずシングル接続ポイントを通じてアナログ・グラウンドとデジタル・グラウンドの間を流れます。これにより、電流が非常に大きい場合は2つのグランド・プレーンの間に大きな電位差が発生し、AD7606Bが誤動作することがあります。したがって、フェライト・ビーズをアナログ・グラウンドとデジタル・グラウンドの接続に使用することは、非常に重大な問題となる可能性があります。

デカップリング・コンデンサ

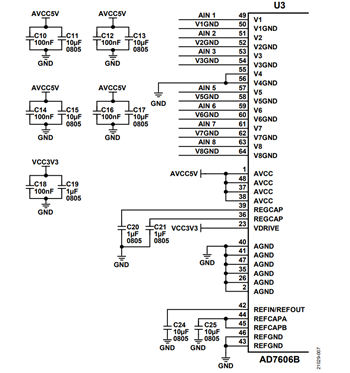

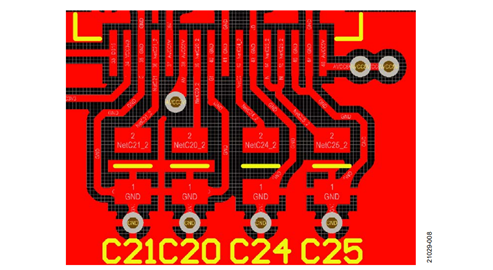

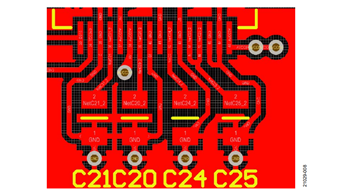

デカップリング・コンデンサは、AD7606Bの電源ピンの近くに配置します。デカップリング・コンデンサの概要を図7に示します。

AD7606Bの内部電圧レギュレータ用の1μFデカップリング・コンデンサはC20とC21です。電圧リファレンスおよびリファレンス・バッファ用の10μFデカップリング・コンデンサはC24とC25です。この4個のコンデンサは、PCB上面で以下のピンの近くに配置してください。

- コンデンサC21はピン35とピン36に接続し、パターンをできるだけ短くします。

- コンデンサC20はピン39とピン40に接続し、パターンをできるだけ短くします。

- コンデンサC24はピン42とピン43に接続し、パターンをできるだけ短くします。

- ピン44とピン45を接続します。ピン46とピン47を接続し、このパターンをコンデンサC25に接続します。パターンはできるだけ短くします。

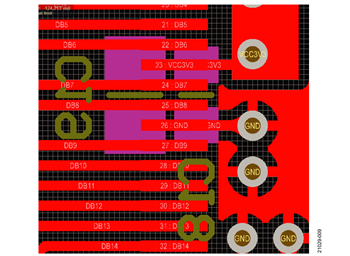

C18とC19は、3.3Vデジタル電源用のデカップリング・コンデンサです。これらのコンデンサに対応するAD7606Bのピンはピン23とピン26です(図9参照)。2つのビアをピン23とピン26の近くに配置し、デカップリング・コンデンサをPCB下面側のビアの近くに配置します。

AD7606Bには、4個の5Vアナログ電源入力ピン(ピン1、ピン37、ピン38、ピン48)が設けられています。これらのピンにおけるデカップリング・コンデンサの配置を図10に示します。デカップリング・コンデンサは、PCB下面側のビアの近くに配置します(図10のピンク色のフットプリント)。ビアと電源ピンの間のパターンはできるだけ短くしてください。

EMC試験

以下に説明するEMC試験では、PCBの電源はバッテリで供給します。

ESD試験

±8kVの接触放電と±15kVの気中放電による干渉を以下のポートに印加します。

- すべての電圧チャンネル入力ポート

- すべての電流チャンネル入力ポート

- 垂直結合板

- 水平結合板

これらの干渉信号を接続しても、ADCの故障を示すLEDは点灯しません。したがって、AD7606Bはシステム・レベルのESD試験に合格することができます。

EFT/バースト試験

±4kV、100kHzの干渉信号と±4kV、5kHzの干渉信号を以下のポートに印加します。

- すべての電圧チャンネル入力ポート

- すべての電流チャンネル入力ポート

これらの干渉信号を接続しても、ADCの故障を示すLEDは点灯しません。したがって、AD7606Bはシステム・レベルのEFT/バースト試験に合格することができます。

サージ試験

AD7606BベースのEMCテスト・ボードには、A相、B相、C相、そして中性入力のN相から成る4個の電圧入力チャンネルが搭載されています。

コモンモードのサージ試験では、±4kVのコモンモード電圧を任意の電圧入力とアース・グラウンド(PE)の間に印加します。以下の組み合わせで接続します。

- A相とPE

- B相とPE

- C相とPE

- A相、B相、およびC相とPE

差動モードのサージ試験では、±2kVの差動モード電圧を各電圧入力チャンネル間に印加します。以下の接続で実施します。

- A相とB相

- A相とC相

- A相とN相

- B相とC相

- B相とN相

- C相とN相

それぞれの相に±4kVのコモンモード電圧と±2kVの差動モード電圧が印加されている間、ADCの故障を示すLEDは点灯しません。したがって、適切に設計することにより、AD7606Bはシステム・レベルのサージ試験に合格することができます。