最大SNRとクロック・ジッタの関係

高速ADC用のクロック回路を設計する場合、最も重要なパラメータの1つがジッタです。クロック・ジッタの量によって、所定の入力周波数に対して実現可能な最大SNRが決まります。最新の高速ADCのジッタは約80fsで、ADCのエンコード・クロックは、おおむねこのあたりに収まっている必要があります。ADCの最大性能を実現するには、1ps未満でなければならないことは確かです。

SNRとジッタの関係は、次式で表すことができます。

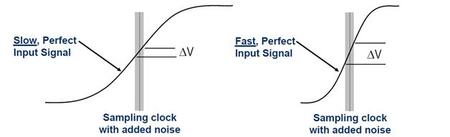

ここでfinは入力信号周波数、tjはクロック・ジッタです。この式から、入力信号周波数が高くジッタ量が一定の場合、最大SNRが低下することがわかります。これは、スルーイング信号が高速になるにつれ、所定のジッタ量に対する電圧誤差が大きくなるためです。

入力信号周波数が比較的低い場合(例えば1MHz)、クロック・ジッタはそれほど問題になりません。しかし、入力信号周波数が数百MHzになると、クロック・ジッタが主な原因で誤差が生じ、SNRを制限する要因となります。

以下の図は、入力周波数とクロック・ジッタがSNRの低下にどのように影響するかを示したものです。

X軸上の使用する入力周波数とY軸上の必要なSNRから、所望のSNRを実現するためにクロック・ジッタを具体的にどの程度に抑えるべきかがわかります。クロック・ジッタをADCジッタと組み合わせるには、2つの項を冪の形で合算する必要があります。

例えば、入力信号が100MHzで必要なSNRが78dBの場合、クロック源のジッタは200fs未満でなければなりません。標準的なFPGAを用いると最大50psのジッタが加わるため、ADCクロックとしては使用できません。通常、ADCのクロック源として最適なのは、VCXOや低ジッタPLLです。

なお、上記の式は標準的なサンプリング理論から導かれたもので、どのメーカーのADCにも適用できます。

高速ADCを使用したシステムを設計する場合、クロック・ジッタを考慮することが重要です。クロック・ジッタによって、システムで実現できるSNRが大幅に制限され、システム設計において致命的な問題となることも考えられます。クロック・ジッタをできる限り小さい値に維持することは、フロント・エンド回路の設計に劣らず非常に重要です。後回しにせず、設計の最初の段階からしっかりと検討してください。

著者について

LTC2246Hのデモ・ボードであるDC1151を始め、リニアテクノロジーのほぼ全ての高速ADCデモ・ボードの設計に携わってきました。これらのボードは、評価用ボードとして様々なアプリケーションで用いられています。Clarenceの設計したデモ・ボードは、アンプとADCを合わせたフル・シグナル・チェーンを有...