LTspice:SAR ADCのアナログ入力をシミュレーション

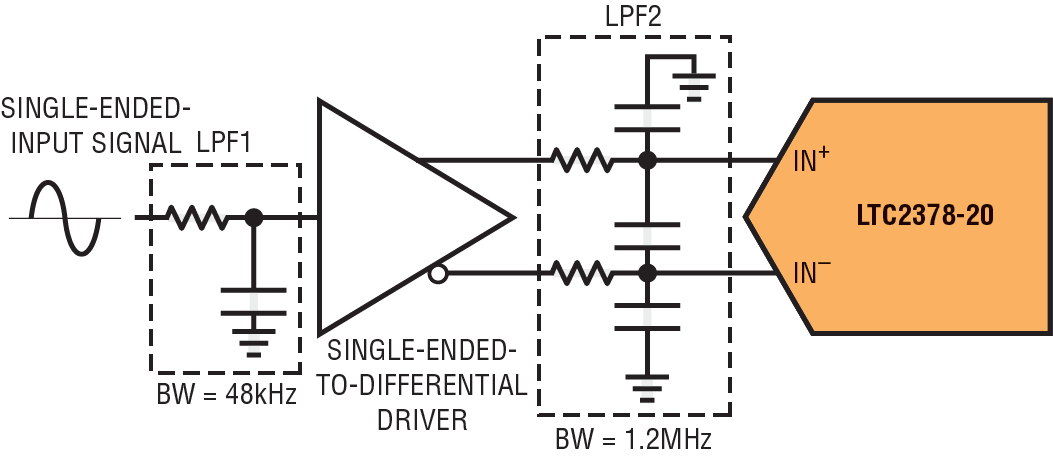

ADCの分解能やサンプル・レートが向上を続けるのに伴い、ADC自体ではなくアナログ入力の駆動回路が、回路全体の精度を決める制限要因になりつつあります。ノイズの多い入力信号用に設けられた単純な単極RCローパス・フィルタ(LPF1)(図1)の他、多くの場合、結合RCフィルタ・ネットワーク(LPF2)がバッファとADCの間に使用され、ADCのサンプリング・トランジェントからバッファに反射される擾乱を最小限に抑えます。アナログ入力のRC時定数が長いと、これらの擾乱のセトリングは遅くなります。そのため、通常、LPF2にはLPF1よりも広い帯域幅が求められます。このフィルタは、バッファからのノイズの影響を最小限に抑える効果もあります。

図1.アンプとADCの間のインターフェースをシミュレーションすることで、ノイズとセトリング時間の間のトレードオフが確定しやすくなります。

アンプとADCの間のインターフェースをシミュレーションすることで、セトリング時間とノイズ性能の間の興味深いトレードオフが示されます。そのようなシミュレーションと共に実験を行うことで、フィルタ設計がこれらの性能の側面にどのように影響するかを、直感的に理解できるようになります。

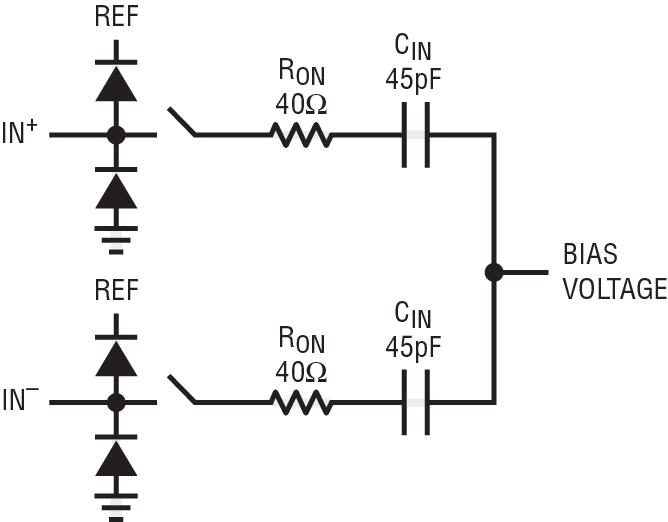

完全差動SAR ADCのアナログ入力は、図2の等価回路に示す駆動回路のスイッチド・キャパシタ負荷としてモデル化できます。ここに示した値は、20ビット1Mspsの低消費電力SAR ADCであるLTC2378-20によるものですが、他のADCを表すように変更することは容易です。アクイジション・フェーズ時は、各入力には、サンプリング・スイッチのオン抵抗から生じる40Ω(RON)と直列に、サンプリングCDACに由来する約45pF(CIN)が生じます。このフェーズでは、CINコンデンサを充電する間、入力は電流スパイクを引き出します。その後の変換フェーズでは、アナログ入力が引き出すのはわずかなリーク電流のみで、コンデンサは完全に放電されます。ADCアナログ入力のこのモデル化は、アンプをLTC2378-20などのSAR ADCと組み合わせる際の極めて大きな課題の1つである、各アクイジション・フェーズの開始時にADC入力によって引き出される電流スパイクを処理する、という課題を強調するものです。

図2.SAR ADCのアナログ入力等価回路

この等価回路のシミュレーション回路図を図3に示します。低消費電力のLTC6362差動オペアンプが、シングルエンド入力信号を完全差動出力に変換してLTC2378-20を駆動するよう構成されています。シミュレーションを簡素化するために、入力ESD保護ダイオードは含まれていません。2個の45pF入力コンデンサ(C1およびC2)は、オン抵抗が40ΩのSWモデル・ステートメントで定義される電圧制御スイッチ(S1およびS2)を介して充電されます。これらのスイッチは、1Msps時のLTC2378-20 SAR ADCのアクイジション時間をシミュレーションするため、パルス幅が312nsで周期が1µsのパルス電圧源で駆動されます。次のアクイジション・フェーズのサンプリング・コンデンサを用意するため、理想的な動作のインバータ(A1)を使用して、コンデンサを放電する2つめのセットのスイッチ(S3およびS4)をオンにします。

図3.SAR ADCアナログ入力等価回路のシミュレーション回路図

アンプとADCの間のRCフィルタ・ネットワークの機能には、いくつかの目的があります。まず、フィルタ・ネットワークはADCに入り込む広帯域ノイズの量を減少させます。次に、コンデンサには、ADCの内部サンプリング・コンデンサからの電荷のキックバックを吸収する電荷リザーバとしての役割を果たします。各変換サイクルの後、放電されたサンプル・コンデンサ(45pF)は、アンプ回路に再接続されます。これよりはるかに大きなリザーバ・コンデンサをADC入力に配置すると、これらのサンプル・コンデンサによる電圧変動が減少します。ただし、広帯域ノイズとセトリング時間性能の間にはトレードオフがあります。サンプル・コンデンサはアンプ回路に接続されている間(アクイジション時間)、RCネットワークは、ADCの分解能の範囲内で完全にセトリングする必要があります。フィルタ・ネットワークのリザーバ・コンデンサが大きすぎる場合、このセトリング時間が許容可能な限度を超えて増加してしまいます。このトレードオフの詳細については、Kris Lokereの「SAR ADC Driver Interface」を参照してください。