概要

設計リソース

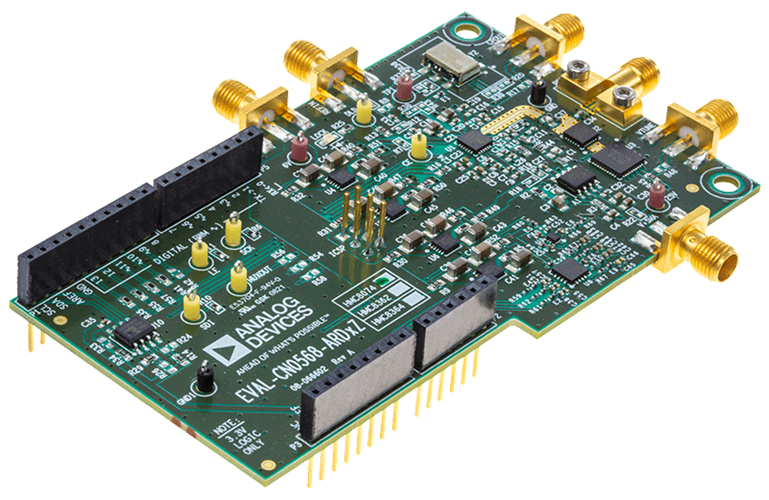

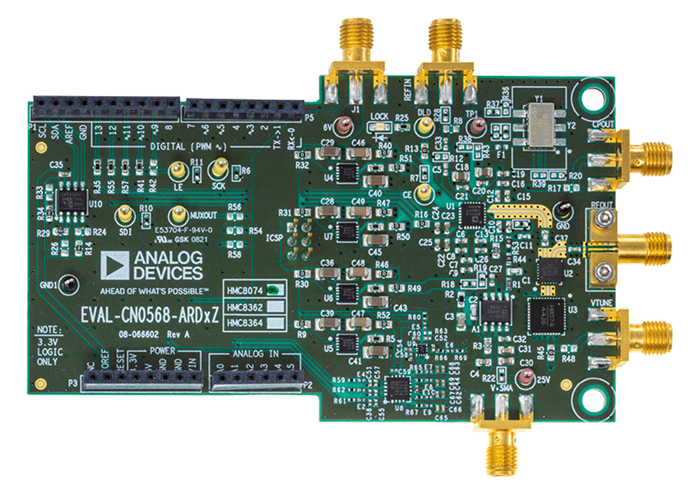

評価用ボード

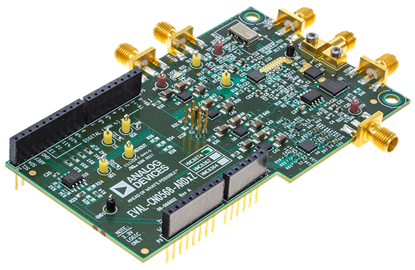

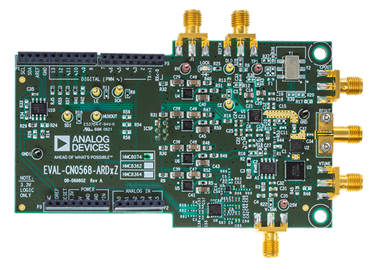

型番に"Z"が付いているものは、RoHS対応製品です。 本回路の評価には以下の評価用ボードが必要です。

- EVAL-CN0568-ARD1Z ($492.20) 8.3GHz to 15.1GHz PLL and Quadband VCO

- EVAL-CN0568-ARD2Z ($492.20) 11.9GHz to 18.3GHz PLL and Quadband VCO

- EVAL-CN0568-ARD3Z ($553.73) 18.1GHz to 24GHz PLL and Quadband VCO

- EVAL-SDP-CK1Z ($184.00) System Demonstration Platform

機能と利点

- 動作周波数:8GHz~26GHz

- クワッドバンドVCOにより広帯域で低位相ノイズを実現

- 使いやすいオンボード・リファレンス・クロック

- Arduinoフォーム・ファクタ互換

参考資料

-

CN0568 User Guide2021/11/11WIKI

-

CN0568: 高速スイッチング、高性能 PLL およびクワッドバンド VCO 周波数シンセサイザ2021/11/11PDF515 K

回路機能とその特長

フェーズ・ロック・ループ(PLL)周波数生成回路は、基本的な FM ブロードキャスト・バンド・レシーバー、デジタル・コミュニケーション、航空宇宙、計測器、レーダー、電子線など、多数の産業やアプリケーションで広く用いられています。PLLは、1MHz 未満の周波数から数 GHz を超える周波数までの無線周波数(RF)や中間周波数(IF)を生成するために用いられています。アプリケーション条件の変化の幅が非常に大きいため、PLL の設計と最適化には、消費電力、位相ノイズ、周波数調整範囲、周波数分解能、ロック時間などのパラメータのトレードオフが必要です。

好ましくない性能低下を招くことが多いことを考慮しておく必要がある重要な設計トレードオフの 1 つが、周波数範囲と位相ノイズ性能のトレードオフです。広帯域の電圧制御発振器(VCO)は、広い範囲の周波数を提供しますが、位相ノイズ性能は最善ではありません。反対に、狭帯域 VCOでは位相ノイズ性能は向上しますが、調整可能な周波数範囲が犠牲になります。複数の狭帯域 VCO をマルチプレクスして調整可能周波数範囲を広げることは可能ですが、多くの場合、実用的ではありません。各 VCO への電源を切り替えて適切な RF 出力を選択するには複雑な外部回路が必要となるためです。

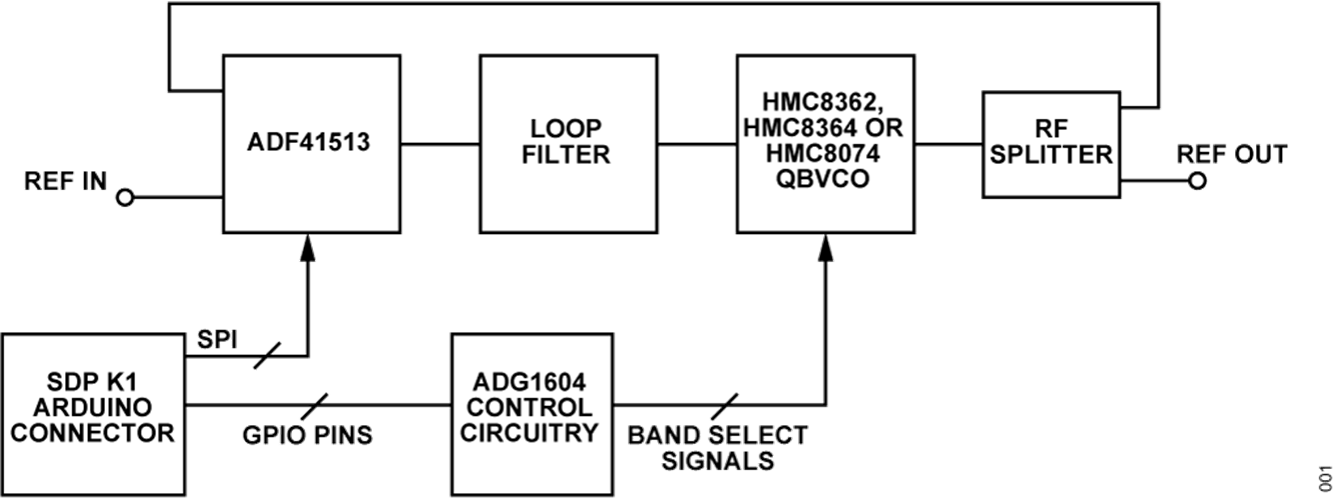

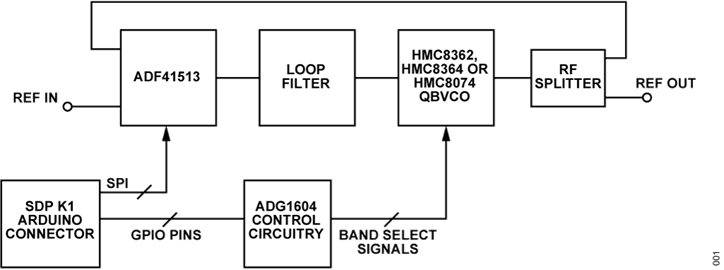

図 1 に示す回路は、4 つの狭帯域 VCO を 1 つのパッケージに収めた、集積化クワッドバンド VCOを示したものです。この設計の利点は、狭帯域 VCO の優れた位相ノイズ性能の利点を維持しながら、同時に広い動作周波数範囲を提供できる点です。VCOの帯域はオンボードのマルチプレクサ回路で切り替えられます。この回路は、ホストから設定された周波数に基づいて 4 つのVCO の 1 つを選択するものです。

このスイッチング回路は、VCO の帯域を超高速に切り替えられるよう最適化されており、最低周波数帯域から最高周波数帯域までの全体的なロック時間を減少します。これは、高速周波数ホッピングなどの、広い範囲の周波数にわたって高速のスイッチング時間が必要となるアプリケーションで利点となります。

PLL に備わっている位相再同期機能と位相調整機能は、高精度の位相再現性を必要とするビームフォーミングのようなアプリケーションで有用です。回路は Arduino フォーム・ファクタのプラットフォーム・ボードと互換性があり、また、複数のボードを積み重ねて同じデジタル・インターフェースを共有することができます。

回路説明

PLL シンセサイザ

この回路の PLL シンセサイザには、ADF41513 が選択されています。このデバイスは動作周波数範囲が 1GHZ~26.5GHzと極めて広く、3 つのバリエーションのクワッドバンド VCO の周波数範囲をすべてカバーしているためです。フラクショナル・モードの場合は、∑-Δ 変調器によってテラヘルツ未満の周波数分解を実現します。また、ADF41513 のノイズ・フロアは、インテジャー・モードで-235dBc/Hz、フラクショナル・モードで-231dBc/Hz と極めて低いため、最適な位相ノイズ性能を実現できます。

リファレンス入力

EVAL-CN0568-ARDxZ は、REFIN SMA コネクタからの外部印加リファレンス周波数用に設定することも、オンボードの100MHz 超低位相ノイズ水晶発振器用に設定することもできます。82fsという超低ジッタと-90dBC/Hzという近接位相ノイズを特長としています。デフォルトでは、オンボード水晶発振器オプションで設定されていますが、R8 を取り外し、R28 のフットプリントに 0Ωの抵抗を挿入することで、外部入力を選択できます。100MHz のリファレンスが必要な事例には、オンボード・リファレンスを使用することを推奨します。

ループ・フィルタ

使用する 3 種のクワッドバンド VCO ではチューニング電圧が1.0V~13.5V であることが必要ですが、ADF41513 PLL のチャージ・ポンプは 0V~3.3Vで動作するため、ゲインを持つアクティブ・ループ・フィルタ回路が必要となります。このループ・フィルタは、各 VCO 帯域の周波数範囲全域で最大限の安定性を持つよう設計されています。ループの帯域幅は約 100kHz、位相マージンは 50ºです。チューニング感度(周波数とチューニング電圧の関係での傾き)は選択した VCO 帯域によって異なるため、ループ・フィルタの帯域幅は動作周波数によってわずかに変動します。ループ・フィルタは 100MHz のリファレンス周波数を使用するよう設計されているため、その他のリファレンス周波数が必要な場合は再設計が必要です。ADISimPLL ツールを使用すると、ループ・フィルタの最適なトポロジを決めることができ、シミュレーションモデルを使用して、目的の帯域幅や位相マージンの実現するために必要な部品値を計算できます。

5 次のループ・フィルタ・トポロジを使用すれば、帯域外のロール・オフを増加し、また、シグマ・デルタ・モジュレータのノイズやスプリアスを減少させることができます。このループ・フィルタで選択したオペアンプは、低ノイズの性能を持ちレール toレールで動作できる ADA4625です。図 2に、使用したループ・フィルタ構成の回路図を示します。図 3 には、ボード上でのループ・フィルタのフットプリントを示します。

電圧制御発振器

HMC8074/HMC8362/HMC8364 クワッドバンド VCO は、それぞれ、1 つの LFCSP パッケージ統合された 4 つの独立した狭帯域VCO コアで構成されています。各コアの選択は、対応するコアに 5Vの電源電圧を供給することで行うことができます。所定のタイミングで給電できるのは 1 つのコアのみであるため、出力バッファ・アンプはオーバードライブされません。これらのクワッドバンド VCO は、広帯域 VCO の周波数範囲を備えていますが、同時に、各内部 VCO コアが狭帯域性能を持つため、優れた位相ノイズ性能が維持されます。各製品バリエーションに対し、VCO のチューニング曲線は 4 つの周波数帯すべてを通じて一定です。そのため、すべての帯域に対し 1 つのループ・フィルタを使用できます。これらのクワッドバンド VCO は、バッファ・アンプを含め 75mA(代表値)の低消費電流で、消費電力が問題となるアプリケーションに適しています。これら 3 種のクワッドバンド VCO を合わせると、8.3GHz~26.6GHz の周波数範囲をカバーします。各クワッドバンド VCO の個別の周波数範囲は次のとおりです。

- HMC8074:8.3GHz~15.2GHz

- HMC8362:11.9GHz~18.3GHz

- HMC8364:18.1GHz~26.6GHz

HMC8364 は、ADF41513 の最大周波数である 26.5GHz まで動作できますが、EVAL-CN0568-ARDxZ の動作範囲は 24GHz に制限されています。詳細については、周波数感度のセクションで説明します。

RF スプリッタ

超広帯域幅(1.8GHz~28GHz)の 1:2 RF スプリッタが、VCO 出力を CN0568 RF 出力ポートと PLL RF 帰還パスに分割します。このスプリッタが選択された主な理由は、動作範囲が 2GHz~26.5GHz と広帯域幅であることです。このことは、このスプリッタがクワッドバンド VCO の 3 つのバリエーションの周波数範囲全域で使用できることを意味します。EP2K1+は、4x4mm という小型フットプリントで 2.5W という高電力処理能力も有しています。

挿入損失は、スプリッタの周波数範囲全域で異なり、代表値は、2GHz で 0.8dB、26.5GHz で 2.4dB です。この挿入損失にスプリッタの 3dB の損失を加えると、特定の周波数でスプリッタによって生じる信号の損失が求まります。動作周波数の高いバリエーションである HMC8364 ボードでは、ADF41513 の RF 入力感度が周波数と共に増加するため、挿入損失がロック動作に影響する可能性があります。詳細については、周波数感度のセクションで説明します。

位相再同期

目的の周波数にロックするとき、リファレンス周波数を基準として位相オフセットが生じる場合があります。位相再同期はADF41513 の機能の 1 つであり、所定の RFOUT 周波数に対しリファレンスから一定の位相オフセットを生成するものです。これは、ビームフォーミングなどの位相が問題となるアプリケーションでは、重要な機能です。

ユーザは、最初に位相再同期をイネーブルした後、動作周波数での位相オフセットを選択します。周波数が変化し、その後元の周波数に戻る場合は、元の位相オフセットが維持されます。位相再同期をイネーブルにすると、内部タイマーが次式で与えられる tSYNCの間隔で同期信号を生成します。

CLK1 および CLK2 は ADF41513 のレジスタ・ビットフィールドで、アプリケーション・ソフトウェア内で設定されます。これらは、tSYNC が PLL の最も厳しいロック時間より大きな値となるように設定し、位相再同期が PLL のセトリング・トランジェントの最後のサイクル・スリップで確実に発生するようにします。なお、位相再同期を使用する場合、インテジャー・モードの動作の場合でもシグマ・デルタ・モジュレータをイネーブルする必要があることに注意してください。

位相調整

位相は、位相値のビットフィールドを使用してどの周波数でも手動によりインクリメントできます。ビットフィールドは CN0568 アプリケーション・ソフトウェア内でプログラムできます。位相オフセットは次の式に従って生成されます。

位相は、ADF41513 のレジスタ 0 に書込みが行われるごとに、位相オフセット分だけインクリメントできます。位相再同期モードの場合のように、位相調整を行うには、インテジャー・モードで動作する場合でもシグマ・デルタ・モジュレータをイネーブルする必要があります。

周波数感度

ADF41513 の最大入力周波数は 26.5GHz で、HMC8364 クワッドバンド VCO のバリエーションはこれより少し高い 26.6GHzです。ただし、周波数が 24GHz に近くなると、このセクションで説明するように、性能に影響しループがロックできなくなる結果をもたらしかねない要因がいくつか生じます。そのため、回路の仕様は 24GHz の最大動作周波数にとどまっています。24GHz は、室温での動作での仕様です。しかし、温度が上昇すると最大動作周波数は減少する可能性があります。

ロック動作に影響する第一の要因は、HMC8364 VCO の出力電力がバンド 4 の周波数増加に伴って減少することです。これを図 6 のグラフで示します。

このように出力電力が減少することは、回路の全電力損失に大きく影響します。23.9GHz~26.6GHz では、最大 6dB の出力電力削減が実現できます。

RF 電力スプリッタの挿入損失も周波数と共に増加します。そのため、動作周波数が高い場合は、更に 1dB の損失が加わり、帰還ループの全体的な損失に影響します。

また、ADF41513 の RFIN の周波数感度も動作周波数と共に増加します。動作周波数が 24GHz を超える場合、この感度が動作にとって重要なものとなります。その他の上述の損失の影響により必要な出力電力を満たすことがより困難になるためです。周波数範囲が狭く周波数が高い場合に挿入損失が小さくなるよう、RF 帰還パターンを再設計できます。ただし、この回路の目的の1 つは、3 種のクワッドバンド VCO すべてについて最も広い周波数範囲にわたり性能を実証することです。帰還信号の電力を増加するためのもう 1 つの方法は、帰還にアンプを追加することです。これについては、バリエーション回路のセクションで説明します。

制御回路

アプリケーション・ソフトウェアで選択した周波数に基づいて様々な VCO 帯域を選択するには、制御回路を使用します。目的の周波数に基づいて、GPIO 信号を SDP-K1 Arduino コネクタからルーティングし帯域を選択します。これらのGPIO制御ロジック信号には、CN0568 製品ページで提供されているカスタム・ファームウェアが書き込まれています。カスタム・ファームウェアのロードについての詳細は、回路の評価とテストのセクションを参照してください。

電圧制御発振器の帯域選択回路における主要コンポーネントの1 つが、ADG1604 4:1 マルチプレクサです。これは、LT3045 レギュレータからマルチプレクサの 4 個のスイッチのいずれかを通じて、対応する VCO 帯域の電源に+5V の電圧を供給するものです。マルチプレクサを制御回路で使用することにより、一度に 1 つの VCOコアのみに給電でき、VCOへの損傷を回避することができます。すべての制御信号には、フィルタリング用のインダクタとコンデンサがあり、ノイズや干渉が発生する可能性を低減できます。図 7 に制御回路の一例の簡略化した回路図を示します(制御回路を含むボードの完全な回路図は、CN0568 Design Support Package にあります)。

VCO 内蔵出力バッファは、別の SDP-K1 GPIO信号で制御される単極双投(SPDT)スイッチを通じてパワーアップおよびパワーダウンが行われます。デフォルトでは、この信号は、アプリケーション・ソフトウェアによって接続が確立された後に、ハイを維持します。

周波数更新シーケンス

ADF41513 の周波数制御レジスタは、ダブル・バッファ化されています。つまり、RF 出力周波数を変更するには、2 つのイベントが生じる必要があります。まず、周波数制御ワード・レジスタを新しい目標周波数に応じて更新する必要があります。次に、周波数変更を開始するために、レジスタ 0 に書込みを行います。アプリケーション・ソフトウェアのフロント・パネルで周波数が更新されるたびに、レジスタ0の書込みを含め合計4個のレジスタに書込みが行われます。これらのレジスタへの書込みは、レジスタ 6、レジスタ 3、レジスタ 1、レジスタ 0 の順で行います。

現在の周波数に異なる VCO 帯域を使用するよう周波数が更新される場合は、図 8 に示すように、レジスタ書込み後に GPIO制御信号が更新されます。

レジスタ 0 が更新されてから約 600ns 後に GPIO が更新されます。遷移時間は、GPIO のアドレス・ビットが変更されてから、対応する出力スイッチがマルチプレクスされるまでの遅延時間です。ADG1604 4:1 マルチプレクサの遷移時間は通常 150ns です。

電源レギュレーション

EVAL-CN0568-ARDxZ は、オンボード SMA コネクタに印加される 2 つの外部電源によって給電します。印加電圧は V+SMA に+25V、J1 に 6V です。ADF41513 の電源は、EV-ADF41513SDxZ評価用ボードのデフォルトの電源グループ分けに従ってグループ分けされています。更に多くの電源ピンを組み合わせてレギュレータの数を減らすと、出力周波数スペクトルに不要なスプリアスが生じる可能性があります。

+6V の電源を J1 に適用することで、4 つのオンボード LT3045 LDO レギュレータに入力電圧を供給できます。LT3045 レギュレータが選択されたのは、超低ノイズ性能を備え、500mA の電流出力能力があるためです。

これらのレギュレータが、ADF41513のすべての+3.3V 電源とクワッドバンド VCO の+5V 電源、および水晶発振器リファレンスに電力を供給します。各レギュレータの出力電圧設定は、SET ピンの RSET 抵抗を適宜設定することで行います。詳細については LT3045 のデータシートを参照してください。

+25V の電源は、V+SMA を通じて外部電源からアクティブ・ループ・フィルタ電源に直接適用されます。複数のデカップリング・コンデンサが電源パスに配置され、外部ノイズによって電源の品質が低下するのを防止します。

バリエーション回路

HMC8364 クワッドバンド VCO バリエーションの 24GHz を超える周波数での出力電力の低下を補償するため、RFOUT 信号の後段にアンプを追加できます。この増幅された信号は、その後ADF41513 の RFIN ポートへの帰還信号として使用され、動作範囲を最大周波数 26.5GHz に拡張します。図 9 に、HMC962 LNAとRFOUTポートを接続して位相ノイズの結果を集めたものを示します。比較のため、LNA のないデフォルト構成でのデータを重ねてあります。

図 9 に示すように、HMC962 を出力に置いた場合でも位相ノイズの悪化が生じません。24GHz では、アンプのゲインは約12.5dB です。この場合、アンプ入力の電力レベルは、−7.4dBmでした。出力には 5.23dBm の電力レベルが測定されました。これは、24GHz での ADF41513 の最大感度レベルと最小感度レベルの間にあるため、最適な電力レベルです。ADF41513 の感度レベルの詳細については、データシートを参照してください。

回路の評価とテスト

EVAL-CN0568-ARDxZ ボードは、CN0568 専用ファームウェアを実行する SDP-K1 コントローラ・ボードを介して、ホストとインターフェース接続します。3.3V ロジックを使用するその他のArduino 互換インターフェース・ボードも使用できますが、ファームウェアの開発が必要となります。デモ・ソフトウェアのインストール時に供給されたカスタム・ファームウェア・ファイルは、SDP-K1 コントローラ・ボードの最初の接続後に読み込まれます。これは、ソフトウェア・パッケージに含まれているhexファイルを SDP-K1 の駆動場所にコピーすることで行われます。

必要な装置

- EVAL-CN0568-ARDxZ 評価用ボード

- EVAL-SDP-CK1Z コントローラ・ボード

- Windows 7 以降を実行する PC またはラップトップ

- 適切な周波数測定レンジを持つスペクトラム・アナライザまたは位相ノイズ・アナライザ

- バナナプラグ-SMA 電源ケーブル 2 本

- 2.92mm コネクタ付き 50Ω RF/マイクロ波ケーブル 1 本

- +25V および+6V の電圧出力機能を持つデュアル電源

手順

このセクションでは、EVAL-CN0568-ARDxZ の任意のバリエーションをセットアップしてRFOUTポートに一定の周波数を出力するための、一般的な手順を説明します。手順の詳細については、EVAL- CN0568-ARDxZ ユーザ・ガイドを参照してください。

- 電源がオフであることを確認します。図 10 に示すように評価用ボードをセットアップします。

- EVAL-CN0568-ARDxZ を SDP-K1 コントローラ・ボードに組み込みます。

- USB ケーブルを介してホストの PC/ラップトップをSDP-K1 インターフェースに接続します。

- +6V(電流制限値 = 200mA)を J1、+25V(電流制限値 = 20mA)を V+SMA に接続します。

- 50Ω の RF ケーブルをスペクトラム・アナライザまたは位相ノイズ・アナライザに接続します。

- 電源を両方ともオンにします。

- CN0568 ソフトウェアを開き、該当のバリエーションを選択します。[Connect]ボタンを押し、デバイスの初期化を行います。

- 周波数を動作範囲内で選択し、[Update Frequency]を選択します。

- 選択した周波数がスペクトラム・アナライザに現れます。

結果

HMC8362 の 4 つの帯域の中心周波数を用いて位相ノイズの結果のグラフが収集されます。図 11 にこの位相ノイズのグラフを重ね合わせて示します。

結果のデータ収集は、室温動作でループ帯域幅が 100kHz のデフォルトのオンボード・ループ・フィルタ設定で行いました。EVAL-CN0568-ARD2Zで、回路の測定されたロック時間も、表1に示します。

| Band Start/Stop | Start Freq. (GHz) | Stop Freq. (GHz) | Lock time (μs) |

| Band 1 - Band 2 | 13 | 14.5 | 53.1 |

| Band 1 - Band 3 | 13 | 16.5 | 28.5 |

| Band 1 - Band 4 | 13 | 18 | 49 |

| Band 2 - Band 1 | 14.5 | 13 | 55 |

| Band 2 - Band 3 | 14.5 | 16.5 | 56.7 |

| Band 2 - Band 4 | 14.5 | 18 | 36.5 |

| Band 3 - Band 1 | 16.5 | 13 | 35.8 |

| Band 3 - Band 2 | 16.5 | 14.5 | 54 |

| Band 3 - Band 4 | 16.5 | 18 | 57.1 |

| Band 4 - Band 1 | 18 | 13 | 47 |

| Band 4 - Band 2 | 18 | 14.5 | 32 |

| Band 4 - Band 3 | 18 | 16.5 | 50.2 |

これらの測定されたロック時間について、周波数がストップ周波数の+/- 10kHz に達し、この閾値からその後は外れることがなくなることをロックの基準としました。ADISimPLL を使用し、シミュレーションされたロック時間がこれらの測定結果に近いものであることが確認されています。