概要

設計リソース

設計/統合ファイル

- Schematic

- Bill of Materials

- Gerber Files

- Allegro Layout Files

- Assembly Drawing

評価用ボード

型番に"Z"が付いているものは、RoHS対応製品です。 本回路の評価には以下の評価用ボードが必要です。

- EVAL-CN0506-FMCZ ($203.03) Dual Ethernet PHY Board

デバイス・ドライバ

コンポーネントのデジタル・インターフェースとを介して通信するために使用されるCコードやFPGAコードなどのソフトウェアです。

FPGA/HDL

機能と利点

- RGMII、RMII、およびMIIモードをサポート

- デュアル・ポートにより、リング型またはライン型のトポロジが可能

- 1000Mbspsで154mのケーブルを駆動可能

マーケット & テクノロジー

使用されている製品

参考資料

-

CN0506 User Guide2020/10/05WIKI

-

ラピッド・プロトタイピングを実現するためのソリューション2024/04/15PDF4 M

-

CN0506: 10Mbps/100Mbps/1000Mbps のデュアル・チャンネル、低消費電力産業用イーサネット PHY (Rev. 0)2020/10/05PDF330 K

回路機能とその特長

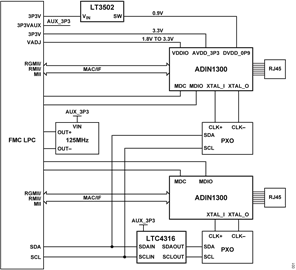

図 1 に示す回路は、デュアル・チャンネル、低遅延、低消費電力のイーサネット物理層(PHY)カードで、ライン型およびリング型ネットワーク・トポロジを使用する産業用イーサネット・アプリケーションにおいて、10Mbps、100Mbps、および1000Mbps の速度をサポートします。

デュアル・チャンネルを用いることにより、一般に産業用のセンシング、制御、および分散制御システムに使用されているライン型およびリング型ネットワーク・トポロジを構成できます。ADIN1300 イーサネット PHY には、電磁両立性(EMC)と静電放電(ESD)の耐性に対する幅広いテストが実施されており、また、公表されている共通の最高速度でリモート PHY デバイスとリンク接続ができるように、自動ネゴシエーション機能がサポートされています。PHYでのIEEE1588タイム・スタンプにより、リアルタイム・アプリケーションでタイミングの不確定性が低減され、冗長なアプリケーションおよびリアルタイム・アプリケーションでリンク喪失検出機能が強化されます。

この回路は、個々に独立した 2 つの 10Mbps、100Mbps、および1000Mbps の PHY で構成され、各 PHY には省電力型イーサネット(EEE)PHY コア、および関連する共通のアナログ回路、入出力クロック・バッファ、管理インターフェース、サブシステム・レジスタ、メディア・アクセス制御(MAC)インターフェース、コントロール・ロジックのすべてが搭載されています。

この設計は、ホストのフィールド・プログラマブル・ゲート・アレイ(FPGA)メザニン・カード(FMC)開発ボードから給電されるため、外部電源は不要です。クロックをソフトウェアでプログラム可能であるため、媒体独立インターフェース(MII)、Reduced MII(RMII)、および Reduced Gigabit MII(RGMII)の MACインターフェース・モードが可能です。磁気回路を内蔵した RJ45 ポートの使用により、ソリューションを可能な限り小型化しています。

このソリューションでは、ギガビットの速度で最長 150 メートルのケーブル長、100Mbps または 10Mbps の速度で最長 180 メートルのケーブル長をサポートします。このソリューションは、一般にリング型またはバス型トポロジで使用されます。ADIN1300の自動ネゴシエーション機能により、サポートされる最高速度で他の PHY デバイスと接続できます。

回路説明

イーサネット

イーサネットは、ローカル・エリア・ネットワーク(LAN)におけるデータ・ネットワーキング・アプリケーションを対象とした最も一般的なタイプのパケットベースの物理接続で、米国電気電子学会(IEEE)802.3 規格によるサブセクションおよび仕様として規定されています。

イーサネットには、様々な速度と伝送媒体があります。ただし、この回路ノートでは、カテゴリ 5e(CAT5e)またはカテゴリ 6(CAT6)のストレート・スルーまたはクロスオーバーのツイスト・ペア・ケーブルを使用した 10BASE-T、100BASE-TX、および 1000BASE-T に焦点を合わせます。

ライン型およびリング型ネットワーク・トポロジ

一般的な産業用イーサネット・ネットワークは、ライン型またはリング型トポロジで構成されます。ライン型およびリング型ネットワーク・トポロジでは、スター型ネットワークと比べて配線長が短縮され、また、リング型ネットワークには冗長経路が存在します(図 2 を参照)。ライン型またはリング型ネットワークに接続する各デバイスには、ネットワークを通してイーサネット・フレームを転送するためのイーサネット・ポートが 2 つ必要です。

PHY

PHY は、開放型システム間相互接続(OSI)モデルの物理層機能を実現する物理インターフェース・トランシーバーです。PHY はデバイス間での送信データをエンコードし、受信データをデコードして、フレームとパケットの完全性を維持します(図 3 を参照)。

図 3. PHY デバイスを使用した代表的なネットワーク・センサー

PHY ハードウェア設定 — ストラップ抵抗

ADIN1300では、パワー・アップの準備をし、リンクを確立するための設定をすることができます。この PHY ハードウェア設定では、非マネージド・アプリケーションでのパワー・オン時に、外付けされたストラップ抵抗を使用して既知の設定をすることができます。非マネージド・アプリケーションでは、一般に管理データ入出力(MDIO)を通じた PHY の設定は行われません。その代わりに、PHY ハードウェア設定を利用し、適切な設定準備をしてから ADIN1300 を起動させ、リモートの PHY パートナとリンク接続します。ADIN1300がパワー・アップし、このデバイスのリセットが解除されたとき、ハードウェア・ストラップ・ピンがサンプリングされます。これによって、この PHY デバイスは様々な機能をどのように設定するかを認識します。

この回路ノートにおいて対象となるハードウェア設定モードは、速度、PHY アドレス、自動媒体依存インターフェース・クロスオーバー(Auto-MDIX)、および MACインターフェースです。EVAL-CN0506-FMCZには抵抗フットプリントがあり、特定のデフォルト設定が施されていますが、様々な組み合わせを行うことができます。デフォルトのハードウェア設定を変更する必要のある場合は、抵抗部品を挿入または除去することができます。

省電力型イーサネット(EEE)、エネルギー検出パワー・ダウン、ダウン・スピード、ソフトウェア・パワー・ダウンといった、その他の機能を使用する場合の詳細については、ADIN1300データシートを参照してください。

物理層 — MAC インターフェース

CN-0506 上の MAC インターフェースはワイヤ媒体で、RGMII、RMII、または MII の 3 つの MAC インターフェース・オプションがあります。RGMII は最大 1000Mbps までのすべての速度をサポートし、MII と RMII はどちらも 10Mbps と 100Mbps の速度をサポートします。CN-0506 上では RGMII がデフォルトのインターフェースになっています。

どのMACインターフェースを使用するかを選択する方法として、ストラップ抵抗を外付けするというハードウェアによる方法と、ソフトウェアでレジスタを設定する方法の 2 つがあります。MACIF_SEL0 と MACIF_SEL1 は、ADIN1300 内の多機能ピンです(詳細については、ADIN1300 のデータシートを参照)。CN0506の場合、表1 に従ってMACIF_SEL0ピンとMACIF_SEL1ピンを設定することにより、MAC インターフェースを選択することができます。MACIF_SEL0 ピンと MACIF_SEL1 ピンには、弱い内部プルダウン抵抗が実装されていることに注意してください。このため、ストラップ抵抗が外付けされていない場合は、デフォルトの MAC インターフェースは遅延が 2ns の RGMII になります。

| MAC Interface Selection | MACIF_SEL1 | MACIF_SEL0 |

| RGMII RXC/TXC, 2 ns Delay | Low | Low |

| RGMII RXC Only, 2 ns Delay | High | Low |

| MII | Low | High |

| RMII | High | High |

この回路ノートにおいて、MAC インターフェースの選択は、ADIN1300 内の GE_RGMII_CFG レジスタと GE_RMII_CFG レジスタをソフトウェアで設定することにより行われます。ハードウェアによって MACインターフェースを設定する場合は、プルアップ抵抗とプルダウン抵抗を外付けするためのフットプリントも実装されています。ただし、抵抗が実装されていないため、PHY が EVAL-CN0506-FMCZ 上でパワー・アップしたとき、デフォルトの RGMII インターフェースに設定されます。

PHY アドレス

PHY アドレス・ピン(PHYAD_x)が 4 ピンあるため、PHY に16通りのPHYアドレスを設定することができます。PHYにアドレスを設定できるため、システムは 1 つのコントローラで最大16 の独立した制御可能なチャンネルを装備することができます。

EVAL-CN0506-FMCZは現状では、特定のアドレスに配線されていますが、各チャンネルに対応する設定抵抗に変更することによりアドレスを変更できます。現状、チャンネル 1 はアドレス0001 に指定され、チャンネル 2 はアドレス 0010 に指定されています。

プログラム可能な MAC インターフェース・クロック

ADIN1300 には、MII、RMII、または RGMII の 3 つの MAC インターフェース・オプションがあります。ADIN1300 において、RGMII と MII のインターフェースには 25MHzのクロックが必要で、RMII には 50MHz の外部クロックが必要です。アプリケーションによっては、25MHz の水晶発振器を XTAL_I ピンとXTAL_O ピンの近くに配置することもでき、また、RMII を使用する場合には、ホスト・コントローラ、MAC インターフェース、またはスイッチから PHY に必要な 50MHz のクロックを直接供給することもできます。

EVAL-CN0506-FMCZには100kHz~125MHzのプログラム可能な2 つの I2C クロック(Y1 と Y2)が搭載されているため、ADIN1300 が様々な MAC インターフェースで必要とするすべてのクロックをサポートすることができます。

デフォルトでは、パワー・アップ時に各チャンネルのクロックは 25MHz に設定されます。RMII MAC インターフェースを使用する場合、クロックを 50MHz にプログラムすることができます。

両方のクロックの I2C アドレスは同じですが、I2C アドレス変換器 LTC4316 を使用することにより、これらのクロックは互いに異なるように個別にプログラムすることができます。LTC4316は、入力アドレスと、チップの抵抗分圧ネットワークによって設定された変換バイトとを XOR 演算して、各入力ビットを変換します。

MDI インターフェース — 磁気回路内蔵

MDI インターフェースにより、ADIN1300 は一般にトランスとRJ45 コネクタを通してイーサネット・ネットワークに接続されます。CN-0506 には、磁気回路が内蔵された RJ45 コネクタが使用されています。RJ45 コネクタに内蔵された磁気回路を使用すると、ディスクリートの磁気回路を使用した場合と比べて、一般に電磁干渉(EMI)シールドが改善され、また、フットプリントが小さくなり、配線パターンも短くなります。

統合化された磁気回路は、RJ45 コネクタ、コモンモード・チョーク、絶縁トランス、LED、デカップリング・コンデンサ、および終端抵抗で構成されています。設計上、過電圧条件が異なる場合や、特定の EMI に対して異なるレイアウトが要求される場合には、ディスクリートの磁気回路を使用することもできます。

電源

ADIN1300、MDIO、および MAC インターフェース用のアナログ回路の電源は、電源の数を減らすために、FPGA の 3.3V レールからフェライト・ビーズを介して供給されます。フェライト・ビーズによって、システムに侵入するノイズを低減させることができます。

ADIN1300 のデジタル・コアには 0.9V の電源が必要です。この電源は、3.3V レールからボード上の LT3502 パルス幅変調(PWM)降圧 DC/DC コンバータを介して供給されます。このコンバータでは、FPGA からの 3.3V 電源が 0.9V に変換され、キャリアからの電力が最大で 0.45W 消費されます。

ソフトウェアの概要

CN-0506 を使用するために提供されている FPGA リファレンス設計によって、各 ADIN1300 は個別に設定されます。各 PHY(ADIN1300)は、指定された MAC インターフェースに接続されます。また、ADIN1300 と FPGA 間は、RGMII、MII、およびRMII の 3 つのインターフェース・モードがサポートされています。

一部のモードで変換器を必要とするため(ギガビット MII(GMII)から RGMIIなど)、モードごとに個別のハードウェア設計言語(HDL)があります。動作モードは、Linuxで使用したいモードに一致する HDL で選択する必要があります。

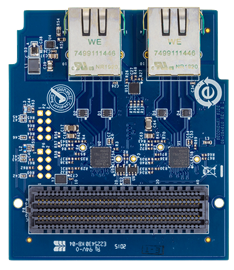

EVAL-CN0506-FMCZ は、標準のロー・ピン・カウント(LPC)FMC コネクタに接続することができます。これにより、ソフトウェア設計が多くの様々な FPGA 開発ボードに移植可能になります。

様々なモードとキャリアを組み合わせるためにサポートされている Linuxデバイス・ツリーは、CN0506 HDL pageで参照することができます。アナログ・デバイセズの標準 Linux イメージの詳細については、FPGA Image user guide を参照してください。

ボード・レイアウト時の考慮事項

イーサネット信号のレイアウトは、ギガビットの速度で特に重要です。信号は、100Ωに調整されたインピーダンスのペアでRJ45 ジャックに配線されています。

キャリアに向かうデータ信号とクロック信号は、低いクロック・レートで動作しますが、エッジ・レートに関してレイアウトに細心の注意を払う必要があります。EVAL-CN0506-FMCZ上の信号はできるだけ短くする必要がありますが、CN-0506 と接続するキャリア・ボード上の信号パターン長とインピーダンス・マッチングにも細心の注意を払う必要があります。これらの要素は、CN-0506 の全体的な速度と性能に重要ですが、個々に考慮する必要があります。

図 4 に、V2 から V1 にかけて 98.7%に低下している 1000BASE-Tの最大ドループ・ポイントを示します。

性能の測定結果

CN-0506 を使用して、モード検証テスト、速度テスト、ケーブル長を変えての駆動テストなど、複数のテストを行いました。

EVAL-CN0506-FMCZは、ケーブル長を延長して様々なモードでテストしました。ケーブル長が 4 メートルのときの測定結果を表 2 に、ケーブル長が 154メートルのときの測定結果を表 3に示していますが、パケット・ロスは発生していません。

表 2 と表 3 は、短距離のケーブル伝送と長距離のケーブル伝送における、ローカル・イーサネット PHY 位置とリモート・イーサネット PHY 位置での、ADIN1300 のフレーム・チェッカ・カウント・レジスタ(FC_FRM_CNT_H と FC_FRM_CNT_L)のリードバック値と、受信エラー・カウント・レジスタ(RX_ERR_CNT)のリードバック値を示しています。

| Speed (Mbps) | Mode | Local Ethernet PHY | Remote Ethernet PHY | Status | ||||

| FC_FRM_CNT_H | FC_FRM_CNT_L | RX_ERR_CNT | FC_FRM_CNT_H | FC_FRM_CNT_L | RX_ERR_CNT | |||

| 1000 | RGMII | 744 | 6314 | 0 | 744 | 6314 | 0 | Pass |

| 100 | RGMII | 74 | 26853 | 0 | 74 | 26853 | 0 | Pass |

| 10 | RGMII | 7 | 2890 | 0 | 7 | 2890 | 0 | Pass |

| 100 | MII | 74 | 26849 | 0 | 74 | 26849 | 0 | Pass |

| 10 | MII | 7 | 28900 | 0 | 7 | 28900 | 0 | Pass |

| Speed (Mbps) | Mode | Local Ethernet PHY | Remote Ethernet PHY | Status | ||||

| FC_FRM_CNT_H | FC_FRM_CNT_L | RX_ERR_CNT | FC_FRM_CNT_H | FC_FRM_CNT_L | RX_ERR_CNT | |||

| 1000 | RGMII | 744 | 7693 | 0 | 744 | 7693 | 0 | Pass |

| 100 | RGMII | 74 | 26847 | 0 | 74 | 26847 | 0 | Pass |

| 10 | RGMII | 7 | 28900 | 0 | 7 | 28900 | 0 | Pass |

| 100 | MII | 74 | 26849 | 0 | 74 | 26849 | 0 | Pass |

| 10 | MII | 7 | 268900 | 0 | 7 | 268900 | 0 | Pass |

回路の評価とテスト

データの完全性と帯域幅は、産業用ネットワークにおいて重要です。データ・ループバック・テストを行うと、EVAL-CN0506-FMCZ、ケーブル、コネクタなどの全体のシステムを検証できます。セットアップとテストの詳細については、CN0506ユーザ・ガイドを参照してください。

必要な装置

以下の装置類が必要になります。

- EVAL-CN0506-FMCZ 回路評価用ボード

- CAT6 イーサネット・ケーブル

- ZC706 FPGA 開発ボード

- SD カード

- USB タイプ A ドングル付きワイヤレス・キーボードおよびマウス

- マイクロ USB On the Go(OTG)アダプタ

- 高解像度マルチメディア・インターフェース(HDMI)オス/HDMI オス・ケーブル

- HDMI モニタ

- CN0506 用に設定されたアナログ・デバイセズの Linux イメージ

設計の開始にあたって

以下の内容を含む AD-FMC-SDCARD for Zynq & Altera SoC Quick Start Guide に詳述されている手順に従って、SD カードを準備します。

- 最新の FPGA Linux イメージをダウンロードします。

- SD カードをフォーマットします。

- FPGA Linux イメージを SD カードに書き込みます。

- CN-0506 用の boot.bin とデバイス・ツリー・ファイルを SDカードのブート・パーティションにコピーします。

機能ブロック図

テスト・セットアップの機能ブロック図を図 5 に示します。

セットアップ

以下の手順に従って、テストのセットアップを行います。

- LPC FMC コネクタを使用して、EVAL-CN0506-FMCZ をZC706 FPGA 開発ボードに取り付け、10mm のスタンドオフを使用してボード間を固定します。

- 事前に設定しておいた SD カードを Xilinx ZC706 に挿入します。

- 2 つの RJ45 イーサネット・ジャック間にイーサネット・ケーブルを接続して、ループバックを構成します。

- HDMI モニタと Xilinx ZC706 間に HDMI ケーブルを接続します。

- マイクロ USB OTG アダプタを Xilinx ZC706 のマイクロUSB ポートに接続します。

- USB タイプ A ドングルを使用して、ワイヤレスのキーボードとマウスを USB OTG アダプタに接続します。

- 電源コネクタを Xilinx ZC706 に接続し、他端を壁の電源に接続します。

テスト

システムをループバック・モードでテストします。すなわち、一連の大きなデータを生成して、一方のチャンネルからもう一方のチャンネルに送ったり、送り戻したりします。

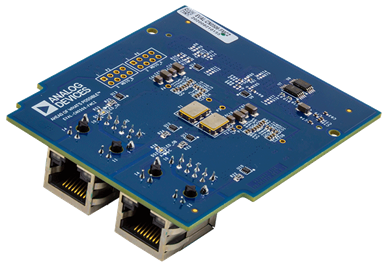

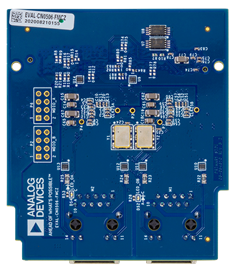

EVAL-CN0506-FMCZ 回路評価用ボードの写真を図 6 に示します。

テスト・セットアップに関する詳細、および EVAL-CN0506-FMCZ の使用方法については、CN0506 ユーザ・ガイドを参照してください。