製品概要

機能と利点

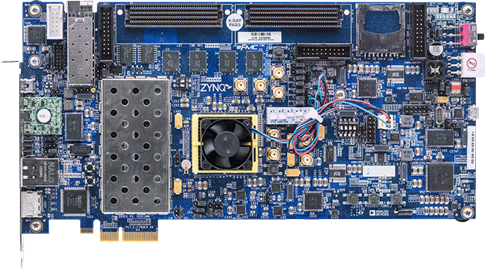

- Upgraded with -3 speed grade XC7Z045 FFG900 supporting up to 12.5 Gbps JESD204B Lane Rates

- 1 GB (PS) DDR3 Component Memory

- 1 GB (PL) SODIM Memory

- GigE Ethernet

- USB Host

- FMC LPC and HPC Expansion Ports

- 12 V Adapter powers Zynq® Evaluation Kit

- Provides Power for RadioVerse Transceiver Evaluation Boards via FMC Connector

製品概要

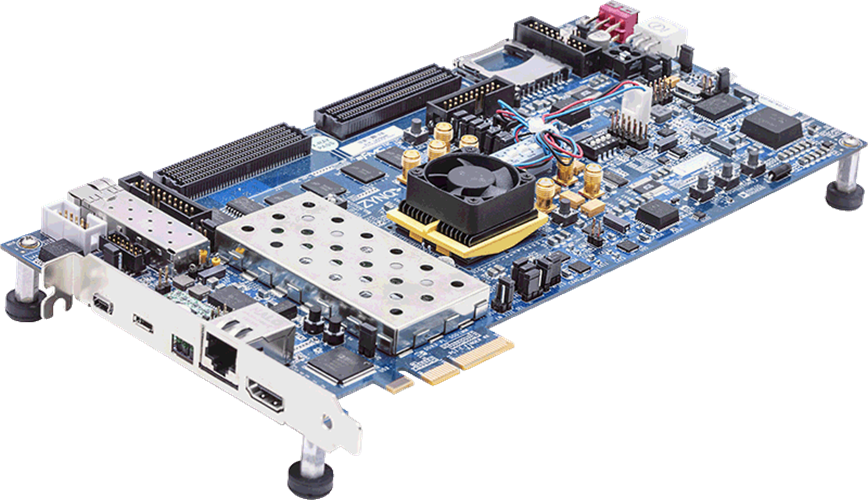

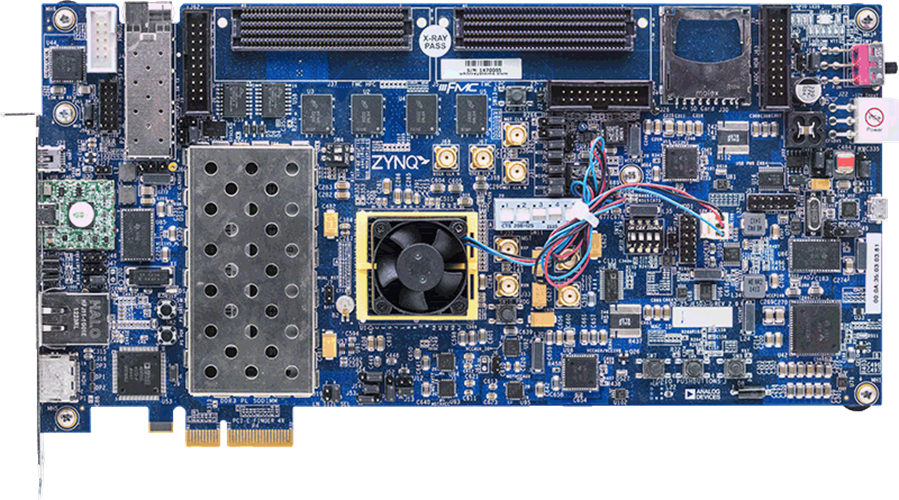

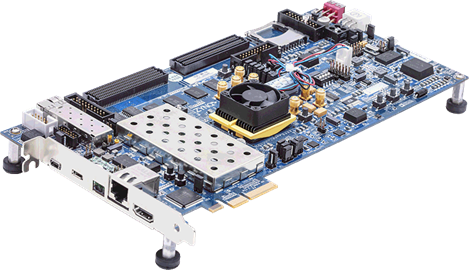

The Zynq®-7000 All Programmable SoC Evaluation Kit Optimized for JESD204B provides a data capture platform for many of the RadioVerse families of wideband transceiver evaluation boards. A single 12 V power supply provides power for both the Zynq® and the RadioVerse evaluation boards. The data capture platform interfaces to the RadioVerse evaluation boards through a variety of interfacing standards including JESD207 and JESD204B. The JESD204B interface on the Zynq® evaluation system supports up to 12.5 Gbps lane rates. A variety of interface options allows the evaluation kit to interface directly to a PC monitor, keyboard, and mouse as well to a PC running the Transceiver Evaluation or Prototyping Software Packages.

Comparison of ZC706 and EVAL-TPG-ZYNQ3 is listed as below.

| Board | FPGA part no. | Speed grade | Package type | GTX speed supported (Gb/s) | Transceiver Evaluation Platform Supported |

| ZC706 | XC7Z045 FFG 900 -2 | -2 | FF | 10.3125 | AD9371, AD9375 |

| EVAL-TPG-ZYNQ3 | XC7Z045 FFG 900 -3 | -3 | FF | 12.5 | AD9371, AD9375, ADRV9009, ADRV9008-1/-2 |

マーケット&テクノロジー

対象となる製品

パッケージの内容

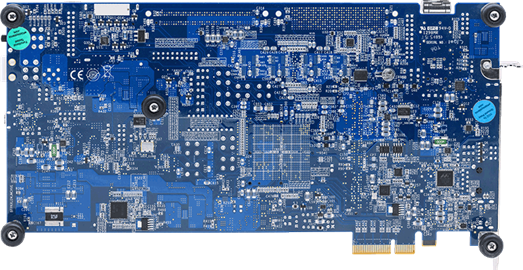

- ZC706 evaluation board upgraded with XC7Z045 FFG900-SOC

- Power supply

- For the user guide with AD9371 and AD9375, please refer to the section “AD9371 Demonstration System Overview” of the AD9371 User Guide UG-992.

関連資料

-

SDR集積化トランシーバの設計リソース2024/07/16