AN-2625: 複数のADE ADC を使用した設計

はじめに

このアプリケーション・ノートでは、複数のADE ADC を使用したシステムの設計および設定方法について概説します。

対応するデバイス

構成

デイジーチェーンのSPI

要件

以下に、デイジーチェーン接続されたSPI の構成に必要な条件を列挙します。

- すべてのデバイスは、同じクロック源で動作させてください。

- すべてのデバイスには、単一のチップ・セレクト(CS)を使用してください。

- データ・レディ(DREADY)の出力は、1 つのデバイスからのみで十分です。

- 詳細については、データ・レディ・ピン(DREADY)のセクションを参照してください。

複数のチップ・セレクトを使用したSPI

要件

以下に、複数のチップ・セレクトを使用したSPI の構成に必要な条件を列挙します。

- それぞれのデバイスには、個別のチップ・セレクトを接続してください。

- ADC を同期させる必要がある場合は、以下を参照してください。

- すべてのデバイスは、同じクロック源で動作させてください。

- すべてのCS ラインは、同期してトグルできるようにする必要があります。

- 1 つのDREADY 出力のみが必要となります。

- ADC を同期させる必要がない場合は、以下を参照してください。

- すべてのデバイスは、異なるクロック源で動作させることができます。

- CS ラインを同期させる必要はありません。

- すべてのDREADY 出力は、マイクロコントローラに個別に出力してください。

- 詳細については、データ・レディ・ピン(DREADY)のセクションを参照してください。

設計/ソフトウェアに関する考慮事項

以下のセクションでは、複数のADC を使用したボード設計の際に注意すべき設計に関する考慮事項を説明します。

SPI SCLK のバッファ

複数のADC が長く距離をとって配置されている場合は、1:x のファンアウト・バッファを使用することを推奨します。ここで、x はチェーン内にあるADCの数です。これにより、SCLKパターンの分岐を無くすことができ、高速のSPI 動作時に発生する反射や信号の完全性の問題を防ぐことができます。また、個々のパターンがカバーすべき最大距離も短くできます。高速のSPI動作には、低遅延のファンアウト・バッファを使用してください(図3 を参照)。

MCLK のバッファ

SPI SCLK のバッファと同様(SPI SCLK のバッファのセクションを参照)、MCLK 信号もバッファによって分岐とパターン長を低減することを推奨します。これを行うには、SPI SCLK と同じように低遅延のファンアウト・バッファを使用する方法と、ADC 自身にクロックをバッファさせる方法の2 通りがあります。本稿に対応するADC(ADEMA12x およびADE91xx)はすべて、CLKOUT/DREADY ピンからMCLK を出力する機能を備えています(詳細については、対応するデバイスのセクションを参照)。図4 で、ADC1 には水晶発振器がXTALIN/XTALOUT ピンに接続されており、これがMCLK を生成します。そしてADC1 とADC2 は、CLKOUT/DREADYピンからMCLKを出力するよう設定されており、これは後段のデバイスのXTALIN に送信されます。チェーンの最後のデバイス(この場合はADC3)は、DREADY(データ・レディ)を出力するよう設定されており、これはMCU に送信されます。これにより、ADC から新しいデータをリードバックする準備ができたことをMCUに伝えます。

チェーン内にADE91xx デバイスがある場合、これをクロック源(図4 のADC1)として使用しないでください。クロックはADEMA12x を使用して供給してください。

ADC の同期

複数のADC を同じSPI バスに接続する場合、ADC のサンプリングは、すべてのデバイス間で±1MCLK サイクルで同期できます。すべてのADC は、同じMCLK 源かつ同じ出力データ・レートで動作する必要があります。複数のチップ・セレクト設定では、すべてのチップ・セレクト・ラインを同時にローにアサートできるようにする必要があります。複数のADC の同期に関する詳細については、ADEMA124/ADEMA127 のデータシートのSynchronization of Multiple Devices のセクション、およびADE9103/ADE9112/ADE9113 のデータシートの複数のADE9103/ADE9112/ADE9113 デバイスの同期化のセクションを参照してください。また、同期方法についてのステップ・バイ・ステップによる説明は、本アプリケーション・ノートのSync/Snap の手順のセクションを参照してください。

デイジーチェーンにADEMA124/ADEMA127 を使用する場合の注意事項

デイジーチェーンにADEMA124 またはADEMA127 がある場合、DATAPATH_CONFIG_LOCK がトグルされると必ず、ADC は変換を停止し再開します(ADEMA124/ADEMA127 のデータシートのConfiguration Lock and Access Bit のセクションを参照)。そのため、ADC 間の同期が失われる可能性があります。

以下のセクションで、DATAPATH_CONFIG_LOCK がトグルされた後にADC の同期を保つための2 つのソリューションを説明します。

ソリューション1(推奨)

いずれかのデバイスでDATAPATH_CONFIG_LOCK がトグルされた後、すべてのADC を再度同期します。このソリューションは、(ADEMA12x とADE91xx の)あらゆるデバイスの組み合わせで有効です。この方法は、ADC service によってサポートされています。energy ADC service では、アナログ・デバイセズの電力量計用ADC と通信するためのAPI 一式が提供されています。ADC service については、https://github.com/analogdevicesinc/energy-adc-service を参照してください。

ソリューション2

チェーンのすべてのデバイスがADEMA12x である場合、1 つのSPI トランザクションでDATAPATH_CONFIG_LOCK をディスエーブルしてから再イネーブルする、すなわち、すべてのデバイスを同時にロック解除してからロックする、という操作を行うことでADC の同期を維持できます。この方法は、ADC serviceでは提供されていません

Sync/Snap の手順

このセクションでは、ADC の同期方法、およびデイジーチェーンと複数のチップ・セレクトの両方のSPI 設定におけるアライメント確立の方法について、ステップ・バイ・ステップで手順を説明します。

デイジーチェーンのSPI 構成

アライメントと判定

以下の手順で、ADC を同期し、アライメントが確立されたことを判定する方法を説明します。

1. すべてのデバイスのSYNC_SNAP レジスタ(0x14)に0x2 を書き込みます。

- ALIGN ビットを1 に設定します。

2. すべてのデバイスのSNAPSHOT_COUNT_HI(0x17)およびSNAPSHOT_COUNT_LO(0x18)レジスタを読み出します。

3. すべてのデバイスのSYNC_SNAP レジスタ(0x14)に0x1 を書き込みます。

- SNAPSHOT ビットを1 に設定します。

4. すべてのデバイスのSNAPSHOT_COUNT_HI(0x17)およびSNAPSHOT_COUNT_LO(0x18)レジスタを読み出します。

5. 同期させた後の各ADC のSNAPSHOT_COUNT_x レジスタを比較して、同期が正常に行われたことを確認します。

- 数値が±1 以内であることが必要です。

判定のみ

1. すべてのデバイスのSYNC_SNAP レジスタ(0x14)に0x1 を書き込みます。

- SNAPSHOT ビットを1 に設定します。

2. すべてのデバイスのSNAPSHOT_COUNT_HI(0x17)およびSNAPSHOT_COUNT_LO(0x18)レジスタを読み出します。

3. 各ADC のSNAPSHOT_COUNT_x レジスタを比較して、同期されていることを確認します。

複数のチップ・セレクトを使用したSPI 構成

アライメントと判定

以下の手順で、ADC を同期し、アライメントが確立されたことを判定する方法を説明します。

1. すべてのデバイスのSYNC_SNAP レジスタ(0x14)に0x6 を書き込みます。

- ALIGN ビットを1 に設定します。

- PREP_BROADCAST ビットを1 に設定します。

2. すべてのデバイスのSNAPSHOT_COUNT_HI(0x17)およびSNAPSHOT_COUNT_LO(0x18)レジスタを同時に読み出します。

- すべてのデバイスのCS が同時にハイからローに遷移することが重要です。

3. すべてのデバイスのSYNC_SNAP レジスタ(0x14)に0x5 を書き込みます。

- SNAPSHOT ビットを1 に設定します。

- PREP_BROADCAST ビットを1 に設定します。

4. すべてのデバイスのSNAPSHOT_COUNT_HI(0x17)およびSNAPSHOT_COUNT_LO(0x18)レジスタを同時に読み出します。

5. 同期させた後の各ADC のSNAPSHOT_COUNT_x レジスタを比較して、同期が正常に行われたことを確認します。

- 数値が±1 以内であることが必要です。

判定のみ

ADC の同期を定期的に判定することによって、判定のみを使用することも可能です。同期が想定範囲から外れていた場合は、再同期できます。

1. すべてのデバイスのSYNC_SNAP レジスタ(0x14)に0x5 を書き込みます。

- SNAPSHOT ビットを1 に設定します。

- PREP_BROADCAST ビットを1 に設定します。

2. すべてのデバイスのSNAPSHOT_COUNT_HI(0x17)およびSNAPSHOT_COUNT_LO(0x18)レジスタを読み出します。

3. 各ADC のSNAPSHOT_COUNT_x レジスタを比較して、同期されていることを確認します。

データ・レディ・ピン(DREADY)

対応する各ADC には、CLKOUT/DREADY と名付けられたデータ・レディ・ピン(DREADY)が備わっています。その名が示すように、このピンを使用してMCLK とデータ・レディ信号の出力を設定できます。データ・レディ信号がハイからローに遷移することで、ADC から新しいADC データを読み出せる状態になったことを示します。この信号の周波数は、動作中のADCのデータ・レートに応じて異なります(詳細については、対応するデバイスのセクションを参照)。同期するには、すべてのADC が同じMCLK 源かつ同じデータ・レートで動作している必要があります。そのため、デイジーチェーン内でADEMA12x とADE91xx を一緒に使用する場合は、特定のデータ・レートのみが使用できます(表1 を参照)。すべてのADC が同期されると(ADC の同期のセクションを参照)、すべてのデバイスのデータ・レディが同期されます。そのため、ホストのMCUに送信する必要があるのは、1 つのDREADY 出力信号のみです。ADC の同期が必要でない場合には、すべてのDREADY ピンからマイクロコントローラに送信する必要があります。

| Data Rate | ADEMA12x2 | ADE91xx2 |

| 64ksps | X | |

| 32ksps | X | X |

| 16ksps | X | |

| 8ksps | X | X |

| 4ksps | X | X |

| 2ksps | X | X |

| 1ksps | X | X |

| 500sps | X | |

| 250sps | X |

デイジーチェーン構成でのADC の最大サンプル・レート

デイジーチェーン構成では、すべてのADC は同じSPI バスを共有します。そのため、チェーン内のADC の数が多いほど、SPIフレームが伝送するデータは増加します。このため、SPI 速度とADC の数に応じて対応できる出力データ・レートの最大値には制限があります。すべてのADC は、ロング形式でデータを出力するように設定する必要があります(詳細については、対応するデバイスのセクションを参照)。SPI アイソレータが必要な場合は、アイソレータの伝搬遅延を計算に含めてください(アイソレータの使用を検討する場合は、アプリケーション・ノートAN-1478、特定のシステム条件を対象とする絶縁型SPI バスを参照してください)。

以下の計算を参照してください。

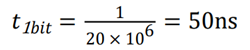

1. 1 ビット時間を計算します。これは、1 ビットが伝送されるのに要する時間で、単位は秒です。

2. フレーム長を計算します。これは、伝送される総フレームの長さで、単位はビットです。

| ADC | Frame Length (bits) |

| ADEMA124 | 160 |

| ADEMA127 | 256 |

| ADE9113 | 128 |

| ADE9112 | 128 |

| ADE9103 | 128 |

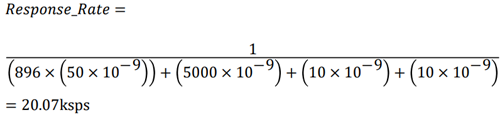

3. 応答レートを計算します。これは、目的の設定に対応するのに必要な最小サンプル・レートで、単位はサンプル/秒です。

ここで、

tCH = SPI トランザクション間でのCS ハイ時間(ns)。

tSS = CS とSCLK 立上がりエッジの間の時間(ns)。

tSFS = SPI トランザクション間でのCS ハイ時間(ns)。

4. ルックアップ・テーブルを使用して対応するデータ・レートを選択してください(対応するデータ・レートについては表1を参照)。

動作例

1 個のADE9113 と3 個のADEMA127 の4 個のADC をチェーン構成で使用し、SCLK = 20MHz、tCH = 5000ns、tSS = 10ns、tSFS =10ns とします。

下記のように計算します。

1.

2. Frame_Length = 128 + 256 + 256 + 256 = 896 bits

3.

4. ADE9113 とADEMA127 を一緒に使用する場合、特定のデータ・レートのみが対応可能です。ADE9113 は16ksps のオプションを備えていないため、対応可能な最大データ・レートは8ksps です。

| Data Rate | ADEMA12x1 | ADE91xx1 |

| 64ksps | X | |

| 32ksps | X | X |

| 16ksps | X | |

| 8ksps | X | X |

| 4ksps | X | X |

| 2ksps | X | X |

| 1ksps | X | X |

| 500sps | X | |

| 250sps | X |

例

以下のセクションでは、1 個のADE9113 と3 個のADEMA127 を使用したデイジーチェーン構成の例を示します。

ハードウェアの構成

図6 に示すように、ホスト・マイクロコントローラと4 個のADCを接続します。

ADC の設定

ADC をデイジーチェーン構成で使用するための設定方法を、以下の手順で説明します。

- すべてのADEMA127 デバイスで、CLKOUT/DREADYピンからMCLK を出力するように設定します。これは、ADEMA127 デバイスでCONFIG0 (0x2 ) レジスタのCLKOUT_EN ビットに0x1 を書き込むことによって設定できます。

チェーンの最初のADC(ホストMCUのMOSI ピンに接続されたデバイス)、次に2 番目のADC、その次に3 番目のADC、という順に書き込むことで、次段のADC と通信を行う前にMCLK を受信した状態にしておくことができます。 - すべてのデバイスが同じ出力データ・レートになるように設定します( 詳細については、データ・レディ・ピン(DREADY)のセクション、およびデイジーチェーン構成でのADC の最大サンプル・レートのセクションを参照)。

ADEMA127 では、DATARATE(0x03C)レジスタに書き込むことで出力データ・レートを設定します。(詳細については、ADEMA124/ADEMA127 のデータシートのOutputSample Rate のセクションを参照)。

ADE9113 では、CONFIG_FILT (0x3) レジスタのDATAPATH_CONFIG[2:0]ビットに書き込むことで出力データ・レートを設定します。 - 各ADC を同期します。詳細については、ADC の同期のセクションを参照してください。

ソフトウェアの設定

energy ADC service では、アナログ・デバイセズの電力量計用ADC と通信するためのAPI 一式が提供されています。ADCservice については、https://github.com/analogdevicesinc/energy-adcserviceを参照してください。