AN-2623: 高速周波数ホッピング・アプリケーションでのADF4382/ADF4382A/ADF4383 の高速キャリブレーション機能の使用

はじめに

高速周波数ホッピングを使用するフェーズド・アレイや通信システムなど、フェーズ・ロック・ループ(PLL)周波数生成アプリケーションの多くでは、周波数の切り替えに必要な時間の最短化が非常に重要となります。ADF4382/ADF4382A/ADF4383では高速キャリブレーションを導入しており、この機能により総合的なロック時間が大幅に短縮され、周波数の高速な移行が可能です。

ADF4382/ADF4382A/ADF4383 シリーズのPLL デバイスには、2 つのコアと512 個の重なり合う帯域があり、広い基本周波数範囲をカバーできます。出力周波数を選択するデフォルトの方法では、内蔵の自動キャリブレーション・ルーチンを使用して、プログラムされたRF 出力周波数と動作温度に基づいて適切なVCO コアと帯域を選択します。このルーチンでは、周波数変化ごとに最短でも100μs の時間がかかります。

周波数を切り替えたときの総合的なロック時間には、自動キャリブレーションの時間と、ループ・フィルタでのチューニング電圧(VTUNE)のセトリング・タイムが含まれます。高速キャリブレーションを使用すると、VCO 帯域を切り替えるときの自動キャリブレーション処理全体を省略することができ、総合的なロック時間が大幅に短縮されます。

このアプリケーション・ノートでは高速キャリブレーションの設定手順を概説し、動作原理を解説し、動作例の結果を示します。

ロック時間を決める要因

フェーズ・ロック・ループのロック時間とは、前の出力周波数から新しい出力周波数に向けてロックするのにかかる時間を指します。この時間、デバイスのロックは外れています。理想的な周波数変化を図1 に示します。ロック時間は、自動キャリブレーション時間とループ・フィルタのVTUNE 電圧セトリング・タイムで構成されます。

総合ロック時間の計測の開始点は、周波数が変化を開始する点です。ADF4382/ADF4382A/ADF4383 の場合には、これはキャリブレーションをトリガするN_INT ビット・フィールド(レジスタ0x010)への書込みになります。図2 に図示するように、このレジスタ書込みの最後のSPI クロック信号の立上がりエッジで周波数の変化が始まります。

デバイスがロックしたとみなされる点は、ユーザ・アプリケーションの仕様により異なります。例えば、使用するセトリング閾値のパラメータは、アプリケーションにより、周波数、位相、チューニング電圧のセトリング・ウィンドウなどである場合があります。使用する閾値の値は、1ppm、10ppm、あるいは定義された周波数や電圧のウィンドウであるかもしれません。このアプリケーション・ノート内で結果を標準化する目的で、セトリング・バンド幅として30kHz のセトリング・ウィンドウを使用します。これは、最終の周波数の±30kHz 以内にセトリングし、その30kHz のウィンドウから出なくなったときに、デバイスがロックしたと判定するという意味です。

自動キャリブレーション

自動キャリブレーションは、ユーザ定義のインテジャー・ワードとフラクショナル・ワードに基づいて適切なコアと帯域の値を選択するデフォルトの方法です。EN_AUTOCAL = 1(レジスタ0x0020、ビット7)をセットすることによってイネーブルされます。N_INT(レジスタ0x0010)に書き込むことによって新しい周波数が設定されると、自動キャリブレーション・ルーチンがトリガされます。このルーチンでは、目的の出力周波数を得るために、まず適切なコアを選択し、選択されたコアの中で512 個の帯域から1 つを選択します。帯域は、動作温度(−40ºC~105ºC)に基づいて選択します。例えば、デバイスが高い温度で動作する場合、その出力周波数を得るための高いVTUNE 電圧に対応する帯域が選択されます。同様に、低温で動作する場合には、低いVTUNE 電圧の帯域が選択されます。自動キャリブレーションを使用するメリットの1 つは、選択した周波数が一度ロックすると、デバイスの動作温度範囲(−40ºC~105ºC)全体にわたって、自動キャリブレーションを再実行することなくロック状態が継続することです。これは常時ロック(lock and leave)範囲として知られています。

使用するデフォルトの自動キャリブレーション時間は250μs で、これは常時ロック範囲の方がロック時間を短縮するよりも重要であるアプリケーションについて推奨される値です。温度範囲にわたり常時ロック性能を確保しながら実現しうる最短の自動キャリブレーション時間は100μs です。自動キャリブレーションの詳細については、ADF4382/ADF4382A/ADF4383 のデータシートを参照してください。

図4 は、自動キャリブレーション中のコアと帯域の選択と、それに続く選択された帯域内でのVTUNE 電圧のセトリングによる周波数セトリングでの、周波数と時間の関係を図示しています。

ループ・フィルタのセトリング

VTUNE 電圧のセトリング・タイムは、ループ・フィルタの部品構成に依存します。ループ帯域幅が広い設定を使用すると、狭い帯域幅のループ・フィルタを使用する場合と比較してセトリング・タイムが大幅に短くなります。ループ・フィルタの例を図5 に示します。これは、インテジャー・モードの出力周波数を使用して、FPFD = 250MHz となるように設計したものです。このループ・フィルタを使用した一般的なVTUNE セトリング・タイムは10μs 未満です。フラクショナル・モードの出力周波数が必要な場合には、追加の部品を使用して大きなオフセット時のシグマ・デルタ・モジュレータ(SDM)ノイズを抑制します。ループ・フィルタ回路で大きい値のコンデンサを使用すると、VTUNEセトリング・タイムが長くなります。

高速キャリブレーションを使用する場合、VTUNE セトリング・タイムが総合的なロック時間の主要な要素となります。ロック時間がシステムで重要な仕様なのであれば、ループ・フィルタの設計を注意深く検討する必要があります。ADISimPLL を使用すると、ループ・フィルタの位相ノイズ応答を正確に設計、モデル化できます。

高速キャリブレーションのコンセプト

高速キャリブレーションでは、ルックアップ・テーブル(LUT)アプローチを使用し、デバイスのオクターブ周波数範囲全体に間隔を置いて配置された32 点に対するコアと帯域の値を保存します。その値は、高速キャリブレーション生成ステージ中に保存されます。この値を得るために、デバイスの初期化後にその32 の出力周波数での自動キャリブレーションを実施します(高速キャリブレーションの手順のセクションを参照)。この動作は高速キャリブレーションLUT 生成手順を実施するときに自動的に実行され、ユーザは各周波数を個別に設定する必要はありません。LUT 生成ステージ後は、ユーザが開始した周波数変更はすべて高速キャリブレーションを使用して実行されます。

高速キャリブレーションは、ユーザが選択した周波数に対し、2 つのLUT 周波数点の間で補間を実施して適切なコアと帯域の値を取得します。各周波数についての高速キャリブレーション時間は2μs 未満で、全体的なロック時間が大幅に短縮されます。図6は、オクターブ周波数範囲にわたって生成された32 のLUT点のプロット例と、高速キャリブレーションで使用する補間帯域値を示しています。

ルックアップ・テーブルのスケーリング

LUT の生成に使用できる最大のPFD(位相周波数検出器)周波数は125MHz です。通常動作時(LUT 生成後)に必要なfPFD が125MHz を超過する場合には、125MHz 以下の初期スケール・ダウンPFD 周波数をLUT 生成に使用する必要があり、これをfPFD_LUT と呼びます。

fPFD_LUT はリファレンス信号経路に設定する必要があります。これは、リファレンス分周器(R_DIV)の値を適宜調節することによって行います(レジスタ0x20、ビット[5:0])。

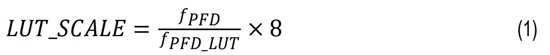

LUT 値に適用されるスケーリング・ファクタはLUT スケーリング値により決まり、この値は必要な動作時のfPFD とLUT 生成用のfPFD_LUT の比率に基づいて計算されます。スケーリング・ファクタはLUT_SCALE レジスタ(レジスタ0x4F、ビット[7:0])で設定され、式1 を使用して計算します。

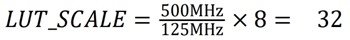

- 例1:ユーザ設定で通常動作時にfPFD = 125MHzを使用する場合、fPFD = fPFD_LUTとなります。LUT_SCALEは次のように計算します。

R_DIV は、ユーザ設定の値から変化ありません。

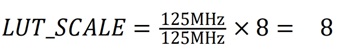

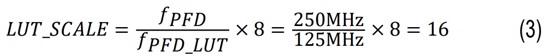

- 例2:ユーザ設定で通常動作時にfPFD = 250MHzが必要な場合、先にLUTの32点を125MHzで生成する必要があります。LUT_SCALEは次のように計算します。

この場合、LUT 生成前に更に2 の係数で分周するよう、R_DIVが加算されます。

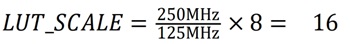

- 例3:ユーザ設定で通常動作時にfPFD = 150MHzが必要な場合、先にLUTテーブルを75MHzで生成する必要があります。LUT_SCALEは次のように計算します。

この場合も、LUT 生成前に更に2 の係数で分周するよう、R_DIV が加算されます。

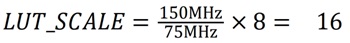

- 例4:ユーザ設定で通常動作時にfPFD = 500MHzを使用する場合、LUT生成時はfPFD_LUT = 125MHzとなります。LUT_SCALEは次のように計算します。

この場合、LUT 生成前に更に4 の係数で分周するよう、R_DIVが加算されます。

高速キャリブレーションの手順

デバイスを高速キャリブレーションに設定するためには、次の3 つの主な手順があります。

- デバイスの初期化:最初にデバイスを必要な電源電圧でパワーアップし、ユーザ設定に応じてレジスタの内容を書き込んで初期化する必要があります。完全なレジスタ・マップの詳細は、ADF4382/ADF4382A/ADF4383 のデータシートに記載されています。

- 高速キャリブレーションの設定:初期化後、32 点のLUT を生成してデバイスのメモリに保存します。この手順では、デバイスのオクターブ範囲にわたる32 点の出力周波数で自動キャリブレーションを実行することにより、各周波数でのコアと帯域の情報を得ます。更にこの手順では、VTUNE 係数値の更新、リファレンス分周器の調節によるLUT 生成用の適切なfPFD_LUT の設定、それに従うLUT_SCALE の設定も実施します。

- 高速キャリブレーションのイネーブル:LUTが生成され、値が保存されると、高速キャリブレーションを有効化できます。この手順では、自動キャリブレーション・ブロックをディスエーブルし、高速キャリブレーション・イネーブル・ビットをセットします(EN_LUT_CAL = 1)。もしfPFD ≠ fPFD_LUT であれば、リファレンス分周器の設定をユーザ設定値に戻すことも必要です。

以下の手順では、完全な高速キャリブレーションの設定手順を詳細に説明します。デバイスが既に必要な電源でパワーアップされ、ユーザ設定に応じてレジスタの内容が適切に初期化されていることを前提とします。この例で使用する製品品番はADF4383 で、fPFD = 250MHz です。

- VTUNE 温度係数の値を以下のように設定します。

- VPTAT_CALGEN(レジスタ0x44 ビット[6:0]) = 0x07

- VCTAT_CALGEN(レジスタ0x45 ビット[6:0]) = 0x15

- fPFD_LUT を決定します(ルックアップ・テーブルのスケーリングのセクションを参照)。この例では、fPFD_LUT = 125MHzとします。fPFD = 250MHz がこの整数倍であるようにしています。

- 追加係数2 で分周するようにR_DIV(レジスタ0x020、ビット[5:0])を設定します。この場合、通常動作中はfREF = fPFD になります。したがって、fPFD_LUT = 125MHz に設定するため、R_DIV = 2 が更新値になります。

- ルックアップ・テーブルの生成を開始するため、EN_LUT_GEN = 1(レジスタ0x36 ビット[1])をセットします。

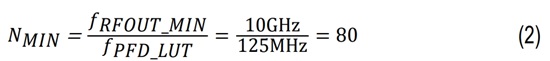

- fPFD と使用する品番に基づいて、基本的範囲での最も低い出力周波数(fRFOUT_MIN)を得るために必要なインテジャーN 値N_INTを計算します。ADF4383 の場合は、最低基本出力周波数は10GHz です。したがって、

- N_INT(レジスタ0x10 ビット[7:0]とレジスタ0x11 ビット[11:8]) = NMIN = 80 に設定し、最小RF 出力周波数を選択します。

この手順で、デバイスのオクターブ範囲にわたるRF 出力周波数に対する32 点のルックアップ・テーブルを生成し、その値をデバイスのメモリのアドレス0x201~0x273 の範囲に保存します。

この手順の間は、INT_MODE(レジスタ0x15 ビット2)を1にセットしておきます。これは、以前に書き込んだ値によってフラクショナル・ワードが使用されないようにし、確実に最小のオクターブ出力周波数が選択されるようにするためです。 - FSM_BUSY(レジスタ0x58 ビット[1])を読み出します。ルックアップ・テーブルの生成が完了していることを確認するには、リードバック値が0 になっていることが必要です。

- デバイスのLUT_SCALE(レジスタ0x4F ビット[7:0])を計算します。ルックアップ・テーブルのスケーリングのセクションに従い、

- ルックアップ・テーブルの生成をディスエーブルするため、EN_LUT_GEN = 0(レジスタ0x36 ビット[1])に設定します。

- 高速キャリブレーション設定処理では、デバイスの最大RF出力周波数に対応するコアと帯域の値で、LUT の最終点を上書きすることが必要です。次のようにします。

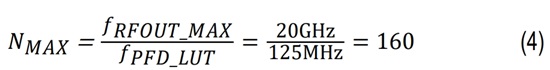

- 使用する品番での最大RF 出力周波数に基づいて最大N_INT 値を計算します。ADF4383 の場合は、最大出力周波数は20GHz です。したがって、

- N_INT(レジスタ0x010 ビット[7:0]とレジスタ0x11ビット[11:8]) = NMAX = 160 に設定します。(INT_MODE = 1)。

この点で、自動キャリブレーションを実施し、RF 出力周波数を20GHz に更新します。 - VCO_CORE(レジスタ0x05Fビット[1])とVCO_BAND(レジスタ0x05F ビット[0]とレジスタ0x05Eビット[7:0])を読み出します。

- 前の手順でのVCO_CORE とVCO_BAND のリードバック値をM_LUT_CORE(レジスタ0x202 ビット[1])とM_LUT_BAND(レジスタ0x202 ビット[0]とレジスタ0x201 ビット[7:0])に書き込みます。

- M_LUT_N(レジスタ0x203 ビット[5:0]とレジスタ0x202ビット[7:2]) = NMAX = 160 と書き込みます。

- LUT_WR_ADDR(レジスタ0x200 ビット[5:1]) = 31 に設定して、ルックアップ・テーブルのアドレスを設定します。

- オーバーライド・ビット・フィールドO_VCO_LUT(レジスタ0x200 ビット0) = 1 に設定し、ルックアップ・テーブルの最終ビット・フィールドを更新された帯域、コア、NMAX の値で更新します。

- 使用する品番での最大RF 出力周波数に基づいて最大N_INT 値を計算します。ADF4383 の場合は、最大出力周波数は20GHz です。したがって、

- PD_CALGEN ( レジスタ0x2A ビット0 ) = 0 、CAL_VTUNE_TO(レジスタ0x039 ビット[6:0]とレジスタ0x038 ビット[7:0]) = 0 と書き込んで、CAL_GEN ブロックをシャットダウンし、CAL_VTUNE タイムアウト・レジスタをクリアします。

- R_DIV(レジスタ0x020、ビット[5:0])の値をデバイスの初期化時に使用した元の値に戻し、fPFD = 250MHz、すなわちR_DIV = 1 の元の設定にします。

- EN_LUT_CAL(レジスタ0x36 ビット0) = 1 に設定して高速キャリブレーションをイネーブルします。これで、高速キャリブレーションがイネーブルされました。RF 出力を変更するときのロック時間が大幅に短くなります。

周囲温度がルックアップ・テーブルを生成したときの温度から±20ºC より大きく変動している場合には、ルックアップ・テーブルを再生成することを推奨します(手順3~12)。

常時ロック温度範囲

常時ロック温度範囲とは、初期ロック温度を基準として、再キャリブレーションを行うことなくデバイスのロックを保つことができる温度変動範囲を指します。

自動キャリブレーションを使用するとき、ADF4382/ADF4382A/ADF4383 のデータシートに規定のとおり、常時ロック温度範囲は全動作温度範囲と等しくなります。デバイスは極端な温度変化でもロック状態を保ちます。例えば−40ºCでキャリブレーションし、温度が+105ºC まで上昇しても動作を継続します。

高速キャリブレーションを使用する場合は、初期化中に32 点のルックアップ・テーブルを生成した後、デバイスがロックした状態を保てる範囲は、初期温度から±20ºC の範囲と狭くなります。例えば、高速キャリブレーションのルックアップ・テーブルの生成を30ºCで行い、デバイスが20GHz でロックした場合、出力は10ºC~50ºC の範囲でロックを維持します。この温度範囲の外では、性能が低下し、より大きい温度変化によってデバイスのロックが外れる可能性があるため、高速キャリブレーション・ルックアップ・テーブルを再生成することを推奨します。

結果

以下の結果は、2 つのRF 出力周波数の間でのロックにおける周波数セトリング・タイムの結果を示しています。結果は、周波数を時間領域で表現して示しています。計測の開始点となるトリガ・ポイントは、最後のSPI クロック・サイクルの立上がりエッジです。自動キャリブレーションの時間は通常の値である250μs に設定しています。

ループ・フィルタは、ロック時間のうちのVTUNE セトリング・タイム部分を短縮するため、1.11MHz という広いループ帯域幅に設定しています。

この結果から分かるように、周波数変化が11GHz から12GHz の場合も、12GHz から15GHz の場合も、高速キャリブレーションで大幅にロック時間が改善します。測定マーカー(M1)を30kHz のセトリング閾値ウィンドウに配置しており、前記の周波数変化時のロック時間が4.6μs と1.8μs であることが分かります。このループ・フィルタ設定で30kHz のセトリング・ウィンドウを使用した場合、ロック時間はデバイスの動作範囲全体で10μs 未満になります。ロック時間の変動は開始周波数と停止周波数によるVTUNE の変化に基づき、開始/停止周波数のステップ・サイズとは無関係です。

| Method | Lock time (μs) | |

| 11GHz to 12GHz | 12 GHz to 15 GHz | |

| Autocalibration | 274 | 274.4 |

| Fast Calibration | 4.6 | 1.8 |

図12 は位相ノイズの比較を示しており、自動キャリブレーション(黄)と高速キャリブレーション(青)で周波数変化を行った後の20GHz での位相ノイズを重ねて表示しています。

自動キャリブレーションと高速キャリブレーションのどちらも、開始周波数が15GHz、停止周波数が20GHz で周波数変化を実施しています。デバイスにはEV-ADF4382SD2Z 評価ボードに従ったデフォルトの設計のループ・フィルタを実装しています。この結果から分かるように、高速キャリブレーションをした場合にも、自動キャリブレーションを使用する場合と比較して位相ノイズの悪化は見られません。