AN-1456: AD5766/AD5767 でのデジタル・ディザ発生

はじめに

AD5766/AD5767 は 16 チャンネル、12 ビット/16 ビットのdenseDAC® D/A コンバータ(DAC)で、最小 -20 V から最大 +14V までの複数の出力電圧スパンを +2.5 V の外部リファレンスから生成し、同時に、チャンネルあたり最大 20 mA の出力電流を供給するように設定することが可能です。

AD5766/AD5767 は、アプリケーション・ノート AN-1446、AD5767 でのディザ発生に示すように、インジウム・リン・マッハツェンダー変調器(InP MZM)の最適な DC バイアス・ポイントを探して変調器の直交性を維持するための、アナログ・ディザ機能を内蔵しています。

アナログ・ディザ入力のアナログ入力周波数あるいは振幅の仕様が、所定の変調器範囲に対するアプリケーションの条件を満たさない場合は、DAC 自体でデジタル・ディザ(任意波形)を生成することができます。

このアプリケーション・ノートの目的は、出力信号の生成という観点からデジタル・ディザについて検討することにあります。

AD5766/AD5767 のブロック図を図 1 に示します。

AD5766/AD5767 のディザの詳細

デジタル・ディザの発生方法

サイン波、矩形波、三角波、その他任意の波形は、DAC レジスタを連続的に更新することによってデジタル的に生成できます。DAC を使用して生成された離散サンプルから再構成された信号に関して少しでも高い性能を保証するには、いくつかの基本原則を理解する必要があります。最大の更新レート、つまり 1 秒あたりの更新回数(Update Per Second: UPS)は、所定の分解能における出力のセトリング能力に合わせて制限する必要があります。

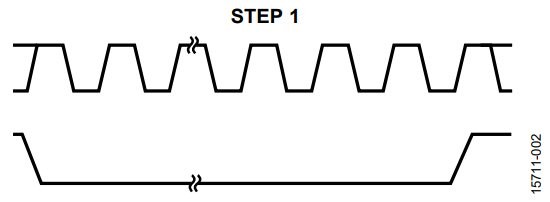

第 1 段階は、VOUTx ピンの更新に関わるステップを分析することです。

- 図 2 に示すように、新しい値が入力レジスタに書き込まれます。

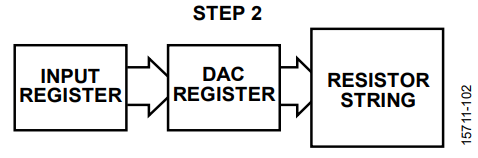

- 図 3 に示すように、デジタル・ブロックがコマンドを処理し、DAC レジスタを更新します。

- VOUTx 電圧が、レジスタに書き込まれた新しいコードによって定義される電圧にセトリングし始めます(図 4 参照)。

- ある不定の時間(図 4 参照)が経過すると、出力は新しいコードによって定義される値を中心とする許容値の範囲内(通常は最終コード ±0.5 LSB)に落ち着きます。

一般に、DAC がステップ 1 からステップ 4 へ移行する時間が短いほど、多くのサンプルを生成する(1 秒あたりの更新回数を多くする)ことができますが、これは 2 つのことを示唆しています。第 1 に、生成される出力の数が多いほど生成される出力信号がスムーズになり、第 2 に、より高い周波数を生成することができます。

最大限の更新レートを得る方法

デフォルトでは、生成可能な 1 秒あたりの最大更新回数は、新しいコードが前のセクションのすべてのステップを完了するのに要する時間によって制限されます。このセクションでは、すべてのステップを分析し、それらのステップがセトリング時間に与える影響について説明します。

ステップ 1 はデジタル・クロックに依存し、最大クロック・レート(50 MHz)では、最小 SYNC ハイ時間などの他の時間的制約を考えなければ、480 ns(= 20 ns × 24 ビット)という短い時間とすることができます。この場合、最大更新レートは 5 μs に制限されます。

ステップ 2、ステップ 3、ステップ 4 に示すように、特定条件における出力電圧のセトリング時間は、AD5766/AD5767 のデータシートの仕様セクションに示されています。この場合(1/4 スケールから 3/4 スケールへのコード遷移)、出力電圧のセトリング時間は 0.5 LSB の許容差範囲で約 10 μs です。

以上から、圧縮処理を行わない場合の合計更新時間は、0.5 LSBの誤差範囲で約 10 μs と考えられます。

前述の更新時間は、更新時間の最適化と最短化のために使用可能な圧縮手法を適用して、短縮することができます。

最初の手法は並列化処理に基づくもので、この場合は、VOUTx電圧がまだセトリング中に(ステップ 4)新しいコードを転送します(ステップ 1)。

この手法は無損失精度として知られています。

AD5767 データシートの仕様に基づけば、セトリング時間条件(ステップ 2、ステップ 3、およびステップ 4)は 5 V ステップの遷移を指しています。DAC のスルー・レートが 1 V/μs の場合、DAC はコマンドの処理に約 5 μs を要し(ステップ 2)、VOUTxのセトリングにさらに約 5 μs を要します(ステップ 3 とステップ 4)。

なお、5 μs のセトリング時間は、1/2 スケール遷移に対する時間です。別の電圧遷移に DAC が要する時間は、以下のように計算できます。

1 µs × ΔVOUTx = セトリング時間

この場合、更新レートのタイミングは 5 V セットアップの場合で 10 μs −480 ns = 9.52 μs です。

この無損失精度手法の原理を図 5 に示します。この手法は、サイン波、鋸波、または三角波の信号生成によく見られる小さいステップ変化に適しています。

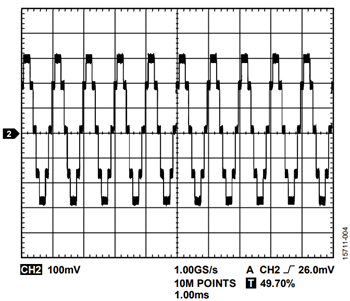

もう一つの圧縮手法はより積極的なもので、有効 DAC 分解能が低下する結果となります。この方法では、1 つ前のコマンドが処理される前に DAC を更新することを基本としています。この場合は、図 6 に示すように更新レートを 5 μs ~ 480 ns という高い値(デジタル処理コマンド時間)にすることができます。この方法は、矩形波生成のような大きいステップの遷移に適しています。

しかし、この手法には 3 つの短所があります。出力が完全にセトリングしないこと、アンプのゲイン帯域幅(GBW)を考慮しなければならないこと、そしてデジタル/アナログ・グリッチとデジタル・フィードスルーの影響を無視できないことです。

実際的な例

デジタル信号を生成するには、出力周波数、更新レート、チャンネル数など、いくつかの要素を考慮する必要があります。

1 つのチャンネルに 1 kHz のサイン波信号を生成する場合、1 周期あたり 10 サンプルと仮定すると、更新レートは 10,000 UPS です。出力信号を図 7 に示します。

20 kHz のサイン波信号を生成する場合、1 周期あたり 9 サンプルと仮定すると、更新レートは 180,000 UPS です。出力信号を図 8 に示します。

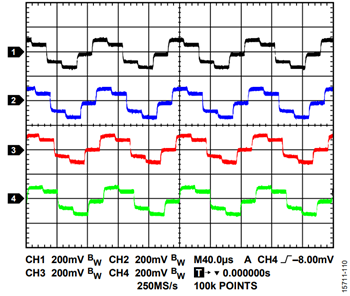

1 kHz のサイン波信号を生成する場合、1 周期あたり 25 サンプルで 4 チャンネルと仮定すると、更新レートは1 × 25 × 4 = 100,000 UPS です。出力信号を図 9 に示します。

周波数と 1 周期あたりのサンプル数(この場合は 5 サンプル)に関する性能の比較については、図 10 を参照してください。

図 9 と図 10 では異なるチャンネル間の位相が整合されていないので、すべてのサイン波が位相 0 で生成されています。各チャンネルは順番に更新されるので、位相遅延が生じます。

DAC 出力への影響

デジタル信号が生成される際には、隣接するチャンネルにクロストークが発生します。これは、図 11 に示すように、一般に高い方の周波数にある更新レート周波数で特に顕著です。