AN-1406: ADP5300/ADP5301/ADP5302/ADP5303 超低消費電力降圧 DC/DC レギュレータを使用した反転電源の設計

はじめに

バイポーラ・アンプ、光学モジュール、電荷結合素子(CCD)バイアスなどの特定のアプリケーションでは、通常、正の入力電圧から負の出力電圧を得る必要があります。パワー・マネージメント・システムの設計者には、パワー・マネージメントに関するこれらの課題を解決することのできる、多機能のスイッチング・コントローラとレギュレータが必要です。アナログ・デバイセズの ADP5300/ADP5301/ADP5302/ADP5303 超低消費電力降圧 DC/DC レギュレータは自己消費電流が極めて小さい、同期整流降圧機能を備えています。これらのレギュレータは、0.8V の範囲まで降圧が可能で、入力電源電圧範囲は 2.15 V ~ 6.50V、出力電流は最大 500 mA です。

ADP5300/ADP5301/ADP5302/ADP5303 は同期整流降圧アプリケーション向けのデバイスですが、多機能であるため、ソリューションのコスト、外付け部品、サイズなどを増やすことなく、正の入力電圧から負の出力電力を生成できる反転昇降圧トポロジーを実装することができます。

また、ADP5300/ADP5301/ ADP5302/ADP5303 は超低消費電力なので、ヒステリシス・モードでの軽負荷動作時に、高い効率を実現することができます。これらのデバイスは、低ノイズ性能と重負荷動作を実現するために、パルス幅変調(PWM)モードで使用できます。

このアプリケーション・ノートでは、同期整流反転昇降圧トポロジーにADP5300/ADP5301/ADP5302/ADP5303 を実装して、正の入力電圧から負の出力電圧を生成する方法を説明します。また、昇降圧トポロジーのいくつかの制約と、可能な解決策についても検討します。

昇降圧トポロジーの基本

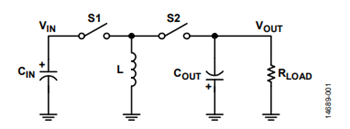

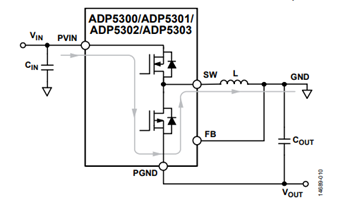

簡略化した昇降圧トポロジーを図 1 に示します。このトポロジーは、1 個のインダクタ、互いに逆位相で動作する 2 個のパワー・スイッチ、1 個の入力コンデンサ、および 1 個の出力コンデンサで構成されます。

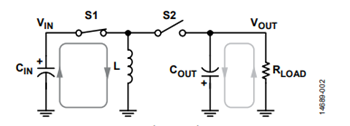

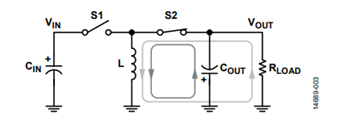

S1 がオンおよびオフした際に電流が流れる経路を、それぞれ図2 と図 3 に示します。スイッチ S1 がオンすると、スイッチ S2がオフになり、電流が入力コンデンサから流れ出してインダクタを充電し、一方で出力コンデンサが負荷にエネルギーを供給します。スイッチ S1 がオフすると、スイッチ S2 がオンになり、出力コンデンサを充電しながら電流がインダクタから負荷に流れます。

電流がグラウンドから VOUT に流れ、それによって出力電圧が負になることに注意してください。

式 1 では、定常状態での変換比が、インダクタのボルト秒バランスとコンデンサの電荷バランスの原理をこのトポロジーに適用することによって記述しています。式 2 は、PWM モードでの DC インダクタ電流 ILを規定しています。式 3 はインダクタのリップル電流 ΔIL の詳細を示しています。

ここで、

VOUT は出力電圧、

VIN は入力電圧、

D はデューティ・サイクル:

IOUT は出力電流、

L はインダクタ、

fSW はスイッチング周波数です。

ADP5300 ~ ADP5303 による昇降圧トポロジーの実装

ADP5300/ADP5301/ADP5302/ADP5303 同期整流降圧レギュレータを使って昇降圧トポロジーの反転電源アプリケーションを実装する際は、表 1 に示す設計上の制約を考慮してください。

| Voltage and Current | Restriction | Parameter | Value |

| VIN_MIN | > | VUVLO | 2.06 V |

| VIN_MAX + |VOUT| | < | VMAX | 6.50 V |

| IL_PEAK_HYS | < | ILIM_HYS | 265 mA |

| IL_PEAK_PWM | < | ILIM_PWM | 1000 mA |

昇降圧回路の最小入力電圧は、ADP5300/ADP5301/ADP5302/ADP5303 の UVLO 電圧より高くなければならず、レギュレータを動作させるには代表値が 2.06 Vでなければなりません。最大入力電圧と出力電圧の絶対値の合計は、レギュレータの最大動作入力電圧(代表値 6.50 V)より小さくなければなりません。回路を正常に動作させるために、ピーク・インダクタ電流が、レギュレータの最小電流制限トリガ・ポイント未満になるようにしてください。

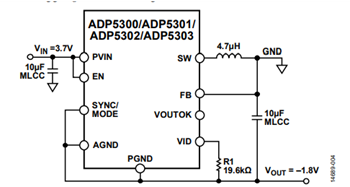

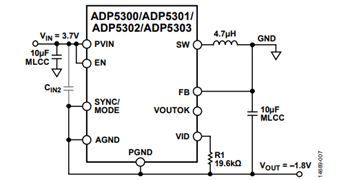

同期整流降圧レギュレータを昇降圧トポロジーに変換するには、インダクタと出力コンデンサを降圧トポロジーと同様に接続します。グラウンド電圧ポイントと出力電圧ポイントが逆になっていることに注意してください(図 4 参照)。出力電圧は、外付けの VID 抵抗によって設定された降圧トポロジーと同じです。抵抗値については表 2 を参照してください。

| VID Configuration | VOUT (V) | |

| Factory Option 0 | Factory Option 1 | |

| Short to AGND | −3.0 | −3.1 |

| Short to PVIN | −2.5 | −1.3 |

| RVID = 499 kΩ | −3.6 | Not applicable |

| RVID = 316 kΩ | −3.3 | Not applicable |

| RVID = 226 kΩ | −2.9 | −4.2 |

| RVID = 174 kΩ | −2.8 | −3.9 |

| RVID = 127 kΩ | −2.7 | −3.4 |

| RVID = 97.6 kΩ | −2.6 | −3.2 |

| RVID = 76.8 kΩ | −2.4 | −1.9 |

| RVID = 56.2 kΩ | −2.3 | −1.7 |

| RVID = 43 kΩ | −2.2 | −1.6 |

| RVID = 32.4 kΩ | −2.1 | −1.4 |

| RVID = 25.5 kΩ | −2.0 | −1.1 |

| RVID = 19.6 kΩ | −1.8 | −1.0 |

| RVID = 15 kΩ | −1.5 | −0.9 |

| RVID = 11.8 kΩ | −1.2 | −0.8 |

インダクタの選択

動作周波数、入力電圧、およびインダクタのリップル電流がインダクタ値を決定します。ピーク・インダクタ電流を考慮して、降圧トポロジーに使用するインダクタより大きいインダクタの使用を推奨します。ただし、インダクタはループの安定性に影響するので、大きくし過ぎないようにしなければなりません。電流制限が早く生じ過ぎないようにするために、ピーク・インダクタ電流が、最小ピーク電流制限閾値(PWM モードのILIM_PWM とヒステリシス・モードの ILIM_HYS)を超えないようにしてください。

ピーク・インダクタ電流は、平均インダクタ電流と、ピーク toピーク・インダクタ・リップル電流の半分を加えることによって計算します。

ここで、

IAVG は平均インダクタ電流です。

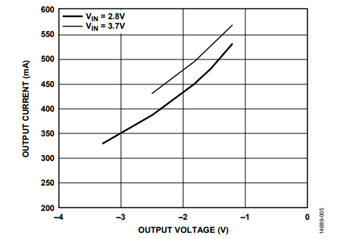

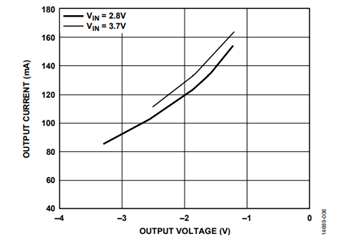

インダクタを 4.7 μH、スイッチング周波数を 2 MHz と仮定して、ピーク・インダクタ電流を考慮に入れた場合、PWM モードとヒステリシス・モードでの一般的な入力電圧に対する反転昇降圧トポロジーでの ADP5300/ADP5301/ADP5302/ADP5303 の負荷電流能力を、図 5 と図 6 に示します。

インダクタの飽和電流は、ピーク・インダクタ電流よりも大きくする必要があります。急峻な飽和特性を持つフェライト・コア・インダクタの場合、インダクタの飽和電流定格がスイッチの電流制限の閾値より大きいものにして、通常動作時にインダクタが飽和するのを防止する必要があります。

出力コンデンサの選択

反転昇降圧トポロジーでは、出力電流が不連続であることに注意してください。出力コンデンサは、インダクタに蓄えられるエネルギーが増大するオンの時に、負荷にエネルギーを供給します。オフの時は、インダクタが負荷と出力コンデンサの両方にエネルギーを供給します。

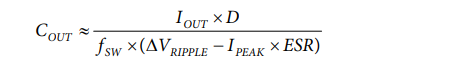

出力コンデンサの容量に関する大きな問題は、出力コンデンサの 2 つのパラメータによって決まる許容出力電圧リップルです。そのパラメータの 1 つが出力コンデンサの容量で、もう 1つが等価直列抵抗(ESR)です。以下の式は、出力電圧リップルを許容範囲内に維持するために必要な最小容量(COUT)の予想値を与えます。

ここで、

ΔVRIPPLE は許容出力リップル電圧、

ESR は出力コンデンサの合計等価直列抵抗、

IPEAK はインダクタのピーク電流です。

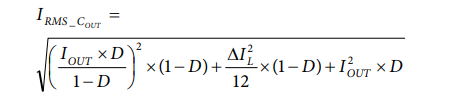

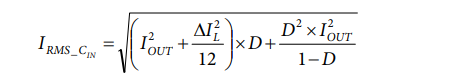

出力リップル電圧をできるだけ小さくするには、ESR 値が非常に低い積層セラミック・コンデンサ(MLCC)を使用することを推奨します。選択した出力コンデンサの RMS 定格電流は、次式を使用して計算される値より大きくする必要があります。

入力コンデンサの選択

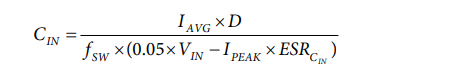

反転昇降圧トポロジーでは、入力電流も不連続です。電源オン時の入力コンデンサのエネルギー消耗による入力電圧の変動を入力電圧の 5 % 未満と仮定すると、この要求を満たすために必要な最小入力容量(CIN)は以下の式で計算できます。

ここで、

IAVG は平均インダクタ電流、

ESRCIN は入力コンデンサの等価直列抵抗です。

少なくとも 10 μF のセラミック・コンデンサを1 個使用することが推奨されますが、このコンデンサは PVIN ピンのできるだけ近くに取り付ける必要があります。選択した入力コンデンサの RMS 電流は、次式で求められる値より大きくする必要があります。

入力電圧レールの容量の大部分はシステム・グラウンドを基準にしていますが、図7 に示すように、入力電圧とADP5300/ADP5301/ADP5302/ADP5303 の PGND ピンの間に入力デカップリング・コンデンサを追加することで、出力電圧リップルを減らして過渡応答を改善することができます。

イネーブル信号のレベル・シフト

ADP5300/ADP5301/ADP5302/ADP5303 には、レギュレータをイネーブル/ディスエーブルするためのEN ピンがあります。ただし、反転昇降圧アプリケーションでは、IC はシステム・グラウンドではなく負の出力電圧を基準にしています。レギュレータをディスエーブルするつもりでシステム・グラウンドにENピンを接続しても、ADP5300/ADP5301/ADP5302/ADP5303 はスイッチングを続けます。

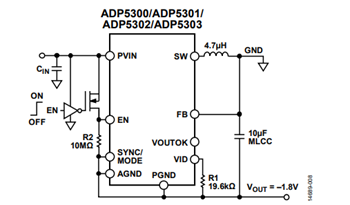

このイネーブル信号用に考えられるソリューションは、図8 に示すように、超低消費電力インバータ、P 型 MOSFET(金属酸化膜半導体電界効果トランジスタ)、および適切に接続した抵抗によって、EN レベル・シフト回路を形成することです。

レベル・シフト回路を使用すると、ADP5300/ADP5301/ADP5302/ADP5303 の高精度イネーブル機能が失われることに注意してください。イネーブル機能が必要ない場合は、図8 に示すように、単純に EN ピンを入力電圧に接続します。

スタートアップ前の VOUT のランプアップの低減

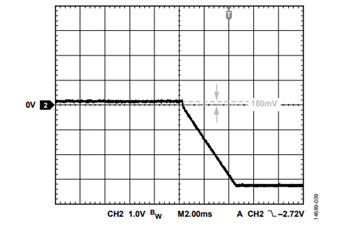

同期整流降圧レギュレータを使って反転昇降圧トポロジーを実現する場合の一般的な問題の1 つは、出力電圧がランプアップして、レギュレータの動作開始前に正の電圧になる可能性があることです(図9 参照)。

この正の出力電圧のランプアップは、図10 に示すように、レギュレータのシャットダウン電流が IC の PGND ピンからローサイド MOSFET のボディ・ダイオードを通り、システム・グラウンドへ流れることによって発生します。ADP5300/ADP5301/ADP5302/ADP5303 のシャットダウン電流は非常に小さいので、ローサイド MOSFET のボディ・ダイオードは、VOUT を代表値が約 180 mV の順方向電圧レベルにクランプします。

VOUT はレギュレータの PGND ピンに接続されますが、このピンは実際に UVLO などの内部回路の基準点なので、PGND ピンに現れる正電圧は UVLO 閾値電圧を下げます。入力電圧がレギュレータの UVLO 閾値電圧(代表値 2.06 V)に非常に近い場合は、レギュレータがスタートアップできない可能性があります。

このアプリケーション・ノートに示したように、反転昇降圧トポロジーを実現するために同期整流降圧レギュレータを使用する場合は、ほぼすべての同期整流降圧レギュレータでこの問題が発生します。この問題を完全になくすことは非常に困難です。

まとめ

反転昇降圧トポロジーにADP5300/ADP5301/ADP5302/ADP5303を実装することで、降圧トポロジーの実装と同程度にシンプルで安価、かつサイズの小さいソリューションを実現することができます。このアプリケーション・ノートは、イネーブル/ディスエーブル機能が必要な場合にシンプルな EN レベル・シフト回路を提供するとともに、同期整流降圧レギュレータを反転昇降圧トポロジーに適用する際に、VOUT が正電圧にランプアップすることに伴う問題について説明しています。

このアプリケーション・ノートの設計式や推奨事項に従うことよって、システム設計者は、すべての要件を満たす信頼性の高い設計を実現することができます。