資料ライブラリ

AN-1349: ADM2582E/ADM2587E RS-485/RS-422 トランシーバの放射エミッションを最小限に抑えるためのPCB 実装ガイドライン

はじめに

ADM2582E/ADM2587E は、全機能を集積した信号/電源絶縁型RS-485/RS-422 トランシーバです。信号の絶縁には、アナログ・デバイセズのiCoupler®デジタル・アイソレーション技術が採用されています。またADM2582E/ADM2587E には、アナログ・デバイセズのisoPower®技術を採用した高電圧絶縁型DC/DC 電源も内蔵されているため、外部のDC/DC 絶縁ブロックは不要です。どの絶縁型電源においても主なコンポーネントは電源トランスです。isoPower 内蔵トランスは、180MHz~400MHz の範囲のスイッチング周波数で動作します。絶縁は、物理的な絶縁間隙によって分離された分割リファレンス・プレーンによってプリント回路基板(PCB)上に実装されています。PCB レイアウトに絶縁間隙があることにより、不要な電流ループが放射されます。PCB のレイアウトを作成する場合、電磁(EM)抑制に関する基本的なガイドラインおよび概念に従うことで放射エミッションを軽減できます。

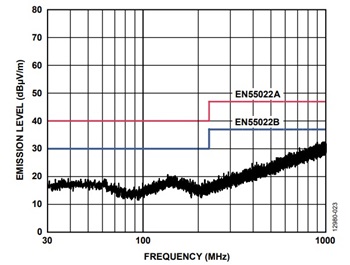

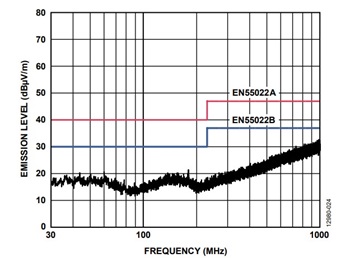

産業用アプリケーションおよび計測器用アプリケーションでは、放射エミッションに関する複数の規格が存在します。優れたPCB 設計およびレイアウトを採用することで、ADM2582E/ADM2587E デバイスは産業環境で一般的に使用されているEN55022/CISPR22 クラスA(FCC クラスA)放射規格を容易に満たすことができます。注意深く設計することで、これらの製品は非シールド環境でEN55022/CISPR22 クラスB(FCCクラスB)規格を満たすこともできます。

このアプリケーション・ノートでは、放射エミッションに関するこれらの規格を満たすため、特定のレイアウト・オプションおよび使用するコンポーネントについて説明します。また、EN55022/CISPR22 クラスA ( FCC クラスA ) およびEN55022/CISPR22 クラスB(FCC クラスB)の両方の放射規格に適合する、特定のPCB のレイアウトの詳細と公認の10m 半無響室での測定結果についても説明します。

推奨事項

PCB の推奨事項の概要

EN55022/CISPR22 クラスA(FCC クラスA)等級に適合させるには、次のガイドラインに従うことを推奨します。

- PCB のデカップリングが良好であることを確認します(ADM2582E/ADM2587E データシートの推奨デカップリングに従う)。

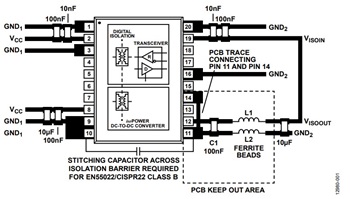

- PCB パターン接続部と次のIC ピンの間にフェライト・ビーズを接続します:VISOOUT(12 番ピン)およびGND2(11 番ピンおよび14 番ピン)。

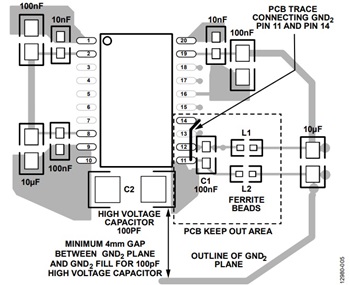

- VISOOUT ピンは電源プレーンに接続しないでください(PCBパターンを使用してVISOOUTをVISOIN に接続します)。図1 に示すように、フェライト・ビーズを介してVISOIN (19 番ピン)をVISOOUT(12 番ピン)に接続します。

- 図1 に示すように、GND2(16 番ピンおよび20 番ピン)を、L2 フェライトの外側(バス側)でGND2(11 番ピン)に接続します。

- PCB レイアウトのL1 フェライト・ビーズおよびL2 フェライト・ビーズの周囲に、GND2 プレーン用の禁止領域を設けます。禁止領域とは、フェライト・ビーズの下のいずれのレイヤにもGND2 フィルまたはメタル・フィルを配置してはならないことを意味します。その理由は、寄生容量があるとフェライト・ビーズのフィルタリング効果が減少してしまうため、PCB パターンとPCB のレイヤの間での寄生容量を低減することにあります。

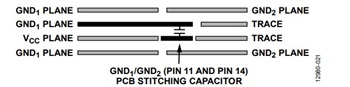

より厳格なEN55022/CISPR22 クラスB(FCC クラスB)放射規格を満たす必要があるアプリケーションの場合、前述の推奨事項に加え、絶縁バリアをまたぐスティッチング容量による抑制技法を実施する必要があります。次の2 つのどちらの方法でもスティッチング・コンデンサを作成できます。

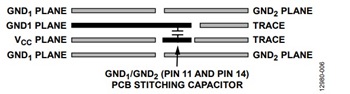

- PCB プレーン内部のレイヤを使用してGND1 とピンGND2 ピン(11 番ピンと14 番ピン)の間のスティッチング・コンデンサを組み込みます。スティッチング・コンデンサはGND2ピン(16 番ピンおよび20 番ピン)には接続しないでください。

- GND1 ピン(9 番ピンおよび10 番ピン)とGND2 ピン(11 番ピンと14 番ピン)の間に高電圧のディスクリート・コンデンサを接続します。

放射抑制に関する推奨事項

放射エミッションを軽減するには、PCB の設計/レイアウト作成時にいくつかの基本的なガイドラインに従うことが重要です。短時間に大電流がスイッチングされると電磁放射が発生し、大きなdi/dt ノイズが発生します。放射エミッションのレベルは、電流パスのループ面積に依存します。これは、電流ループ面積が大きいと、放射エミッションが強くなるためです。これらのガイドラインにより、放射エミッションを発生源で制御し、電流パスのループ面積を最小限に抑えることができます。

次の操作により、isoPower 技術での放射レベルをクラスA の制限値未満に低減できます。

- VCC 電源の良好なデカップリング。

- 特定のIC ピンとPCB パターン間のインピーダンスの増加。

- PCB パターンでのVISOIN とVISOOUT の接続(プレーン接続なし)。

EN55022/CISPR22 クラスB(FCC クラスB)等級に適合させるには、追加の抑制方法が必要になります。つまり、GND1 とGND2 間の絶縁バリアをまたぐ高周波電流に対するインピーダンスを低減してください。

放射の制限値をクリアするための余裕を設けるには、GND2 プレーン面積を最小限に抑える必要があります。

電源/信号ケーブルからの放射の制御とシャーシのシールド技法については、このアプリケーション・ノートでは取り上げません。

PCB のガイドライン

VCC デカップリング

デカップリング・コンデンサには、次の2 つの主な機能があります。

- デカップリング・コンデンサは、電荷蓄積デバイスとして使用します。IC が状態を切り替える際に追加の電流が必要になったときに、局所的なデカップリング・コンデンサが低インダクタンス経路を通じてこの電流を供給します。

- デカップリング・コンデンサは、PCB プレーンに混入するノイズを軽減します。これにより、システム内の高周波ノイズが抑制されます。混入するノイズは、十分な電流が供給されるまでVCC ピンの電源電圧が一時的に低くなったときに発生します。

ADM2582E/ADM2587E は、isoPower 技術により、数100mAの範囲の大電流を180MHz および400MHz の周波数でスイッチングします。VCC ピン(8 番ピン)に接続された10μF のコンデンサは、大量の蓄積電荷をPCB 上で局所的に提供します。これらのコンデンサは、180MHz と400MHz で非常に小さい等価直列抵抗(ESR)および小さい等価直列インダクタンス(ESL)を達成していることが重要です。

VCC ピンとGND1 ピン間のデカップリングが不十分な場合、これらの高周波スイッチング電流はコンデンサから局所的に供給されるのではなく、PCB への電源供給システムから供給されます。ADM2582E/ADM2587E への電源供給システムがIC の近くにない場合、高周波電流の流れるループ面積が増大します。ループ面積が増大すると、放射レベルが増大します。

PCB レイアウトに関しては、次の配置が非常に重要です。

- デカップリング・コンデンサを電源ピンとGNDX ピンのできるだけ近くに配置して、インダクタンスと電流ループ面積を最小限に抑えます。

- VCC 電源ピンとPCB のVCC 電源プレーンとの間のインピーダンス経路を最小限に抑えます。

- IC のGND1 ピンとPCBのGND1 プレーンとの間のインピーダンス経路を最小限に抑えます。

特定のIC ピンとPCB パターン接続間のインピーダンスの増加

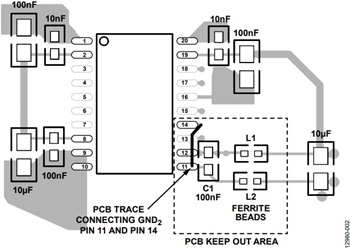

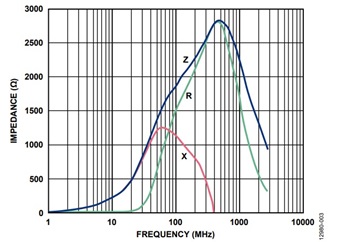

特定のIC ピンとPCBパターン接続間の高周波電流に対するインピーダンスを大きくすると、電磁放射のレベルが最小限になります。このEM 抑制方法は、放射される信号を信号源で制御し、ループ面積を最小限に抑えます。これは、表面実装フェライト・ビーズをVISOOUT(12 番ピン)およびGND2(11 番ピンと14 番ピン)と直列接続することで実現できます(図2 を参照)。フェライト・ビーズのインピーダンスは、図3 に示すように、100MHz~1GHz の周波数範囲で2kΩ よりも大きくなるよう選択します。この図において、Z はインピーダンス、R は抵抗、X はフェライト・ビーズのリアクタンスです。測定データは、表1に示すフェライト・ビーズを使用して収集しました。

| Manufacturer | Device No. |

|---|---|

| Taiyo Yuden | BKH1005LM182-T |

| Murata Electronics | BLM15HD182SN1 |

GND1 とGND2 間の絶縁バリアをまたぐ高周波電流に対するインピーダンスの低減

EN55022/CISPR22 クラスB(FCC クラスB)等級に適合させるには、絶縁バリアをまたぐスティッチング容量による抑制技法を使用して、更に放射レベルを低減させる必要があります。

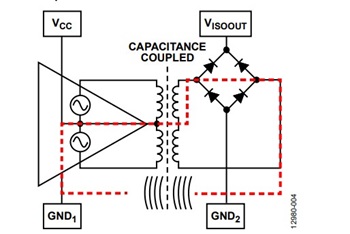

PCB 上に絶縁間隙が形成されることにより、不要なグラウンド電流ループが生じて放射エミッションが増加することがあります。絶縁された電源を生成するため、トランスによって絶縁バリアをまたぐ電流がスイッチングされます。理論的には、1 次側のトランス・ドライバの差動電流のみが絶縁バリアをまたいで磁気的に結合されます。ただし、トランスに固有の問題として、寄生電流も絶縁バリアをまたいで容量性の結合を形成します(図4 を参照)。これらの寄生電流が2 次側にある場合、1 次側の発生源に戻る経路を探します。これらの電流が絶縁間隙を通過するための物理的な接続はありません。これらの高周波電流は、2 次側のVISOOUT ピンとGND2 ピンでコモンモード電流になります。これらの高周波電流が絶縁バリアをまたいで戻れないことにより、放射エミッションが発生します。

図4 に示す電流の流れを分析すると、絶縁バリアにより2 次側から1 次側に戻る物理的なリターン経路が存在しないので、放射源となるダイポール・アンテナが生成されます。高周波コモンモード電流用に低インピーダンスのリターン経路を提供することで、ダイポールの放射レベルを低減できます。

絶縁バリアをまたぐスティッチング・コンデンサは、システムで求められる高電圧絶縁を維持すると同時に、高周波コモンモード電流に必要な低インピーダンスのリターン経路を提供します。

スティッチング・コンデンサの実装

次の方法を使用して、PCB の絶縁間隙をまたぐスティッチング・コンデンサを実装できます。

- 高電圧、安全定格のディスクリート・コンデンサ

- 内蔵PCB スティッチング容量

高電圧、安全定格のディスクリート・コンデンサ

スティッチング容量は、絶縁バリアをまたぐセラミック・コンデンサを使用して実装できます。

可能な場合は、表面実装型の高電圧コンデンサ・ボディを使用することを推奨します。これは、ディスクリートのスルー・ホール・コンデンサと比較して、表面実装コンポーネントのほうがリード線のインダクタンスが小さいためです。ADM2587E(3.3V および5.0V で駆動)およびADM2582E(5.0V で駆動)は、EN55022B の認証を取得するためにディスクリート高電圧コンデンサを使用しています。

PCB 設計を行う場合は、図5 に示したPCB レイアウトに従ってください。

- GND2(14 番ピン)を、C1 の100nF コンデンサの内側(デバイス側)でGND2(11 番ピン)に接続します。

- C1 コンデンサをL2 フェライト・ビーズおよびL3 フェライト・ビーズのデバイス側でVISOOUT(12 番ピン)とGND2(11 番ピン)の間に接続します。

- 図5 に示すように、GND2(16 番ピン)を、L2 フェライト・ビーズの外側(バス側)でGND2(11 番ピン)に接続します。

- PCB レイアウトのL1 フェライト・ビーズおよびL2 フェライト・ビーズの周囲に、GND2 プレーン用の禁止領域を設けます。禁止領域とは、L1 およびL2 のフェライト・ビーズの下のいずれのレイヤにもGND2 フィルを配置してはならないことを意味します。

- GND2 プレーン・フィルとC2 高電圧ディスクリート・コンデンサ・パッド用GND2 フィルの間には最低でも4mm の間隙を設けます。

沿面距離、間隙、および耐電圧が確保されたコンデンサは、主要なコンデンサ・メーカーから入手できます(表2 を参照)。

| Parameter | Value |

|---|---|

| Manufacturer | TDK Corporation |

| Device Number | C4532C0G3F101K160KA |

| Description | Capacitor, ceramic, 100 pF, 3 kV |

| Body Size | 1812 |

内蔵PCB スティッチング容量

マルチレイヤPCB では、PCB レイヤを使用して内蔵スティッチング・コンデンサ構造を作成できます。内蔵PCB コンデンサは、PCB の2 つの金属プレーンが互いに重なり合い、誘電体で分離されている場合に作成されます。内蔵スティッチング・コンデンサは、1 次レイヤおよび2 次レイヤからPCB 表面の沿面距離に使用する領域まで内部リファレンス・プレーンを延ばすことで形成されます。絶縁バリアをまたぐように内部レイヤを重ねることで、絶縁バリアをまたぐコンデンサが形成されます。このコンデンサは、絶縁バリアをまたぐ、高周波コモンモード・ノイズ電流のリターン経路を提供します。内部レイヤを使用してコンデンサを形成します。表面レイヤには沿面距離および間隙を最小限にするという要件があるため、表面レイヤを使用するのは実用的ではありません。内蔵スティッチング・コンデンサのレイアウトと実装については、AN-0971 で詳述されています。

内蔵スティッチング・コンデンサは、次の2 つのいずれかの構造を使用して実装できます。

- 重複スティッチング構造

- フローティング容量構造

重複スティッチング構造

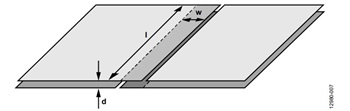

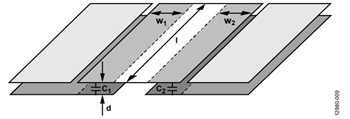

重複スティッチング構造は、1 次リファレンス・プレーンと2 次プレーン間の絶縁間隙領域をまたぐようにPCB リファレンス・プレーンの2 つの内部レイヤを延ばすという概念を使用しています。容量は、アイソレータの下の間隙に形成されます。沿面距離と間隙を確保するため、上のレイヤと下のレイヤで空間を確保する必要があります。内部金属リファレンス・プレーンはPCB の誘電体(通常はFR4)で分離され、コンデンサ構造が形成されます。誘電体で分離された金属の重複面積を使用して、内蔵スティッチング構造の容量を計算します(図6 を参照)。

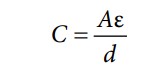

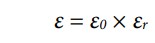

容量結合は、平行板コンデンサの次の基本的な関係を使用して計算します。

ここで、

C は容量、

A は面積、

ε は誘電率、

d はレイヤ間の距離です。

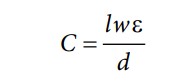

重複スティッチング・コンデンサ構造を備えたPCB の場合、次の式を使用して容量結合を算出します。

ここで、

ε = ε0 × εr、

ε0 は自由空間の誘電率で、8.854 × 10−12F/m、

εr はPCB 絶縁材料の比誘電率、

w、d、l は1 次リファレンス・プレーンと2 次リファレンス・プレーンの重複部分の寸法です(図7 を参照)。

2 つのリファレンス・プレーン間の誘電体FR4 材料の厚みにより、システムの高電圧性能が決定されます。これらの間隙は結合点と呼ばれ、絶縁を実現します。このアーキテクチャでは、結合点は1 箇所だけで、1 次リファレンス・プレーンと2 次リファレンス・プレーンの間のレイヤ数はFR4 の1 レイヤだけです。誘電体の厚みを増やして、高電圧性能を向上することができます。ただし、誘電体の厚みを増やすと、内部リファレンス・プレーン間の間隔が増えるため、得られる結合容量が低下します。例えば、特定の面積の2 つの内部リファレンス・プレーン間の誘電体の厚さを2 倍にすると、リファレンス・プレーン間の結合容量は1/2 になります。

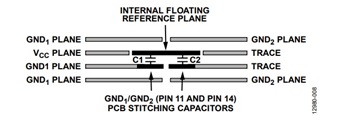

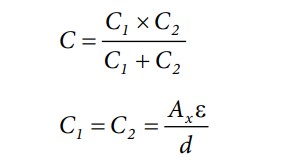

フローティング・スティッチング構造

高電圧性能に関する要件が厳格なアプリケーションでは、フローティング・スティッチング・コンデンサのアーキテクチャを使用します。フローティング・アーキテクチャでは、フローティング状態の内部金属プレーンの概念を使用して、高周波コモンモード電流を2 次リファレンス・プレーンから絶縁間隙をまたいで1 次リファレンス・プレーンに結合します。このアーキテクチャでは、並列接続された2 つのコンデンサを形成します(図8 を参照)。

重複スティッチング構造と同様、間隙をまたぐ高電圧絶縁を提供するのは誘電体です。高電圧性能の観点から重複構造と比較した場合、フローティング・スティッチング構造には2 つの絶縁間隙によるメリットがあります。1 つ目のメリットは、2 次プレーンと内部フローティング・リファレンス・プレーンの間の誘電体の厚さによる絶縁間隙です。2 つ目のメリットは、内部フローティング・リファレンス・プレーンと1 次リファレンス・プレーンの間の誘電体の厚さによる絶縁間隙です。これらの2 つの間隙が存在することは、高電圧絶縁レベルを増加する必要のあるシステムにおいて強化された絶縁バリアを形成する場合に有利です。

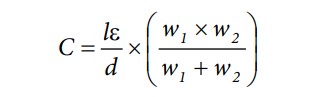

図8 の構造の容量性結合は、平行板コンデンサの次の基本的な関係を使用して計算します。

ここで、

C は合計スティッチング容量、

AX は各リファレンス・プレーンに対するスティッチング容量の重複面積、

d はPCB の絶縁層の厚さです。

ここで、

ε0 は自由空間の誘電率で、8.854 × 10−12F/m、

εr はPCB 絶縁材料の比誘電率です。

ここで、w1、w2、d、l はフローティング・プレーンと1 次および2 次リファレンス・プレーンの重複部分の寸法です。(図9 を参照)。

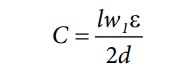

w1 = w2 の場合、この数式は次のように簡素化されます。

コンデンサが並列実装されていることで、単位面積あたりの実効容量は重複コンデンサ構成の1/2 になります。

EN55022 に適合するADM2582E/ADM2587E の放射レベル測定値

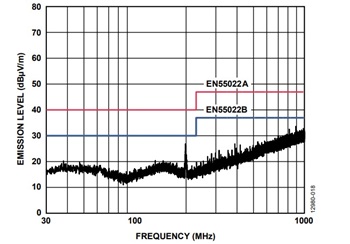

このセクションでは、公認の10m 半無響室で得られた放射レベル測定値について説明します。ここで説明する放射レベル測定値は、次の等級に適合させるための特定のPCB レイアウトとEM 抑制技法を基準にしています。

- EN55022 クラスA 等級

- EN55022 クラスB 等級

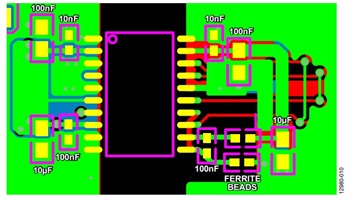

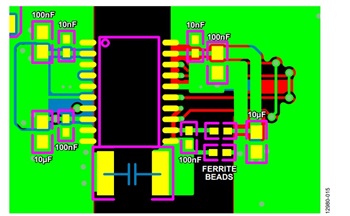

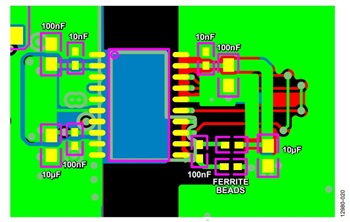

EN55022/CISPR22 クラスA等級に適合させるには、図10 のペリフェラル・コンポーネントのレイアウトの詳細を参照してください。

EN55022/CISPR22 クラスB等級に適合させる場合は、EN55022Aに適合させるための推奨レイアウトにスティッチング容量を追加する必要があります。

EN55022 クラスA 等級

EN55022 クラスA 等級に適合させるのに使用したEMI 抑制技法/コンポーネントは次のとおりです。

- すべてのVCC ピンおよびVISO ピンに適切なデカップリング・コンデンサを接続。

- VISOOUT(12 番ピン)およびGND2(11 番ピンおよび14 番ピン)にフェライト・ビーズを接続。

最適化されたコンポーネント配置とPCB レイアウトについては、図10 を参照してください。

特定の場所にデカップリング・コンデンサを接続し、VISOOUT ピンおよびGND2 ピンにフェライト・ビーズを接続することが重要です。11 番ピンと14 番ピンのGND2 接続は、フェライト・ビーズに接続される前にPCB パターンによって結合されています。放射エミッションを低減するには、これらの2 つのGND2ピンが、フェライト・ビーズを介した上で、PCB のGND2(16 番ピン)とGND2(20 番ピン)に接続することが重要です。

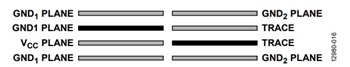

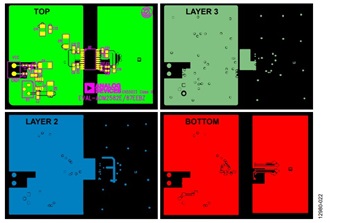

使用したPCB は、図11 に示すように、4 レイヤ構成です。

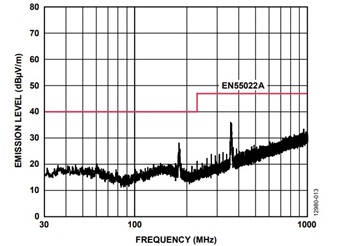

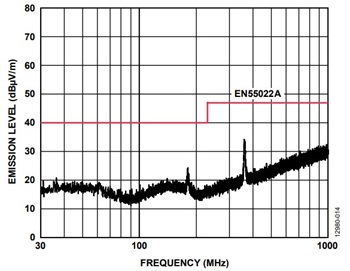

ADM2582E とADM2587E はどちらもVCC = 3.3V で駆動し、最大データレート(それぞれ16Mbps および500kbps)でデータをスイッチングしました。デバイスは半2 重モードで接続し、ピンA をピンY、ピンB をピンZ に接続しました。外部のコンプライアンス・テスト施設内にある公認の10m 半無響室で、EN55022 規格に従って放射レベルを測定しました。

図12 にADM2582E の放射エミッションの測定値、図13 にADM2587E の放射エミッションの測定値を示します。

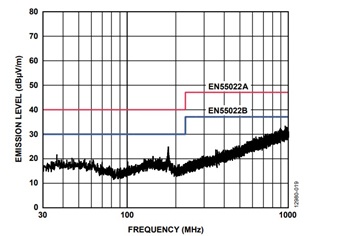

EN55022 クラスB 等級

EN55022 クラスA 等級のセクションで説明した、EN55022 クラスA 等級に適合させるのに必要なEMI 抑制技法/コンポーネントは、EN55022 クラスB 等級に適合させる場合にも実行/実装する必要があります。ただし、EN55022B に適合させるには、絶縁バリアをまたぐスティッチング容量による追加の抑制技法も必要です。次の2 つのスティッチング方法について説明します。

- 高電圧ディスクリート・スティッチング・コンデンサ

- 重複スティッチング・コンデンサ

高電圧ディスクリート・スティッチング・コンデンサ

CISPR22/EN55022B 等級に適合させるには、デカップリング・コンデンサ(高電圧ディスクリート・コンデンサ)を特定の場所に配置し、VISOOUT ピンとGND2 ピンにフェライトを接続する必要があります。高電圧ディスクリート・コンデンサの使用により、ADM2587E は3.3V および5.0V 電源で駆動した場合、ADM2582E は5.0V 電源で駆動した場合に、放射制限値をクリアすることが実証されています。ADM2582E を3.3V で駆動し、16Mbps の最大データレートで動作させてテストした場合は、高電圧ディスクリート・コンデンサではクラスB 等級への適合に十分ではありませんでした。

ペリフェラル・コンポーネントのレイアウトの詳細については、図14 を参照してください。使用したPCB は、図15 に示すように、4 レイヤ構成です。PCBスティッチング容量は、高電圧ディスクリート・コンデンサで実装しました。最適な性能を実現するため、コンデンサをGND2 ピン(11 番ピン)に直接接続することが重要です(デバイスのピンとフェライトの間)。ここに記載されている測定結果は、100pF、1812 ボディ・サイズのコンデンサで得られたものです。このコンデンサの電圧定格は3kV で、TDK Corporation 製(C4532C0G3F101K160KA)です。

外部のコンプライアンス・テスト施設内にある公認の10m 半無響室で、EN55022 規格に従って放射レベルの測定結果を記録しました。図16 にADM2582E の放射エミッションの測定値、図17にADM2587E の放射エミッションの測定値を示します。

重複スティッチング・コンデンサ

最高の性能を発揮するには、特定の場所にデカップリング・コンデンサを接続し、VISOOUT ピンおよびGND2 ピンにフェライト・ビーズを接続することが重要です。ペリフェラル・コンポーネントのレイアウトの詳細については、図18 を参照してください。使用したPCB は、図19 に示すように、4 レイヤ構成です。PCB スティッチング容量の例は、重複構造を使用して実装しました。第2 レイヤ(GND1 に接続)の内部金属プレーンを延長し、第3 レイヤ(VISOOUT に接続)の金属領域を延長して、第2 レイヤと第3 レイヤの間に金属が重複する領域を設けました。第2 レイヤおよび第3 レイヤのこれらの2 つのリファレンス・プレーン間の重複領域( 図19 を参照) の面積は、ADM2582E/ADM2587E パッケージのサイズです。これら2 つの金属リファレンス・プレーン間の重複領域はFR4 材料で分離されており、第2 レイヤと第3 レイヤの間のFR4 誘電体による間隔が0.1016mm の場合、容量は約35pF です。高い絶縁性能を維持できるように、この例よりもレイヤの間隔を増やすには、必要に応じて重複面積も増やす必要があります。

外部のコンプライアンス・テスト施設内にある公認の10m 半無響室で、EN55022 規格に従って放射レベルの測定結果を記録しました。ADM2582E とADM2587E はどちらも3.3V で駆動し、最大データレート(それぞれ16Mbps および500kbps)でデータをスイッチングしました。図21 にADM2582Eの放射エミッションの測定値、図22 にADM2587Eの放射エミッションの測定値を示します。

放射エミッションの測定結果を備えたユーザ向け評価用PCB

EVAL-ADM2587E およびEVAL-ADM2582E の製品ページで、評価用PCB を購入できます。外部のコンプライアンス・テスト施設内にある公認の10m 半無響室で、EN55022 規格に従って放射レベルの測定結果を記録しました。ADM2582E とADM2587E はどちらも3.3V および5.0V で駆動し、ADM2582E およびADM2587E のTxD ピンにおいて最大データレート(それぞれ16Mbps および500kbps)でデータをスイッチングしました。

以下に示す、2 レイヤPCB 構成と4 レイヤPCB 構成の評価用PCB が入手可能です。

- 2 レイヤ・ボード:EVAL-ADM2582EEMIZ およびEVAL-ADM2587EEMIZ

- 4 レイヤ・ボード:EVAL-ADM2582EEBZ またはEVAL-ADM2587EEBZ

これらの評価用ボードに対するEN55022 認証に関する資料は、ご要望に応じて、アナログ・デバイセズ・セントラル・アプリケーションまたは、最寄りのアナログ・デバイセズのフィールド・アプリケーション・エンジニアから入手できます(テクニカル・サポートのページを参照)。

2 レイヤのユーザ評価用PCB のエミッション結果

2 レイヤ・ボード用のEVAL-ADM2582EEMIZ/EVAL-ADM2587EEMIZユーザ・ガイドに基づくEN55022 放射エミッション・テスト結果の概要を表3 に示します。

| Device | High Voltage Capacitor | Supply | Data Rate | Load | EM55022 Class | Pass Margin (dBμV) |

|---|---|---|---|---|---|---|

| ADM2582E | No | 3.3 V | 16 Mbps | 54 Ω | A | 1.2 |

| ADM2582E | No | 5.0 V | 16 Mbps | 54 Ω | A | 4.7 |

| ADM2582E | Yes | 3.3 V | 16 Mbps | 54 Ω | B | 3.7 |

| ADM2582E | Yes | 5.0 V | 16 Mbps | 54 Ω | A | 7.5 |

| ADM2587E | No | 3.3 V | 500 kbps | 54 Ω | A | 3.9 |

| ADM2587E | No | 5.0 V | 500 kbps | 54 Ω | A | 4 |

4 レイヤのユーザ評価用PCB のエミッション結果

表4 のEN55022 放射エミッション・テスト結果は、このアプリケーション・ノートのPCB ガイドラインに従い、GND1 とGND2 の間に内蔵PCB スティッチング・コンデンサを実装して得られたものです。4 レイヤPCB の設計およびレイアウトの詳細については、EVAL-ADM2582EEBZ/EVAL-ADM2587EEBZユーザ・ガイドを参照してください。

| Device | Embedded Stitching Capacitor | Supply | Data Rate | Load | EM55022 Class | Pass Margin (dBμV) |

|---|---|---|---|---|---|---|

| ADM2582E | Yes | 3.3 V | 16 Mbps | 54 Ω | B | 4.7 |

| ADM2582E | Yes | 5.0 V | 16 Mbps | 54 Ω | B | 6.5 |

| ADM2587E | Yes | 3.3 V | 500 kbps | 54 Ω | B | 5.5 |

| ADM2587E | Yes | 5.0 V | 500 kbps | 54 Ω | B | 8.5 |

参考資料

AN-0971 アプリケーション・ノート、isoPower デバイスでのEMI 放射制御についての推奨事項。Analog Devices, Inc.

Archambeault, Bruce R. and James Drewniak. PCB Design for Real-World EMI Control. Boston: Kluwer Academic Publishers, 2002