AN-1084: AD7190、AD7192、AD7193、AD7194、AD7195 でのチャンネル切り替え手順

概要

Σ-Δ ADC は一般に、出力データレートで仕様が規定されます。出力データレートとは、1 つのチャンネルが選択されてADC が連続的に変換を行うときの変換を行うレートを意味します。データ・アクイジション・システムのようなマルチチャンネル・アプリケーションでは、複数のチャンネルから変換結果が読出されます。すなわち、各チャンネルが順次選択されて、そのチャンネルに対して変換が行われます。このようなアプリケーションでは、変換が実行されるレートは1 チャンネルのシステムの場合と異なることがあります。このアプリケーション・ノートでは、AD7190、AD7192、AD7193、AD7194、AD7195 (以後AD719x と呼びます)で使用されるスイッチング手順について説明します。

マルチチャンネル・システム

PLC システムのようなアプリケーションでは、センサーからの多数の信号または出力を処理するため複数の入力チャンネルが必要とされます。AD719x はPGA と広範囲なプログラマブルな出力データレートを持つため、様々な振幅と様々な出力データレートの信号を変換する際に使うことができます。

アプリケーションでは一般に所定のスループットが必要になります。すなわち、与えられた数のチャンネルを与えられた時間内に読出す必要があります。実現できるスループットは、読出すチャンネル数とADC が各チャンネルを変換するために要する時間に依存します。このアプリケーション・ノートで述べるADC には次の複数の動作モードがあります。

- Sinc4 フィルタまたはSinc3 フィルタ

- チョップをイネーブル/ディスエーブル

- ゼロ・レイテンシ

- シングル変換モード

- 自動チャンネル・シーケンシング

許容される出力データレートおよび/またはセトリング・タイム(チャンネル切り替え後に最初の変換結果を得るまでに要する時間)は、各動作モードで異なります。このため、スループットも動作モードに依存します。

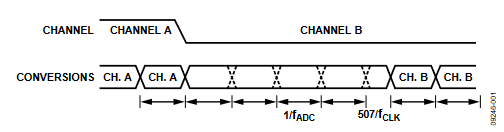

Sinc4 フィルタ(チョップをディスエーブル)

sinc4 フィルタを選択し、かつチョップをディスエーブルした場合、1 つのチャンネルを連続的に変換するときの出力データレート(fADC)は、次のようになります。

fADC = fCLK/(1024 × FS[9:0])

ここで、fCLK はマスター・クロック周波数、FS[9:0]はモード・レジスタにロードされたフィルタ・ワード。チャンネル切り替え後の最初の変換を得るまでに要する時間は、ほぼ次の値になります。

tSETTLE = 4/(fCLK/(1024 × FS[9:0]))

= 4096 × FS[9:0]/fCLK

この式は、低出力データレートを使用する場合には十分正確な値を与えます。セトリング・タイムの完全な式は、次のようになります。

tSETTLE = 4/(fCLK/(1024 × FS[9:0])) + 507/fCLK

= (4096 × FS[9:0] + 507)/fCLK

このため、チャンネルを切り替えるときは、最初の変換結果を得るまでにセトリング・タイムが必要です。このチャンネルでの後続変換は、設定された出力データレート(fADC)で行われます。複数のチャンネルを使用し、かつ各チャンネルから1 つの変換結果を読出すアプリケーションでは、各変換でセトリング・タイムが必要です。このため、毎秒読出すチャンネル数は次のようになります。

スループット = fCLK/(4 × 1024 × FS[9:0] + 507)

= fCLK/(4096 × FS[9:0] + 507)

変換が1 つのチャンネルで完了すると、変換する次のチャンネルを選択するために、設定レジスタへの書込みが必要になります。このSPI 通信がスループットを小さくします。表1に、幾つかのサンプルFS[9:0]値に対する出力データレート、セトリング・タイム、スループットをまとめます(SPI 通信に要する時間は無視します)。

| FS[9:0] | fADC (Hz) | tSETTLE (ms) | Channels per Second |

| 96 | 50 | 80.1 | 12 |

| 80 | 60 | 66.8 | 14 |

| 1 | 4800 | 0.936 | 1067 |

図1.チャンネル切り替え(Sinc4 フィルタ、チョップをディスエーブル)

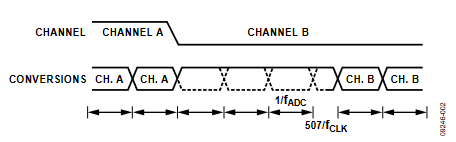

Sinc3 フィルタ(チョップをディスエーブル)

モード・レジスタのSINC3 ビットを設定すると、デジタル・フィルタをsinc3 フィルタに切り替えることができます。sinc3 フィルタを選択しても、出力データレートに影響はありません。このため、1 つのチャンネルを連続的に変換する際の出力データレートも次式で与えられます。

fADC = fCLK/(1024 × FS[9:0])

ただし、チャンネル切り替え後に有効な変換結果を得るのに要する時間は、小さくなります。

tSETTLE = 3/(fCLK/(1024 × FS[9:0])) + 507/fCLK

= (3072 × FS[9:0] + 507)/fCLK

低出力データレートでは、この式は次式で近似されます。

tSETTLE = 3072 × FS[9:0]/fCLK

チャンネルあたり1 変換結果が読出されるマルチチャンネル・アプリケーションでは、システムのスループットは次式で表されます。

スループット = fCLK/(3 × 1024 × FS[9:0] + 507)

= fCLK/(3072 × FS[9:0] + 507)

表2 に、幾つかのサンプルFS[9:0]値に対する出力データレート、セトリング・タイム、スループットをまとめます。実際には、各チャンネルをマニュアルで選択するので、スループットが低下します。

| FS[9:0] | fADC (Hz) | tSETTLE (ms) | Channels per Second |

| 96 | 50 | 60.1 | 16 |

| 80 | 60 | 50.1 | 19 |

| 1 | 4800 | 0.728 | 1373 |

図2.チャンネル切り替え(Sinc3 フィルタ、チョップをディスエーブル)

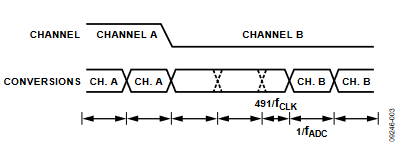

チョッピングのイネーブル

Sinc4 フィルタ

sinc4 フィルタを選択し、かつチョップをイネーブルした場合、1つのチャンネルを連続的に変換するときの出力データレート(fADC)は、次のようになります。

fADC = fCLK/(1024 × FS[9:0] × 4 + 16)

= fCLK/(4096 × FS[9:0] + 16)

チャンネル切り替え後に変換結果を得るまでに要する時間(セトリング・タイム)は、次の値になります。

tSETTLE = 2/(fCLK/(1024 × FS[9:0] × 4 + 16)) + 491/fCLK

= (8192 × FS[9:0] + 523)/fCLK

低出力データレートでは、これら式は次式で近似されます。

fADC = fCLK/(4096 × FS[9:0])

tSETTLE = 8192 × FS[9:0]/fCLK

チャンネルあたり1 変換結果を読出すアプリケーションで複数のチャンネルが使用される場合、スループットは次式で表されます。

fCLK/(2 × (1024 × FS[9:0] × 4 + 16) + 491)

= fCLK/(8192 × FS[9:0] + 523)

各チャンネルを選択するための設定レジスタへの書込みにより、さらにスループットが低下します。

表3 に、幾つかのサンプルFS[9:0]値に対する出力データレート、セトリング・タイム、スループットをまとめます。

| FS[9:0] | fADC (Hz) | tSETTLE (ms) | Channels per Second |

| 96 | 12.49 | 160.1 | 6 |

| 80 | 14.99 | 133.4 | 7 |

| 1 | 1195.3 | 1.773 | 563 |

Sinc3 フィルタ

sinc3 フィルタを選択し、かつチョップをイネーブルした場合、1つのチャンネルを連続的に変換するときの出力データレートは、次のようになります。

fADC = fCLK/(1024 × FS[9:0] × 3 + 16)

= fCLK/(3072 × FS[9:0] + 16)

セトリング・タイムは、

tSETTLE = 2/(fCLK/(1024 × FS[9:0] × 3 + 16)) + 491/fCLK

= (6144 × FS[9:0] + 523)/fCLK

低出力データレートでは、これら式は次式で近似されます。

fADC = fCLK/(3072 × FS[9:0])

tSETTLE = 6144 × FS[9:0]/fCLK

このため、チャンネル切り替え後の最初の変換ではtSETTLE 時間が必要となり、このチャンネルの後続変換は1/fADC で行われます。

チョップをイネーブルし、かつシステムで複数のチャンネルを使用する場合、スループットは、

fCLK/(2 × (1024 × FS[9:0] × 3 + 16) + 491)

= fCLK/(6144 × FS[9:0] + 523)

各チャンネルの選択のために必要なSPI 通信により、さらにスループットが低下します。

表4 に、幾つかのサンプルFS[9:0]値に対する出力データレート、セトリング・タイム、スループットをまとめます。

| FS[9:0] | fADC (Hz) | tSETTLE (ms) | Channels per Second |

| 96 | 16.67 | 120.1 | 8 |

| 80 | 19.99 | 100.1 | 9 |

| 1 | 1591.7 | 1.356 | 737 |

図3.チャンネル切り替え(チョップをイネーブル)

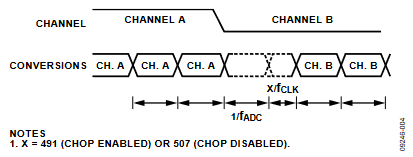

ゼロ・レイテンシ

これらのΣ-Δ ADC は、ゼロ・レイテンシ・モードでも動作することができます。このモードは、モード・レジスタのビットMR11 (ビット・シングル)を1 に設定すると、イネーブルされます。このモードがイネーブルされると、1 つのチャンネルを連続変換する際の変換時間は、ほぼセトリング・タイムと等しくなります。このモードの利点は、変換が1 つのチャンネルで行われるか、または複数のチャンネルで行われるかにかかわらず、すべての変換の間の時間が同じになることです。

チャンネルを切り替えるとき、最初の変換で491/fCLK または507/fCLK の余分な遅延が発生します。低い出力データレートでは、この余分な遅延がセトリング・タイム値に影響を与えることはほとんどありませんが、高い出力データレートでは、遅延を考慮する必要があります。表5に、1 つのチャンネルを連続変換する際と、様々なフィルタ設定に対してチャンネルを切り替える際の出力データレートをまとめます。

| Filter | Chop | fADC | tSETTLE |

| Sinc4 | No | fCLK/(4096 × FS[9:0]) | (4096 × FS[9:0] + 507)/fCLK |

| Sinc3 | No | fCLK/(3072 × FS[9:0]) | (3072 × FS[9:0] + 507)/fCLK |

| Sinc4 | Yes | fCLK/(8192 × FS[9:0] + 32) | (8192 × FS[9:0] + 523)/fCLK |

| Sinc3 | Yes | fCLK/(6144 × FS[9:0] + 32) | (6144 × FS[9:0] + 523)/fCLK |

チャンネル間で切り替える場合、AD719x ではチャンネル切り替え後の最初の変換を得るまでに、フル・セトリング・タイムを確保することができます。このため、複数のチャンネルがイネーブルされた場合、ADC は自動的にゼロ・レイテンシ・モードで動作します—シングル・ビットを設定する意味がありません。

例えば、sinc4 フィルタを選択した場合、チョップがディスエーブルされ、ゼロ・レイテンシがイネーブルされ、FS = 96 のとき、出力データレートは12.5 Hz になります。このため、変換時間は80 ms になり、セトリング・タイムは80.1 ms になります。FS= 96 のとき、毎秒最大12 チャンネルをサンプルすることができます。したがって、スループットは、チョップをディスエーブルし、ゼロ・レイテンシをディスエーブルしたsinc4 の場合と同じになります。

図4.ゼロ・レイテンシ

シングル変換モード

これらのADC は、デバイスが変換を行った後にパワーダウン・モードになるシングル変換モードも持っています。このモードは、ADC が連続変換を行うPLC のようなアプリケーションと関係ありませんが、アプリケーションで、複数の入力チャンネルを使い、変換結果を各チャンネルから周期的にリードバックする場合、このモードが有効です。

モード・レジスタのMD2 ビット、MD1 ビット、MD0 ビットに書込むと、変換が開始されます。これらのビットが適切に設定されると、ADC がパワーアップします。内部クロックを使用する場合は、パワーアップ時間が必要です。その後、変換結果を得るためにはフル・セトリング・タイムが必要です。ADC はこの変換結果をデータ・レジスタにロードし、DOUT/RDYをロー・レベルにして、パワーダウン・モードに戻ります。この場合のスループットは、使用されるチャンネル数、選択された出力データレート、ADC との通信に要する時間に依存します。

チャンネル・シーケンサ

AD7194にはシーケンサがないため、このデバイスはこのセクションに関係しません。

FS[9:0]ビットの値と使用される動作モードは、スループット・レートに影響する主な要因ですが、説明したすべてのモードでは、変換と変換の間に設定レジスタに書込みを行って変換する次のチャンネルを選択する必要があります。シングル変換モードでは、設定レジスタの他にモード・レジスタにも書込みを行って、次のシングル変換を開始させる必要があります。

これらのADC は、マルチチャンネル・アプリケーションでのデバイスの使用を簡素化するチャンネル・シーケンサを内蔵しています。アプリケーション内で使用されるすべてのチャンネルがイネーブルされます。シーケンサは、イネーブルされたチャンネルを順次選択して、各チャンネルで変換を行います。チャンネル・シーケンサは、すべてのチャンネルが同じPGA ゲインと出力データレートを使用する場合にのみ、使うことができます。例えば、各チャンネルが異なるPGA ゲインを使う場合には、シーケンサをディスエーブルする必要があります。

設定レジスタのビットCH0 ~ビットCH7 を設定すると、各チャンネルがイネーブルされて使用可能になります。ADC は変換する際に、イネーブルされた各チャンネルを順次自動的に選択して、各チャンネルの変換を行います。DOUT/RDYピンがロー・レベルになるごとに、チャンネルの変換結果が得られます。モード・レジスタのビットDAT_STA が1 に設定されると、ステータス・レジスタ値が各変換結果に付加されます。ステータス・レジスタは、チャンネルと変換結果の対応を表示します。また、ERR ビットを使って変換が有効か否かも表示します。

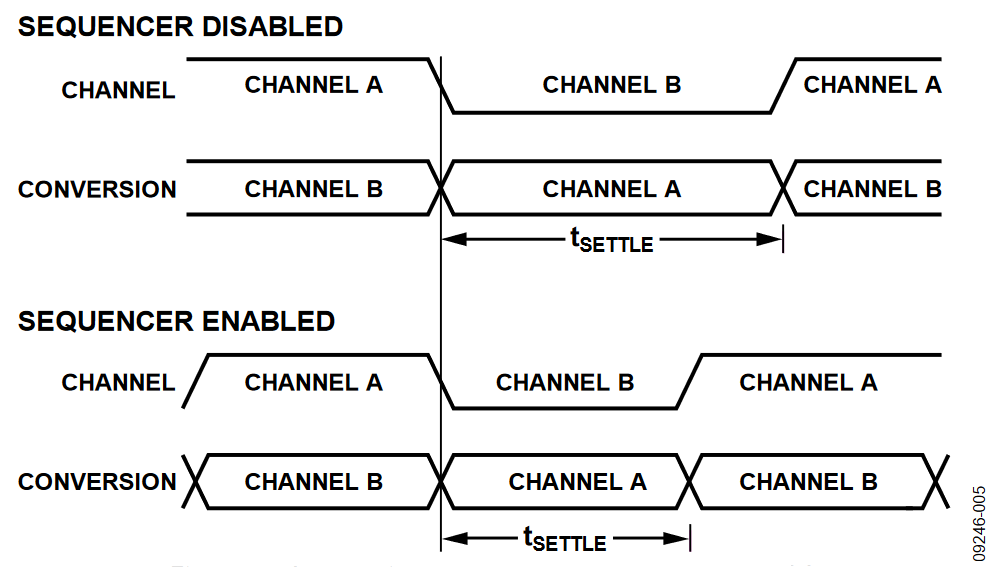

チャンネル・シーケンサをイネーブルした場合、チャンネルあたりのセトリング・タイムは、使用するフィルタ構成に依存しますが、シーケンサをディスエーブルした場合の、前に説明した設定と比較して、シーケンサをイネーブルした場合のセトリング・タイムは小さくなります。シーケンサをディスエーブルした場合、チャンネルを切り替えた際にセトリング・タイムに491/fCLK または507/fCLK の遅延が発生します。シーケンサをイネーブルした場合は、この遅延は変換する最初のチャンネルでのみ発生します。後続チャンネルのセトリング・タイムは小さくなります。表6に、シーケンサをイネーブルしたときの、各チャンネルのセトリング・タイムをまとめます。最初の変換では、491/fCLK の遅延が加わります。

| Filter | Chop | tSETTLE |

| Sinc4 | No | (4096 × FS[9:0] + 16)/fCLK |

| Sinc3 | No | (3072 × FS[9:0] + 16)/fCLK |

| Sinc4 | Yes | (8192 × FS[9:0] + 32)/fCLK |

| Sinc3 | Yes | (6144 × FS[9:0] + 32)/fCLK |

表7 に、チョップをディスエーブルし、シーケンサをイネーブルまたはディスエーブルしたときの、sinc4 フィルタを使って変換できる毎秒のチャンネル数の比較を示します。この比較には、シーケンサをディスエーブルした際に次のチャンネルを選択するためにADC とのインターフェースに要する時間は含まれていません。低い出力データレートでは、チャンネル数は同じですが、高い出力データレートでは、シーケンサでのチャンネル数が大幅に増加します。

| FS[9:0] | Channels per Second (Sinc4, Chop Disabled) | |

| Sequencer Disabled | Sequencer Enabled | |

| 96 | 12 | 12 |

| 80 | 14 | 14 |

| 1 | 1067 | 1195 |

図5.シーケンサをイネーブル/ディスエーブルしたときの比較

まとめ

変換結果を取得できるレートは、シングル・チャンネル・アプリケーションとマルチチャンネル・アプリケーションの間で異なります。マルチチャンネル・システムでは、チャンネルが選択されるごとに、最初の変換結果を得るまでにセトリング・タイムが必要です。このため、セトリング・タイムは、チョップのイネーブル/ディスエーブルやフィルタ次数のような、デバイスが設定されるモードに依存します。したがって、マルチチャンネル・システムでデバイスのスループットを求めるときは、アプリケーション内で使用されるチャンネル数を含めて、与えられた構成で必要とされるセトリング・タイムを計算する必要があります。