AN-1075: Synchronous Inverse SEPIC Using the ADP1870/ADP1872 Provides High Efficiency for Noninverting Buck/Boost Applications

はじめに

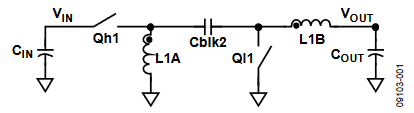

多くの市場では、降圧、昇圧のいずれかのモードで動作する高効率な非反転DC/DCコンバータの需要が増しています。このコンバータは入力電圧を降圧または昇圧して、最小のコスト、部品数、電力損失で安定化電圧を生成します。反転SEPIC(シングルエンド・プライマリ・インダクタ・コンバータ)はZeta(ジータ)コンバータとも呼ばれており、この機能にとって最適な特性を数多く備えています(図 1を参照)。本稿では、この動作の分析と同期整流スイッチング・レギュレータ・コントローラ「ADP1870/ADP1872」を用いた実験によって、このアプリケーションに有用な特性を明らかにします。

反転SEPICの基本

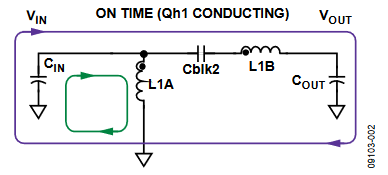

1 次スイッチQh1 と 2 次スイッチQl1 は、互いに反対の位相で動作します。オン時にQh1 はオンし、Ql1 はオフになります。図 2に示すように、電流は 2 経路で流れます。最初の経路は入力から 1次スイッチ経由で、エネルギー転送コンデンサ(Cblk2)、出力インダクタ(L1B)、負荷へと続き、最後にグラウンドを通って入力に戻ります。もう一つの経路は、入力から 1 次スイッチ経由でグラウンド基準のインダクタ(L1A)を通り、グラウンドを介して入力に戻ります。

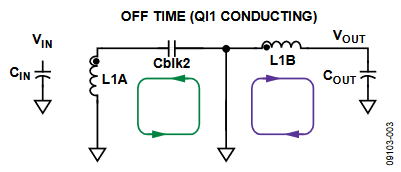

オフ時に、スイッチ位置は逆になります。Ql1 はオン状態で、Qh1はオフです。入力コンデンサ(CIN)は切断されますが、電流はどちらの経路もインダクタ経由で流れ続けます(図 3を参照)。最初の経路は出力インダクタから、負荷とグラウンドを経由し、2 次スイッチを通って出力インダクタに戻ります。もう一つの経路は、グラウンド基準のインダクタから、エネルギー転送コンデンサと 2 次スイッチを経由してグラウンド基準のインダクタに戻ります。

インダクタ電圧時間バランスとコンデンサ電荷バランスの原理に基づいて、式 1に示す DC平衡変換比を求めることができます。

ここで、D はコンバータのデューティサイクルです(スイッチング・サイクルのオン時間の割合)。

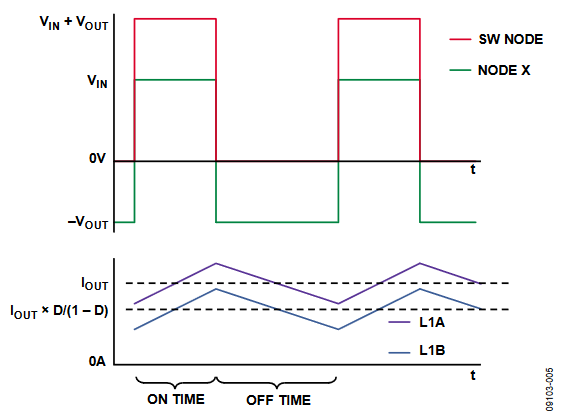

式 1 は、デューティサイクルが 0.5 より大きい場合に出力の安定化電圧が大きくなり(昇圧)、デューティサイクルが 0.5 より小さい場合に安定化電圧が小さくなること(降圧)を示唆しています。この分析からは、ほかにも重要な結果が得られました。エネルギー転送コンデンサ(Cblk2)にかかる定常電圧が無損失システムの VOUTと等しくなるということです。また、出力インダクタ(L1B)を流れる電流の DC 値は IOUTと等しく、グラウンド基準インダクタ(L1A)を流れる電流の DC 値は IOUT × VOUT/VINの値と等しくなります。エネルギー転送コンデンサは、VIN からVOUTまでの電圧に対して DC ブロックも提供します。この特性は、出力が短絡するおそれがある場合に有効です。

さらに、次のような分析結果も得られました。反転 SEPIC の出力電流は連続的なので、出力コンデンサのインピーダンスに対するピーク to ピーク出力電圧リップルは低く抑えられます。そのため、不連続出力電流回路の場合よりも小型で低価格の出力コンデンサを使用できます。

ADP1870/ADP1872を用いて構成した反転SEPIC回路

同期整流構成

一般に、2 次スイッチ(Ql1)は単方向のパワー・ダイオードなので、この回路のピーク効率は制限されます。しかし、アナログ・デバイセズのシングルチャンネル、同期整流スイッチング・コントローラ「ADP1870/ADP1872」(付録Aを参照)を利用すれば、反転SEPICを完全な同期整流構成で設計できます。この構成では、双方向MOSFETを 2 次スイッチとして使用します。そのため、ピーク効率が大幅に改善できると同時に、出力電流が 500 mA程度以上のコンバータのサイズとコストを低減することができます。

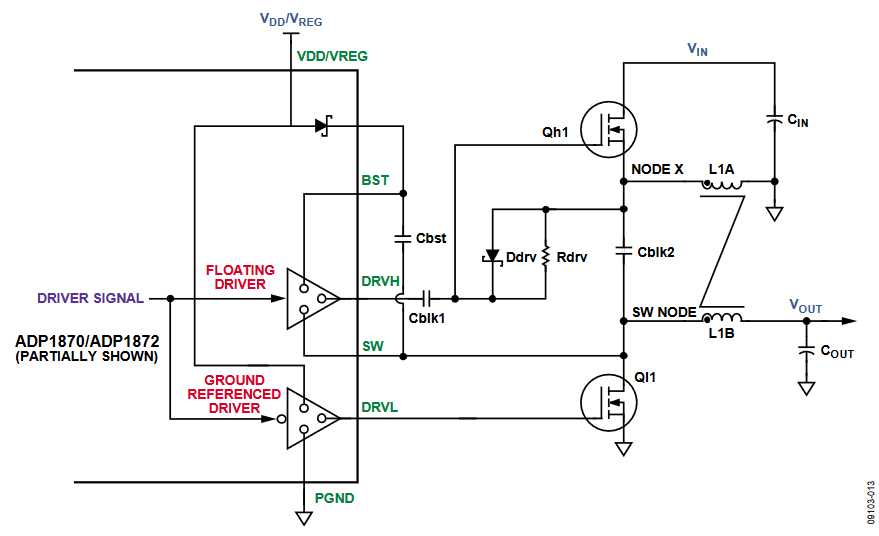

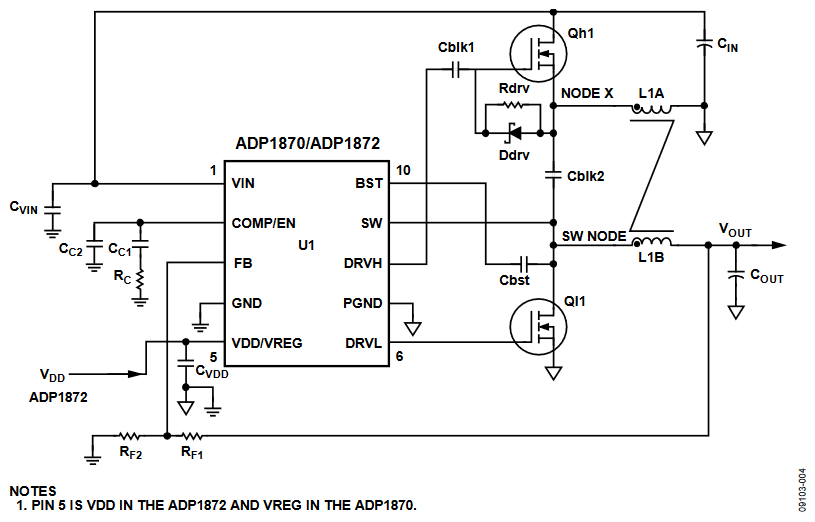

図 5は、ADP1870/ADP1872を使って構成した完全同期整流反転SEPIC構成の電源段を示します。この構成に追加する必要があるのは、消費電力が無視できるほど小さい 3 個の小さな低価格素子(Cblk1、Ddrv、Rdrv)のみです。

この反転SEPICの理想的な定常状態波形を図 4に示します。スイッチ・ノードSW(図 5を参照)は、オン時間中の(VIN + VOUT)とオフ時間中の 0 Vの間でトグルされます。チャージポンプ・コンデンサCbstをSWに接続すると、オン時間中に、ハイサイド内部ドライバ(BSTピン)のブートストラップされた上側レールとハイサイド・ドライバ(DRVHピン)の出力にVIN + VOUT + VDDにほぼ等しい電圧がかかるため、1 次フローティングNチャンネルMOSFETスイッチQh1 の機能が改善されます。クランピング・ダイオードDdrvは、定常状態時にCblk1 にかかる電圧を約VOUT + VFWD (Ddrv)にします(DRVHピンからQh1 のゲートまでを基準)。この場合は、オフ時間中にCblk1とCblk2を実際に並列にします。Cblk1 にかかる電圧は、ノードXの電圧が−VOUTにほぼ等しいときオフ時間中に 1 次スイッチがそのスレッショールドより大きなゲート・ソース間電圧を発生させないようにします。

ADP1871とADP1873はADP187xファミリー製品で、軽負荷時の効率を高めるパルススキップ・モード(PSM)を備えています。軽負荷時には、スイッチング・レートを低減し、出力に十分なエネルギーを供給して安定化した出力電圧を維持し、降圧回路におけるゲート電荷やスイッチング損失を大幅に減らすことができますが、同期整流反転SEPIC回路でのADP1871とADP1873の構成は推奨していません。

スイッチング周波数の予測

付録Aに示すように、ADP1870/ADP1872は、フィードフォワード技術およびスイッチ・ノード平均化技術を適用したコンスタント・オンタイム・アーキテクチャを採用し、一般のコンスタント・オンタイム・アーキテクチャに見られるスイッチング周波数の変動を最小限に抑えています。SWピンは、同期整流反転SEPIC回路で構成されているようにSWノードに接続されます(図 6を参照)。したがって、ADP1870/ADP1872シリーズの各デバイスのスイッチング周波数は次のように予測できます。

ADP187xARMZ-0.3-R7 − a = 3.33 × 10-6

ADP187xARMZ-0.6-R7 − a = 1.66 × 10-6

ADP187xARMZ-1.0-R7 − a = 1 × 10-6

これらのデバイスはそれぞれ 300 kHz、600 kHz、1 MHz として指定されますが、この指定は降圧回路を構成するときの近似スイッチング周波数にのみ当てはまります。

図7に示すように、スイッチ・ノードの平均はオン・タイマに提供されます。無損失システムの場合、この平均は出力電圧と同じです。しかし、出力負荷が増大し、コンバータの損失が増えると、スイッチ・ノード平均は出力電圧からわずかにずれるため、出力負荷の増加に伴ってスイッチング周波数も増大します。一般に、この増加値は負荷の全負荷範囲で無負荷状態の 10%より大きくはなりません。損失のかなり大きいシステムでは、スイッチング周波数の増加がこれより多くなる可能性があります。

インダクタ結合、エネルギー転送コンデンサ

パワー・インダクタL1A、L1Bを図 6に示します。「小信号の分析とループ補償」で説明するように、この回路でインダクタを結合する目的は、出力電圧とインダクタ電流のリップルを低減すること、そしてクローズド・ループ帯域幅の上限を増大させることです。

インダクタを結合する場合でも、結合が強すぎて、大量のエネルギーが最初の巻線から別の巻線へとコア経由で転送されることは好ましくありません。これを避けるには、結合インダクタのリーク・インダクタンス(LLKG)を求め、エネルギー転送コンデンサ(Cblk2)の複素インピーダンスの大きさが単一巻線の DCRとリーク・インダクタスの複素直列インピーダンスの 1/10 になるよう Cblk2 のサイズを選択する必要があります。このインピーダンスは式 3、式 4、式 5 を使って求めることができます。この関係式に当てはまるように回路を設計すれば、結合コア経由のエネルギー転送を最小限に抑えられます。リーク・インダクタンスは、結合係数を使って計算できます。この係数は、通常、結合インダクタのデータシートに記載されています。

電流図の図 2と図 3に示すように、電荷はオン時間中に蓄積され、オフ時間中に除去されます。エネルギー転送コンデンサに電流が流れても、電圧変動はその公称DC電圧の±10%より大きくなることはありません(「同期整流構成」を参照)。次の不等式が真となるようにCblk2 のサイズを決めれば、電圧変動は十分に小さいものとなります。

巻数比は 1:1 とするのがよいでしょう。そうすれば、任意のレベルの出力電圧リップルに対してディスクリート・インダクタで必要とされる巻線ごとのインダクタンスの半分で済むからです(「参考資料」の『Coupled-Inductor and Other Extensions of a New Optimum Topology Switching DC-DC Converter(Ćuk、Middlebrook共著)』を参照)。1:1 と異なる比を使用することもできますが、その場合の特性がどうなるかについては、本稿に掲載した式を用いて正確に予測することはできません。

容量結合ゲート駆動回路

ゲート駆動コンデンサ(Cblk1)の値は、複数の動作パラメータにより制限されます。このコンデンサの容量は十分に確保する必要があります。そうしないと、ハイサイド・スイッチのターンオン時の帯電やターンオフ時の放電のために、電圧の変動幅がその公称 DC 値の±10%より大きくなってしまいます。この DC 値は「同期整流構成」で述べたように VOUT + VFWD (Ddrv)です。また、故障状態中に BST と SW ノード間に過剰な電圧がかかるのを避けるために、Cblk1 の値は Cbst の 1/10 にします。Cbst と Rdrv のRC 時定数は、スイッチング期間よりかなり長くする必要があります。Rdrv は、コンバータがディスエーブルされた後に Qh1 の放電経路を提供します。Cblk1 と Rdrv の適正な開始値はそれぞれ100 nF、1 kΩ です。したがって、Cbst は 1 µF とします。一般的な低価格帯の小型ショットキ・バリア・ダイオード BAT54 は、導通電流が非常に小さいので Ddrv には十分です。

小信号の分析とループ補償

反転 SEPIC の完全な小信号分析は本稿の範囲を超えています。しかし、アプリケーションの観点からすると、この分析の大部分は必要のないものであり、いくつかの指針に従えば、堅牢な回路を設計することができます。

共振周波数(fRES)には多くの複素インピーダンス相互作用がありますが、最初に fRESを計算するために目標クロスオーバー周波数の上限値を求めます。インダクタが非結合の場合、共振周波数は低下し、クローズド・ループ帯域幅の上限は大幅に低下します。

この周波数では、300°以上の大きい Q 位相遅れが生じる可能性があります。全負荷範囲でコンバータの低位相余裕を避けるには、目標クロスオーバー周波数(fUNITY)を fRESの 1/10 にする必要があります。この共振の減衰は、出力負荷抵抗とインダクタの結合DC 抵抗に大きく左右されます。いくらか程度は落ちますが、減衰はエネルギー転送コンデンサの等価直列抵抗(ESR)とパワーMOSFET(Qh1、Ql1)のオン抵抗にも左右されます。したがって、出力負荷抵抗が変動すると、クローズド・ループ伝達関数のシグニチャがこの周波数で大きく変動することがあります。

結合係数はパラメータとして適正に制御できない場合がよくあるため、fRES がスイッチング周波数 fSWQ より小さいと仮定し、目標クロスオーバー周波数 fUNITYを fRESより 1 ディケード低く設定します。fUNITY を設定するときは、2 個の極と 1 個のゼロを持つ標準的なタイプ II 補償を使用できます。

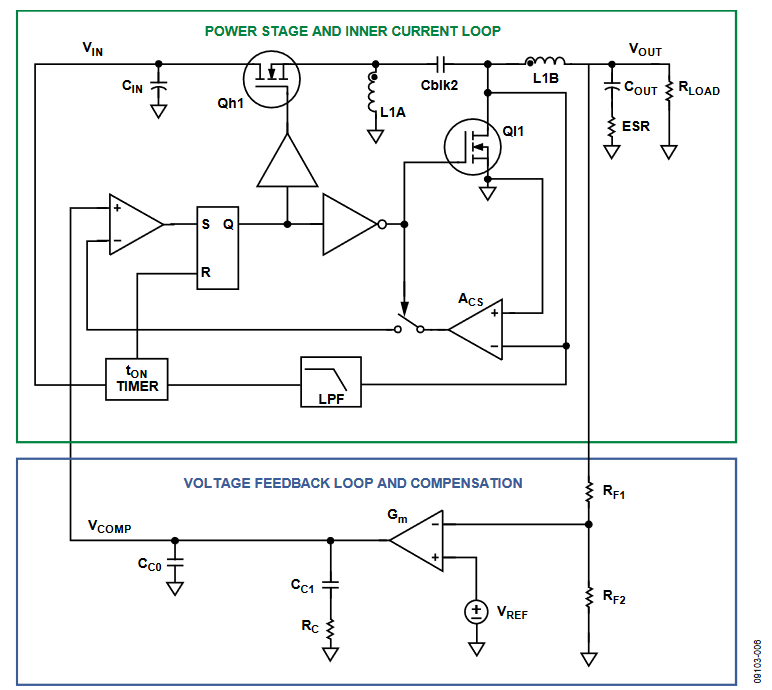

図 7に、ADP1870/ADP1872 帰還ループの等価回路(同期整流反転SEPIC降圧/昇圧回路での使用時)を示します。上の枠内に電源段と内部電流ループを示し、下の枠内に電圧帰還ループと補償回路を示します。

下枠内の補償部品の値は次式で計算できます。

ここで、:

COUTはコンバータの出力容量です。

ESRは出力コンデンサの等価直列抵抗です。

RLOADは最小出力負荷抵抗です。

GmはADP1870/ADP1872ファミリー用誤差アンプ(520 µs)のトランスコンダクタンスです。

VREFFは誤差アンプの正の入力に接続されるリファレンス電圧で

す。ADP1870/ADP1872の場合は 0.6 Vです。

コンバータのトランスコンダクタンス GCSは、次式で計算します。

ここで、

GCSは、昇圧時の 2 次スイッチの抵抗 RDS(ON)とデューティサイクル D に応じて、周波数に関係なく変動するゲインを表す項です。この抵抗とデューティサイクル D が最小のとき、クロスオーバー周波数が最大になるものと予想されます。

ACSs は電流検出ゲインです。ADP1870/ADP1872 では、3 V/V から24 V/V までの 4 ステップからゲインを選択できます。

あまり早い段階で電流制限が発生しないように、次の不等式に従って電流検出ゲイン(ACS)の最大値を選択してください。

ここで、ΔILはピーク to ピーク・インダクタ・リップル電流です。

ADP1870/ADP1872はコンスタント・オンタイム・アーキテクチャを使用しているため、電流モード制御で一般に見られるサンプリング・ポールが制御ループ内に存在しません。したがって、適正量のスロープ補償信号を検知電流信号に加える複雑な処理は必要ありません。

電源部品のストレス

図 2と図 3に電流図を示しましたが、この場合はパワーMOSFETが導通時にインダクタ電流の合計を搬送します。したがって、両スイッチを流れる電流の直流成分は次式で表されます。

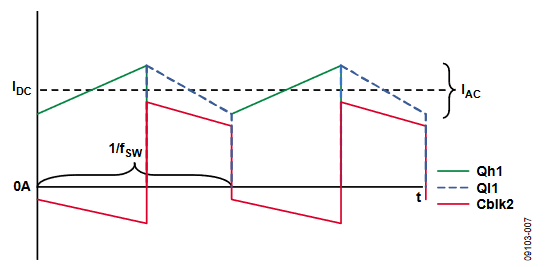

インダクタの結合比が 1:1 の場合、両スイッチを流れる電流の交流成分は次式で表されます。

MOSFET電流の直流成分と交流成分が既知の場合は(図 8を参照)、各スイッチに流れる電流のRMS値を簡単に計算することができます。選択したMOSFETのRDS(ON)MAXとRMS値を利用すれば、MOSFETを熱的に安定させ、効率条件に合うように消費電力を低く抑えることができます。

1 次スイッチのスイッチング損失を正確に計算することは本稿の範囲を超えていますが、計算に関する注意事項を以下に記しておきます。抵抗が高い状態から低い状態に遷移するとき、MOSFET にかかる電圧は VIN + VOUT前後から 0 V 前後にスイングし、デバイスを流れる電流は 0 A から IOUT(1/(1 – D))前後にスイングします。このため、スイッチング損失は、主要損失となり得ます。MOSFET は逆転送容量(CRSS)と RDS(ON)が反比例するため、この素子を選択する場合には、こうした損失を考慮しておかなければなければなりません。

1 次スイッチと 2 次スイッチの両方のドレイン・ソース間降伏電圧(BVDSS)は、入力電圧と出力電圧の合計より大きくなければなりません(図 4を参照)。

ピーク to ピーク出力電圧リップル(ΔVRIPPLE)の概算値は次式で求められます。

出力コンデンサ(IrmsCout)を流れる電流の RMS 値は次式で表されます。

式 14 に示したピーク to ピーク・インダクタ電流(ΔIL)は入力電圧に依存するため、設計者はこのパラメータの変動によって出力電圧リップルが規定値を超えないようにし、出力コンデンサを通る RMS 電流がその定格値を超えないようにします。

図 8に示したエネルギー転送コンデンサCblk2 を流れるRMS電流は次式で表されます。

高出力電流アプリケーションの場合は、個別のコンデンサのRMS 定格を超えないよう Cblk2 に対して複数のコンデンサを並列接続することがよくあります。

ADP1870/ADP1872 を使って構成される同期整流反転 SEPIC の場合は、入力電圧と出力電圧の合計が 20 V を超えてはなりません。その理由は、チャージポンプ・コンデンサがスイッチ・ノードに接続され、その電圧が 1 次スイッチの導通時に VIN + VOUTに達するからです。

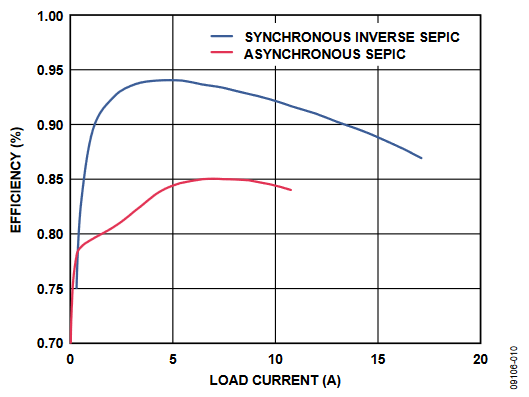

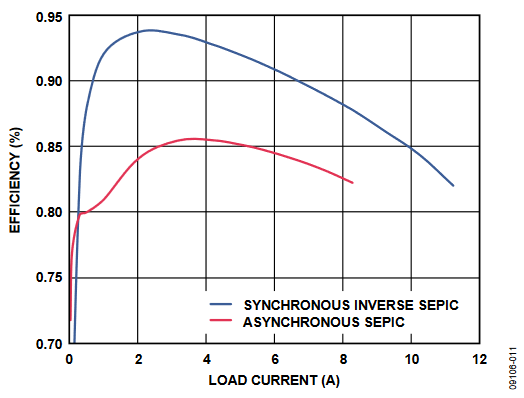

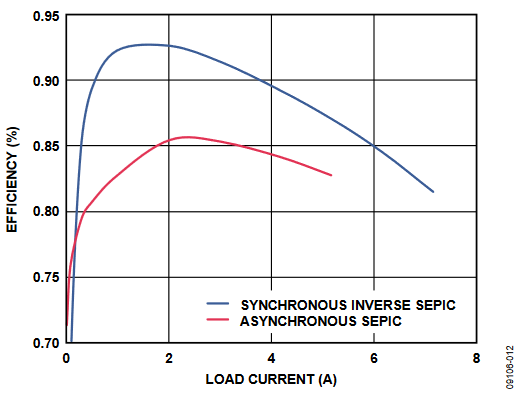

ラボの結果

図 9、図 10、図 11は、同期整流反転SEPICと非同期整流SEPIC(非反転昇降圧コンバータの旧式の構成)において入力電圧から出力5 Vまでの範囲で達成される効率を比較したものです。この 2 つの回路は、高効率を実現するために個別に最適化されており、広い入力電圧範囲のアプリケーションに対応しています。これには、5Vの低電流バイアスがかけられています。

同期整流反転SEPICはADP1872を使って構成されています。関連する電源部品のBOMを表 1に示します。ここには一般的な市販の部品のみを記載しています。非同期整流SEPICは、アナログ・デバイセズのスイッチング・コントローラADP1621を使って構成されています。関連電源部品のBOMを表 2に示します。

図 9~図 11に示すように、出力電流が約 500 mA以上の場合は、同期整流反転SEPICが非同期SEPICより高効率となっています。

各入力電圧において、同期整流反転SEPICは低部品数、高効率でより多くの出力電流を提供できます。表 1と表 2に示すように、同期整流反転SEPICは電力変換に 2 個のMOSFETを使用しますが、非同期SEPICは電力変換に 2 個のMOSFETと大きなパワー・ダイオードを使用します。そのため、同期整流で構成したほうが、部品数が少なくてすみ、フットプリントの小型化、コスト低減、電流出力能力の向上を実現できます。

| Designator | Part Number | Manufacturer | Value | Package | Comment |

| Qh1 | BSC090N03MS | Infineon | 30 BVDDS | SuperSO8 | Power MOSFET, 11.2 mΩ (maximum) at 4.5 VGS, TJ = 25°C |

| Ql1 | BSC016N03MS | Infineon | 30 BVDDS | SuperSO8 | Power MOSFET, 2 mΩ (maximum) at 4.5 VGS, TJ = 25°C |

| L1A/L1B | PCA20EFD-U10S002 | TDK | 3.4 µH per winding | 30 mm × 22 mm × 12 mm | :1:1:1:1:1 coupled inductor, ferrite, 35.8 mΩ (maximum) DCR per winding |

| Designator | Part Number | Manufacturer | Value | Package | Comment |

| Power MOSFET | BSC057N03MS | Infineon | 30 BVDSS | SuperSO8 | Quantity = 2, 7.2 mΩ (maximum) at 4.5 VGS, TJ = 25°C |

| Power Diode | PDS1040L | Diodes Inc. | 40 BVRMM/10 IO | PowerDI5 | VF = 0.46 V (maximum) at TS = 25°C |

| Coupled Inductor | DRQ127-2R2-R | Cooper Bussmann | 2.03 µH per winding | 10 mm × 12.5 mm × 8 mm | 1:1 coupled inductor, ferrite, 7 mΩ (maximum) DCR per winding |

結論

多くの市場では、入力より高い電圧ないしは低い電圧を提供する高効率のDC/DCコンバータ(昇圧型/降圧型)は、いずれのタイプもニーズが増しています。アナログ・デバイセズの 同期整流スイッチング・レギュレータ・コントローラADP1870/ADP1872を用いて、電源段で通常使用されている高損失のパワー・ダイオードの代わりに低損失のMOSFETを使用することができます。この高効率化はコスト低減とソリューション・サイズの縮小をもたらし、システムは厳しいエネルギー条件に対応することができます。いくつかの指針に従えば適正な補償部品値を計算することができ、一般的な市販の部品を使って高効率を達成できます。

参考資料

Slobodan Ćuk、R.D. Middlebrook共著『Coupled-Inductor and Other Extensions of a New Optimum Topology Switching DC-DC Converter(Advances in Switched-Mode Power Conversion 第 1 巻、第 2 巻)』1983 年、Irvine, CA: Tesla Co.

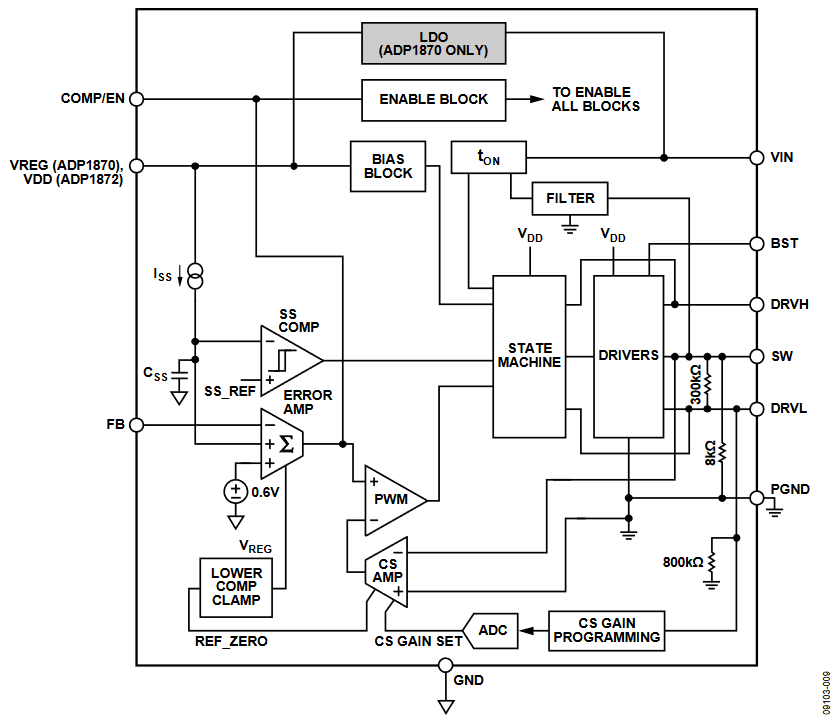

付録A

ADP1870/ADP1872(図 12を参照)はコンスタント・オンタイム・スイッチング・コントローラであり、Nチャンネルの同期パワーMOSFETを駆動するドライバを内蔵しています。コンスタント・オンタイム・アーキテクチャは入力電圧フィードフォワード技術とスイッチ・ノード平均化技術を適用し、一般のコンスタント・オンタイム・アーキテクチャに見られるスイッチング周波数の変動を低減します。この製品ファミリーは、最先端の変調バレー電流モード制御方式も使用しています。

昇圧ダイオードは ADP1870/ADP1872 に内蔵されており、これによって全部品の数とシステム・コストを低減できます。ADP1870は内部リニア・レギュレータを備えていますが、ADP1872は 2.75~5.5 V のバイアス電源を必要とします。

ADP1870/ADP1872 の特長としては、内部で設定されるソフト・スタート期間、Hiccupモード電流制限、サーマル・シャットダウン保護、3 種類のスイッチング周波数オプションなどがあります。ADP1870/ADP1872 は 、 –40 ~ +85°C の温度範囲で −0.834%/ +0.884%の電圧出力精度を、また−40~+125°Cのジャンクション温度範囲で −0.834%/+1.084% の精度を提供します。ADP1870/ADP1872は電源段の入力電圧 2.75~20 Vで駆動されます。本製品は 10 ピンMSOPパッケージを採用しています。