はじめに

マイクロフォンの年間販売数は20億を超えており、この販売量ゆえにマイクロフォン市場が注目されています。市場の約半分は、安価でグレードの低い、サイズや性能が重要ではない玩具市場やその他のアプリケーション向けのマイクロフォンです。残りの半分は、携帯電話、ヘッドセット、デジタル・カメラ、ラップトップなどの携帯型ハイエンド・アプリケーション市場です。この市場で中心となっているのは携帯電話メーカーで、毎年約9億個のデバイスを利用しています。推定年間成長率10%と、携帯電話はマイクロフォン市場で最も急成長している分野といえます。携帯電話の小型化が進む一方、搭載機能はさらに増加し、高性能の次世代マイクロフォンが求められています。

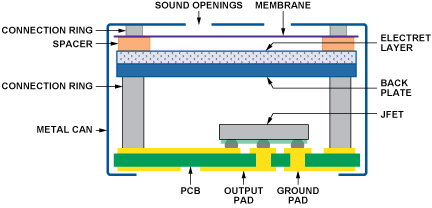

長年、電気通信アプリケーションで利用されていたマイクロフォンは、エレクトレット・コンデンサ(ECM)型でした。このタイプのマイクロフォンは、振動膜、背面電極、エレクトレット層で構成されています。振動膜と固定背面電極が可変コンデンサの極板になります。エレクトレット層はおよそ100Vのコンデンサ電圧に対応する固定電荷を蓄えます。音圧によって膜が移動し、マイクロフォンの容量が変動します。コンデンサの電荷は一定なため、コンデンサ両端の電圧が容量の変化に従って変動します。これは、以下のコンデンサの電荷式に基づきます。

Q は電荷(クーロン)、Cは容量(ファラッド)、Vは電圧(ボルト)です。音圧によるごくわずかな容量の増減ΔCに比例して、電圧の増減ΔVが生じます。

モバイル・アプリケーション用のマイクロフォンはきわめて小さく、一般に直径3~4mmで厚さ1~1.5mm程度です。したがって、マイクロフォン容量も比較的小さくなります。代表値は3~5pF程度ですが、場合によってはわずか1pFのこともあります。

容量性マイクロフォンによって生成される信号には駆動力がないため、次の処理に進む前にバッファ/アンプが必要になります。従来、このマイクロフォンのプリアンプには、単純な接合型電界効果トランジスタ(JFET)が使用されています。図1は、JFETベースのECMパッケージの断面です。

エレクトレット・マイクロフォンのミクロ機械加工技術が改善されたため、マイクロフォンはさらに小型化し、素子の容量が減少しています。標準のJFETでは入力容量が比較的大きいので、マイクロフォン・カートリッジ素子からの信号が大幅に減衰し、十分に対応できません。幸いにして、CMOSプロセス技術の向上により、アンプ回路が改善されました。JFETベースのアンプをCMOSアナログ/デジタル回路に置き換えることで、大きなメリットが得られます。最新のサブミクロンCMOSプロセスで実装されたプリアンプにより、従来のJFETに比べて以下のようにさまざまな点が進歩し、今後もさらなる改善が可能になるでしょう。

- 高調波歪みの減少

- 簡単なゲイン設定

- マルチ機能モード(低消費電力用のスリープ・モードを含む)

- A/D変換(ダイレクト・デジタル出力付きのマイクロフォンを実現)

- 音質を大幅に向上

- 高ノイズ耐性

デジタル出力マイクロフォンのプリアンプ

単純なJFETベースのアンプは本来、低消費電力のデバイスですが、直線性が劣り、精度が低いという欠点があります。改良マイクロフォンの設計における主な目標は、プリアンプ技術とデジタル技術を組み合わせることにより、きわめて低い消費電力を維持しながら、直線性の向上と低ノイズ化によってダイナミック・レンジを増大することです。

携帯電話は、本来ノイズの多い環境で使用されます。従来のJFETのソリューション(および完全に純粋なアナログ・ソリューション)の欠点は、アナログ・マイクロフォン出力の信号がアンプとA/Dコンバータ(ADC)の間に潜む干渉信号によってすぐに妨害されてしまうことです。このため、A/D変換をマイクロフォン自体に内蔵し、もともと干渉による影響を受けにくいデジタル出力を利用します。

システムの説明

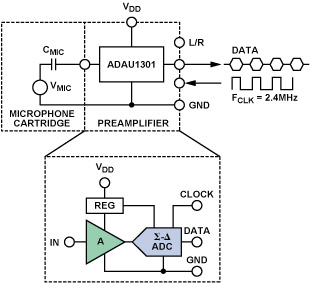

内蔵のデジタル出力プリアンプとそのインターフェースのブロック図を図2に示します。マイクロフォン素子の信号はまず増幅され、次にADCによってデジタル変換されます。内部の電源レギュレータがこれらのブロックに電力を供給するため、十分な電源変動除去比が得られるとともに、デバイスのアナログ部分には独立した電源を利用できます。

プリアンプは、計装アンプ構成で2つのトランスコンダクタンス・アンプ(OTA)を使用してCMOSに内蔵され、マッチング・コンデンサを使用してゲインを設定します。この構成とMOS入力トランジスタによって、容量性の信号源に特に望ましいほぼゼロの入力アドミタンスを提供します。コンデンサをゲイン設定に使用することで、高ゲイン精度(影響するのはプロセス・リソグラフィの制約のみ)と、poly-polyコンデンサ固有の優れた直線性が得られます。アンプのゲインは、配線層マスクを変更する事により簡単に設定でき、最大20dBのゲイン設定が可能です。

- ノイズ・シェーピングによって量子化ノイズが上方へシフトされるため、大部分が音声帯域の外に出ます。このため、回路に厳しいマッチング条件を課さなくても高精度が得られます。

- ADCはシングルビットのΣΔ 型変調器を使用しているため、本質的に線形になります。

- 厳しい設計制約が課せられるのは、シングルビットでシングルループの変調器にある積分器のうち1つだけです。出力にノイズ・シェーピングが行われている内部ループ積分器に対する設計制約はゆるくなります。これによって消費電力が低減します。

高次のΣΔ型変調器にともなう潜在的な問題は、入力が最大安定振幅(MSA)を超えると不安定になりやすいということです。高次の変調器(>2)は、過負荷が原因で不安定になると、入力が減少してMSAを下回っても安定動作に戻れません。潜在的な不安定性に対処するには、デジタル制御の帰還システムによってΣΔ 型ノイズの伝達関数を変更し、変調器を強制的に安定動作に戻します。

システムの入力クロック周波数を1kHz未満に低減するとパワーダウン・モードに入りますが、これによって消費電流は400μAから約50μAに低減し、マイクロフォンを使用しないときにいつでも電力を節約できます。

パワーダウン状態から起動するまでの時間はわずか10msです。

不具合解析機能として特別なテスト・モードがあり、回路内のさまざまな内部ノードにアクセスできます。起動時のDATAピンの特別な設定方法によって、不具合解析の技術者はこれらのノードをDATAピンに切り替えてアクセスできるようになります。

ノイズについて

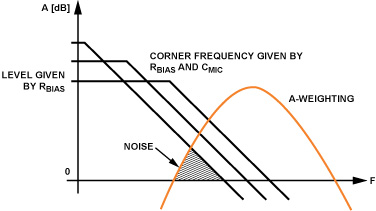

容量性マイクロフォンのCMOSプリアンプにある3つの主なノイズ源は、フリッカ(1/f)ノイズ、入力トランジスタによる広帯域ホワイト・ノイズ、アンプのDC動作ポイントの設定に必要な入力バイアス・レジスタRBIASによるローパス・フィルタ処理済みのホワイト・ノイズがあります。人間の耳では低周波数を聴き取れないことを考慮して、Aウェイトを加えています。

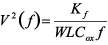

フリッカ・ノイズのスペクトル密度は、トランジスタの面積に反比例します。入力換算フリッカ・ノイズの大きさは、次式で表すことができます。

ここで、Kf はプロセス依存の定数、f は周波数、WはMOS幅、LはMOSの長さ、Coxは単位面積当たりのゲート容量です。1/f ノイズ振幅は、入力トランジスタのサイズを大きくすることで低減できます。入力換算ホワイト・ノイズは、金属酸化物半導体トランジスタ(MOST)のトランスコンダクタンスgmに反比例します。

ここで、k はボルツマン定数、Tは絶対温度です。強反転状態のMOSTでは、gm≒2Id/Veff になります。ここで、Id はドレイン電流、実効電圧はVeff =Vgs -Vth、すなわちゲート/ソース間電圧からMOSTスレッショールド電圧Vth を減算した値です。入力ペアをかなり幅が広い設計にすると、弱反転動作モードに移行するため、MOSTがバイポーラのような動作モードになります。この場合は、gm= Id/(nVT) となります。ここで、nはスロープ係数(代表値1.5)、VT は熱電圧です。このように、MOSTのアスペクト比を最大化することで、最適なホワイト・ノイズ性能が得られます。

入力バイアス・レジスタは容量性のソースに接続しているため、ノイズはローパス・フィルタで処理されます。ノイズがローパス・フィルタ処理済みのホワイト・ノイズで、カットオフ周波数がオーディオ帯域周波数よりもはるかに小さいと想定すると、全ノイズ電力はkT/Cとなります。ここで、Cはノードに結合された容量です。

少ないカートリッジ容量でマイクロフォン・カートリッジの小型化が進むにつれ、マイクロフォン・カートリッジの容量の減少にともないノイズ源が増大することになります。ただし、バイアス・レジスタによって生じるオーディオ帯域のノイズ・パワーは、ローパス・フィルタのカットオフ周波数にも左右されます。カットオフ周波数が低くなるほど、オーディオ周波数範囲に残る全ノイズ・パワーは小さくなります。ノイズを低く抑えるには、マイクロフォン容量の1/2ごとに4倍ずつバイアス抵抗を増やす必要があります。3~5pFのマイクロフォン容量の場合、抵抗の最小値は約10GΩとしなければなりません。

このように大きい値の抵抗をチップに実装するための優れた方法は、平衡状態にある、抵抗値の非常に大きい(一般に1~10TΩ)1組みの逆並列ダイオードを使用することです。信号が大きくなると抵抗が減少し、過負荷状態の後の高速セトリングが保証されます。図3は、RBIASを関数としたインバンド・ノイズです。

プリアンプの入力トランジスタの面積は、マイクロフォンの容量を基準に最適化する必要があります。前述したとおり、入力デバイスが大きくなると1/f ノイズは減少しますが、信号源の容量性負荷が増大するため信号が減衰し、広帯域のS/N比(SNR)が減少します。このためトレードオフが生じます。すなわち、入力デバイスを特に小さくすると信号源の容量性負荷が小さくなりますが、1/f ノイズが大幅に増大し、低周波SNRが減少します。1/f ノイズに対し、最大のSNRを得るための最適化条件は、入力デバイスのゲート/ソース間容量をマイクロフォン容量と寄生容量の合計値に等しくすることです。一方、ホワイト・ノイズの最適化条件は、入力デバイスのゲート/ソース間容量をマイクロフォン容量と寄生容量の合計値の3分の1に等しくすることです。実際には、この2つの値の間でゲート容量を設定することが一番良い妥協策になります。

ブートストラップにより、全チップ入力容量に対する入力パッドの寄与分を最小限に抑えることができます。出力換算ホワイト・ノイズはgmに比例するため、すべての電流源MOSTを強反転領域でバイアスすることで、ノイズ寄与を最小限に抑えます。

表1は、ADAU1301マイクロフォン・プリアンプの主な特性と性能です。

| パラメータ | 値 | 備考 |

| 電源 | 1.64 V ~ 3.65 V |

全電圧範囲で機能しますが、仕様性能は1.8V時のものです。 |

| 電源電流 | 400 µA | @ VDD = 1.8 V |

| M最大ゲイン変動 | X ± 0.4 dBFS/VPeak | X は指定のゲイン |

| 信号帯域幅の最大上限値 | 25 Hz | |

| 信号帯域幅の最小上限値 | 20 kHz | |

| 等価入力換算ノイズ・レベル | 5 µV rms | Aウェイト |

| S/N比 | 60.6 dBFS |

-27dBFS/Paのマイクロフォン感度で計算 |

| ダイナミック・レンジ | >86 dB | @ THD = 10%(ゲインに依存) |

| 入力容量 | 0.1 pF | |

| 最小入力抵抗 | 15GΩ | |

| 起動時間 | 500 ms | VDDが1.8Vに達してからASICゲインが最終整定値の1dB以内にセトリングするまでの測定時間 |

| 最大ウェークアップ時間 | 10 ms | |

| クロック周波数 | 1 MHz ~ 4 MHz | 公称Fclk = 2.4 MHz |

| クロック・デューティ・サイクルfDC | 40% ~ 60% |

完全集積化デジタル・マイクロフォンを実現するために

このデジタル出力アンプはECM素子のニーズを満たしていますが、この組み合わせでは、新しく登場した高集積化を必要とするMEMSマイクロフォン市場には最適とはいえません。エレクトレット層に相当するものが半導体のMEMS素子には存在しないため、容量性素子にはバイアス用の内蔵高電圧源が必要です。マイクロフォン素子は純粋に容量性の負荷であり、バイアス・リファレンスから電流を取れないため、このアンプ・システムの拡張版では、低消費電力のオンチップ・チャージ・ポンプの搭載を予定しています。この場合、電荷蓄積ソースは必要ありません。

結論

モバイル・マイクロフォン市場向けに作られたマイクロフォン・プリアンプによってデジタル出力マイクロフォンが可能になり、当然の流れとしてデジタル出力マイクロフォンへの移行が進んでいます。徹底的なノイズ解析から、所望のダイナミック・レンジを備えた低ノイズ計装アンプが生まれています。低消費電力のΣΔ 型ADCは、厳しい設計上の制約なしに高分解能を実現しています。パワーダウン・モードでは、マイクロフォンを使用しないときに電力を節約することで、バッテリ寿命を最長化できます。特別なテスト・モードは、メーカーのテスト用に通常はアクセスできないノードにアクセスできるように設計されており、プリアンプのアナログ出力を検査できるという利点があります。