目的

今回は、バイポーラ・トランジスタ(BJT)を使用して構成したエミッタ接地回路について検討します。

背景

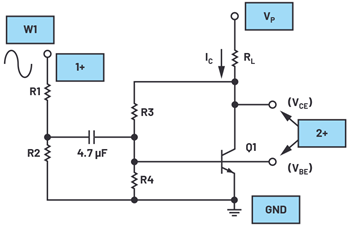

1段構成の基本的なアンプのトポロジは、3種に分類できます。そのうちの1つがエミッタ接地回路です。バイポーラ・トランジスタを使用する場合、電圧を反転増幅するアンプ回路として機能します。トランジスタのベース端子が入力、コレクタ端子が出力です。入力と出力に対し、エミッタが共通に使われる(グラウンドまたは電源に接続)ことから、共通エミッタ・アンプと呼ばれることもあります。

準備するもの

- アクティブ・ラーニング・モジュール「ADALM2000」

- ソルダーレス・ブレッドボード

- 抵抗:5個

- 可変抵抗(ポテンショメータ):50kΩ(1個)

- 小信号NPNトランジスタ:「2N3904」(1個)

説明

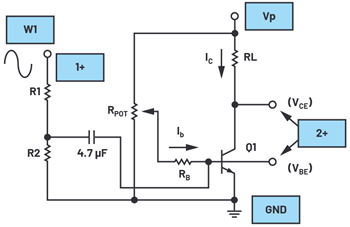

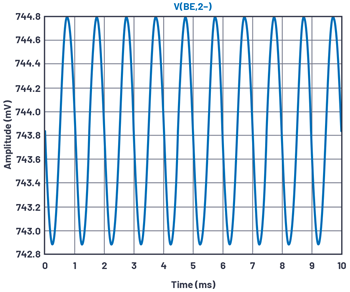

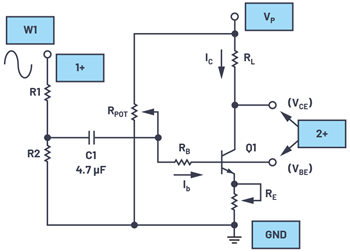

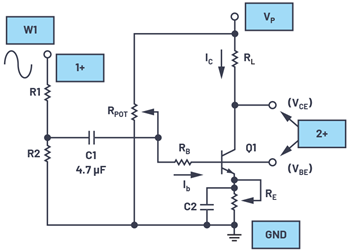

図1に示した回路は、NPNトランジスタをエミッタ接地で使用する例です。出力負荷抵抗RLは、エミッタ電流Icに対して、VCEに現れる電圧が正の電源電圧Vp(5V)の約1/2になるように選択します。また、可変抵抗RPOTと抵抗RBにより、NPNトランジスタQ1のバイアス動作点Ibを設定し、ICが所望の値になるようにします。抵抗R1、R2で構成した分圧回路は、ADALM2000の任意波形ジェネレータ(AWGのW1)からの入力信号が十分に減衰されるように選択します。このように構成するのは、Q1のベースに現れる信号VBEがやや小さくなるので、それを観測しやすくするためです。減衰されたW1の信号は、4.7μFのコンデンサを介してQ1のベースにAC結合されます。それにより、DCバイアスに影響が及ばないようにします。

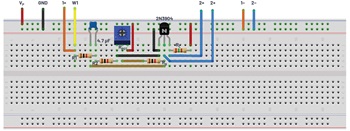

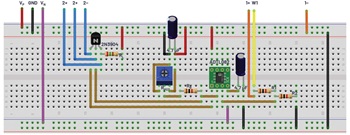

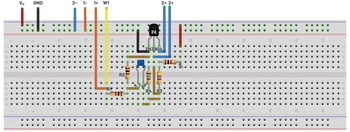

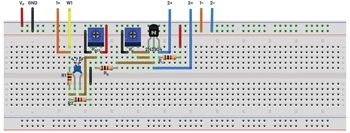

ハードウェアの設定

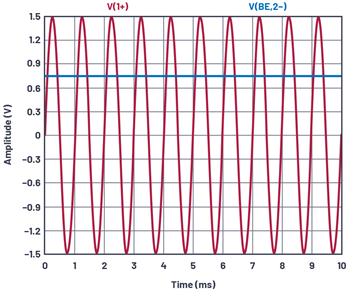

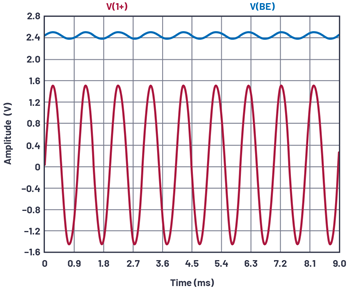

AWGのW1は、ピークtoピークの振幅が3V、オフセットが0V、周波数が1kHzの正弦波を生成するように設定します。オシロスコープのチャンネル1(1+)は、W1の出力を表示するように接続します。チャンネル2(2+)は、Q1のベースとコレクタにおける波形を交互に測定するために使用します。

手順

Q1のコレクタに接続した電源Vp(5V)をオンにします。

オシロスコープは、数周期分の入力信号と出力信号が表示されるように設定します。

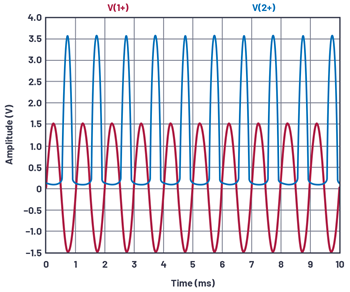

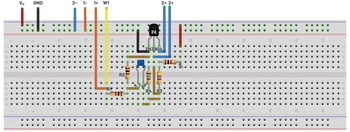

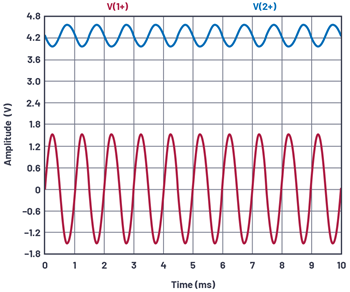

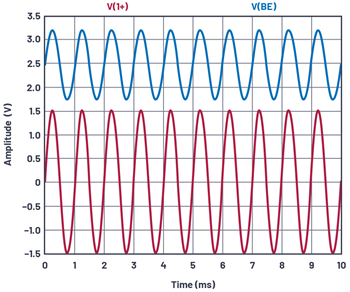

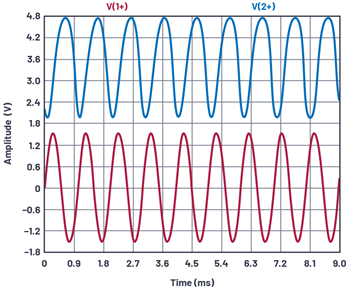

図3、図4は、LTspice®によって図1の回路のシミュレーションを行った結果です。

エミッタ接地回路の電圧ゲインAは、小信号等価モデルにおけるエミッタ抵抗reに対する負荷抵抗RLの比で表されます。トランジスタのトランスコンダクタンスgmは、コレクタ電流ICと熱電圧と呼ばれるkT/qの関数となります(以下参照)。

ここで、kT/qの値は室温で約25mVまたは26mVに近似できます。エミッタ抵抗reの値は1/gmで、エミッタと直列に存在すると見なすことができます。信号をベースに印加すると、reとRLには(ベース電流を無視すると)同じ値の電流が流れます。したがって、ゲインAは以下の式で表せます。

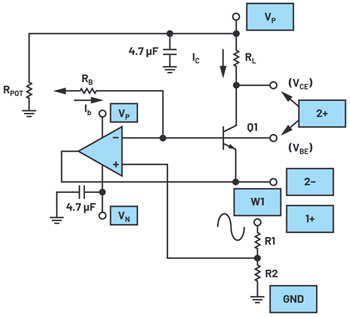

図5に示したのは、エミッタ接地回路のもう1つの構成例です。図1の回路と大きな違いがあるわけではありませんが、小さなメリットが2つあります。1つは、ベース電流のバイアスが、ベース電圧VBEの指数関数に依存しないことです。もう1つは、W1からの小振幅のAC信号が、ベース用のバイアス回路とは独立して加算されることです。つまり、AC結合は必要ありません。小振幅のAC信号はオペアンプの非反転端子に入力され、負帰還によってQ1のベース(オペアンプの反転入力)にも現れます。

負帰還による自己バイアス回路

続いて、負帰還の追加により得られる効果について検討してみます。

目的

ここで検討するのは、負帰還の追加により、DC動作点がどのように安定化されるのかということです。トランジスタ回路で最もよく用いられるバイアス回路の1つが、自己バイアス方式のエミッタ用バイアス回路です。この回路では、1つ以上のバイアス抵抗を使用し、トランジスタに関する3つの電流IB、IC、IEの初期DC値を設定します。

ハードウェアの設定

AWGのW1は、ピークtoピークの振幅が3V、オフセットが0V、周波数が1kHzの正弦波を生成するように設定します。オシロスコープのチャンネル1(1+)は、W1の出力を表示するように接続します。チャンネル2(2+)は、Q1のベースとコレクタにおける波形を交互に測定するために使用します。

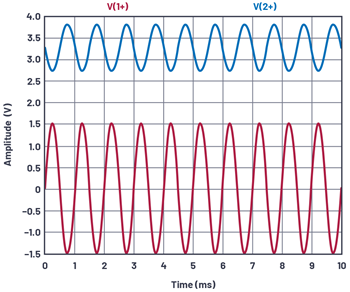

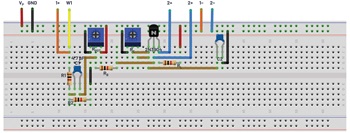

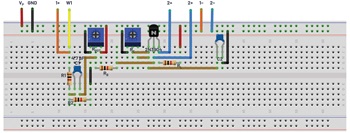

図10. 図9の回路を実装したブレッドボード

手順

Q1のコレクタに接続されている電源Vp(5V)をオンにします。

オシロスコープは、数周期分の入力信号と出力信号が表示されるように設定します。

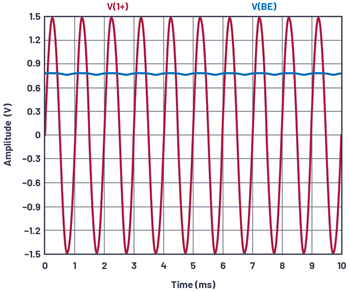

図11、図12は、LTspiceによって図9の回路のシミュレーションを行った結果です。

エミッタ・ディジェネレーションの追加

続いて、エミッタ・ディジェネレーションの例を示します。

目的

ここでは、エミッタ・ディジェネレーション用の回路を追加します。それによって得られる効果について調べてみましょう。

背景

エミッタ接地回路を使えば、非常にゲインが高い反転増幅回路を構成できます。但し、使用するトランジスタによっては、かなりのばらつきが生じる場合があります。ゲインは、温度とバイアス電流に大きく依存します。そのため、実際のゲインを予測するのは困難です。この問題は、値の小さい帰還抵抗をアンプ段に追加することにより解消することができます。つまり、回路の性能を改善することが可能になります。

追加で準備するもの

エミッタ・ディジェネレーションを施した回路を構成するために、追加の部品を使用します。

- 可変抵抗(ポテンショメータ):5kΩ(1個)

説明

図13に示すように、Q1のエミッタをグラウンドから切り離し、5kΩの可変抵抗REを追加します。Q1のコレクタに出力信号が現れるのを確認しつつ、REの値を調整します。

ハードウェアの設定

AWGのW1は、ピークtoピークの振幅が3V、オフセットが0V、周波数が1kHzの正弦波を生成するように設定します。オシロスコープのチャンネル1(1+)は、W1の出力を表示するように接続します。チャンネル2(2+)は、Q1のベースとコレクタにおける波形を交互に測定するために使用します。

手順

Q1のコレクタに接続されている電源Vp(5V)をオンにします。

オシロスコープは、数周期分の入力信号と出力信号が表示されるように設定します。

図15、図16は、LTspiceによって図13の回路のシミュレーションを行った結果です。

エミッタ・ディジェネレーションによるACゲインの変化

エミッタ・ディジェネレーション用の抵抗を追加すると、DC動作点の安定性が高まります。その代わりに、アンプ回路としてのゲインが低下します。この問題に対応するためには、図17に示すようにコンデンサC2をREと並列に追加します。そうすることで、AC信号に対するゲインをいくらか高めることができます。

ハードウェアの設定

AWGのW1は、ピークtoピークの振幅が3V、オフセットが0V、周波数が1kHzの正弦波を生成するように設定します。オシロスコープのチャンネル1(1+)は、W1の出力を表示するように接続します。チャンネル2(2+)は、Q1のベースとコレクタにおける波形を交互に測定するために使用します。

図18. 図17の回路を実装したブレッドボード

手順

Q1のコレクタに接続されている電源Vp(5V)をオンにします。

オシロスコープは、数周期分の入力信号と出力信号が表示されるように設定します。

図19、図20は、LTspiceによって図17の回路のシミュレーションを行った結果です。

問題

- エミッタ接地回路において、RLの値を大きくすると、電圧ゲインA にはどのような影響が生じますか。

答えはStudentZoneで確認できます。