AD9545

RECOMMENDED FOR NEW DESIGNSQuad Input, 10-Output, Dual DPLL/IEEE 1588, 1 pps Synchronizer and Jitter Cleaner

- Part Models

- 2

- 1ku List Price

- Starting From $22.09

Overview

- Dual DPLL synchronizes 1 Hz to 750 MHz physical layer clocks, providing frequency translation with jitter cleaning of noisy references

- Complies with ITU-T G.8262 and Telcordia GR-253

- Supports Telcordia GR-1244, ITU-T G.812, ITU-T G.813, ITU-T G.823, ITU-T G.824, ITU-T G.825, and ITU-T G.8273.2

- Continuous frequency monitoring and reference validation for frequency deviation as low as 50 ppb (5 × 10−8)

- Both DPLLs feature a 24-bit fractional divider with 24-bit programmable modulus

- Programmable digital loop filter bandwidth: 10−4Hz to 1850Hz

- 2 independent, programmable auxiliary NCOs (1 Hz to 65,535 Hz, resolution < 1.37 × 10−12 Hz), suitable for IEEE 1588 Version 2 servo feedback in PTP applications

- Automatic and manual holdover and reference switchover, providing zero delay, hitless, or phase buildout operation

- Programmable priority-based reference switching with manual, automatic revertive, and automatic nonrevertive modes supported

- 5 pairs of clock output pins with each pair usable as differential LVDS/HCSL/CML or as 2 single-ended outputs (1 Hz to 500 MHz)

- 2 differential or 4 single-ended input references

- Crosspoint mux interconnects reference inputs to PLLs

- Supports embedded (modulated) input/output clock signals

- Fast DPLL locking modes

- Provides internal capability to combine the low phase noise of a crystal resonator or crystal oscillator with the frequency stability and accuracy of a TCXO or OCXO

- External EEPROM support for autonomous initialization

- Single 1.8 V power supply operation with internal regulation

- Built in temperature monitor and alarm and temperature compensation for enhanced zero delay performance

The AD9545 supports existing and emerging International Telecommunications Union (ITU) standards for the delivery of frequency, phase, and time of day over service provider packet networks, including ITU-G.8262, ITU-T G.812, ITU-T G.813, ITU-T G.823, ITU-T G.824, ITU-T G.825, and ITU-T G.8273.2.

The 10 clock outputs of the AD9545 are synchronized to any one of up to four input references. The digital phase-locked loops (DPLLs) reduce timing jitter associated with the external references. The digitally controlled loop and holdover circuitry continuously generate a low jitter output signal, even when all reference inputs fail.

The AD9545 is available in a 48-lead LFCSP (7 mm × 7 mm) package and operates over the −40°C to +85°C temperature range.

Note that throughout the data sheet, multifunction pins, such as SDO/M5, are referred to either by the entire pin name or by a single function of the pin, for example, M5, when only that function is relevant.

APPLICATIONS

- Global positioning system (GPS), PTP (IEEE 1588), and synchronous Ethernet (SyncE) jitter cleanup and synchronization

- Optical transport networks (OTN), synchronous digital hierarchy (SDH), and macro and small cell base stations

- Small base station clocking, including baseband and radio

- Stratum 2, Stratum 3e, and Stratum 3 holdover, jitter cleanup, and phase transient control

- JESD204B support for analog-to-digital converter (ADC) and digital-to-analog converter (DAC) clocking

- Cable infrastructures

- Carrier Ethernet

Documentation

Data Sheet 1

User Guide 2

Application Note 1

Technical Articles 1

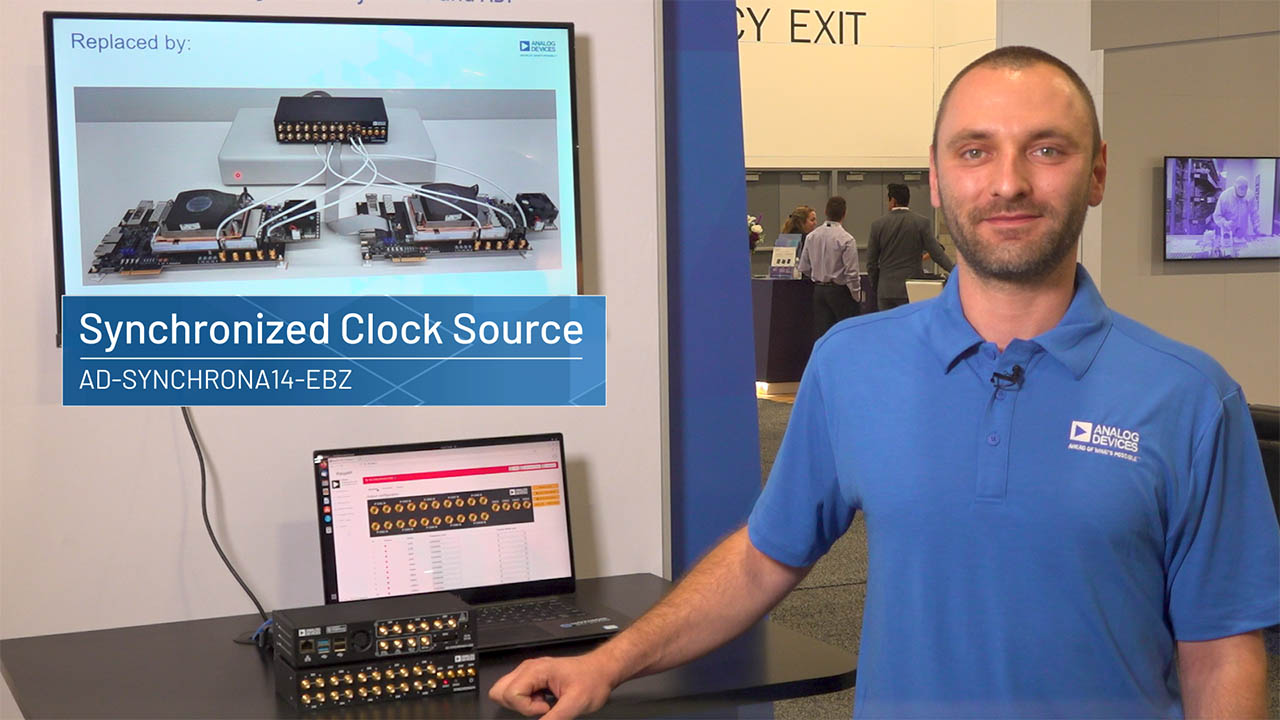

Video 1

Device Drivers 2

Webcast 1

ADI has always placed the highest emphasis on delivering products that meet the maximum levels of quality and reliability. We achieve this by incorporating quality and reliability checks in every scope of product and process design, and in the manufacturing process as well. "Zero defects" for shipped products is always our goal. View our quality and reliability program and certifications for more information.

| Part Model | Pin/Package Drawing | Documentation | CAD Symbols, Footprints, and 3D Models |

|---|---|---|---|

| AD9545BCPZ | 48-Lead LFCSP (7mm x 7mm x 0.75mm w/ EP) | ||

| AD9545BCPZ-REEL7 | 48-Lead LFCSP (7mm x 7mm x 0.75mm w/ EP) |

| Part Models | Product Lifecycle | PCN |

|---|---|---|

|

Aug 8, 2022 - 22_0065 Data Sheet Revision for AD9543/AD9545/AD9546 |

||

| AD9545BCPZ | PRODUCTION | |

| AD9545BCPZ-REEL7 | PRODUCTION | |

|

Sep 21, 2020 - 20_0271 AD9545 specifications change as relates to the system clock input and usage of the 2x frequency multiplier. |

||

| AD9545BCPZ | PRODUCTION | |

| AD9545BCPZ-REEL7 | PRODUCTION | |

|

Sep 6, 2018 - 18_0109 AD9545 Data Sheet Specification Changes |

||

| AD9545BCPZ | PRODUCTION | |

| AD9545BCPZ-REEL7 | PRODUCTION | |

This is the most up-to-date revision of the Data Sheet.

Software Resources

Evaluation Software 0

Can't find the software or driver you need?