Digital Power: Why Should I Care About Accuracy?

We looked at why we care about the digital side of Digital Power in the last post, but what about the analog side of digital power? Does the accuracy at the other end of the Digital Power device matter? It turns out, it matters more than most people realize.

An example error budget

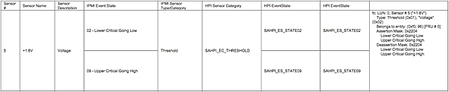

Let’s use an actual IC specification and consider how accuracy plays into it. We will use a high end FPGA. The parametric table (below) for the FPGA determines the power supply voltages over which the IC is guaranteed to operate. If the power supply is outside this range, the device is not guaranteed to operate.

Figure 1. FPGA Parametric Spec.

Let’s focus on the VCC rail that has a ±30mV around a nominal of 0.85V. For the 0.85V rail, the error is ±3.5%.

At first glance one would assume that a ±3% POL would handle this. Unfortunately, there are other considerations.

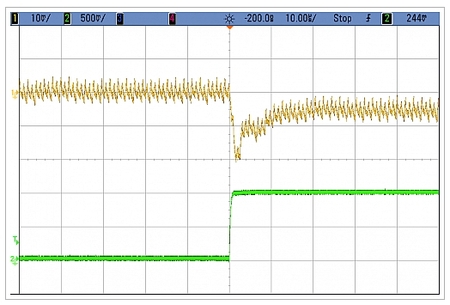

Figure 2. 10A POL Load Response.

This scope shot shows a 10A load pulse at the VCC POL output. There is about 8mV of ripple, and a short drop of 20mV. This begs the question whether these artifacts must be within the ±3.3% spec? The waveform in the scope shot is at the output of the POL. We must ask what does the load see.

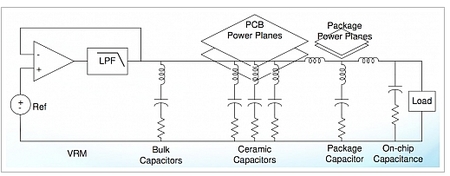

This schematic view of a PDN from DesignCon 2006 “Comparison of Power Distribution Network Design Methods” shows filtering in the package and chip. The PDN, package decoupling, and on-chip capacitance may filter out some of the high frequency portion of the transient. Therefore, the answer to the question of margin for the transient is: it depends. In general, only the package end of the PDN will filter out the highest frequencies.

Figure 3. PDN Schematic.

Ripple is another matter. Ripple is lower in frequency and whatever ripple you see on the pin of the load will be seen on the chip. So for the purpose of our analysis, we will assume ripple consumes part of the error margin, and ignore the transient.

Given our 8mV of ripple, we have only ±2mV left in the error budget, or an accuracy of approximately ±2.5%. Unfortunately, we are not done. We have to consider the over-voltage (OV) and under-voltage (UV) supervisors. If you refer back to the post “Digital Power supervision and telemetry,” the OV/UV supervisors are comparators with DACs that set trip points. Our concern is the under and over voltage accuracy.

The accuracy of the supervisor is part of the error budget, because we want to set the UV supervisor higher than the spec by its accuracy, and the OV supervisor lower than the spec by its accuracy. This is the only way to guarantee the rail is meeting the power supply specification for the IC. (Note, we can typically add some filtering to the supervisor so that transients don’t trip it, but the ripple will always trip it.)

Now, let’s use the accuracy from an LTC3880 supervisor, which is ±2%. On our 0.85V rail that is 17mV. Now we only have 4mV left in the budget! The POL output voltage accuracy now has to be 0.5%! Can we do that?

The LTC3880 datasheet shows the output accuracy with server on is ±0.5%. Wow, we have a rail that meets spec, while guaranteeing it with the supervisor, which will optionally trip and shutdown if the spec is not met, and send a fault to the baseboard management controller (BMC) we considered in the last post.

Let’s review the math

FPGA Spec: 30mV

Remove Ripple: 22mV

Remove Supervisor Accuracy: 4mV

Remove Control Loop Accuracy: 0mV

Can we compromise?

That depends on your expected quality level. If you move the supervisors outside the specification and rely on the control loop, the required accuracy of the control loop is 2%, and the LTC3880 is 4X better. This means it could support a rail even lower than 0.85V. However, there is one last dimension we have not considered. Just when you thought we were done, there is more.

What about margining?

In a production environment a power supply system is run at or beyond high and low specification values to weed out any marginalities in the system. In our design case, that means running the system at ±3.5%. The supervisors will get moved out of the way a bit during margining, because the goal is to ensure the system is reliable over the whole specification range.

Because we have to guarantee operation at the extremes, we will have to set the rails beyond the extremes by the accuracy of the control loop to ensure the actual value is at the extreme or beyond. If the control loop accuracy is 0.5%, we have to set the rail to ±4%. But what if we only had a control loop accuracy of 2%, similar to the supervisor? The values would have to be ±5.5%.

No big deal, right?

If the FPGA application loses timing margin due to higher margin values, margin testing might start producing costly failures. You may have to add timing margin to the design to pass margin tests, and if you can’t tolerate that, you may have a yield loss. Or, you can reduce the margin values and lower quality, by allowing escapes. Either way you lose or your customer loses. If you do the right thing and set the margin values correctly, you will delay your project and you will lose yield and hurt your bottom line. If you cheat the margin test, your customer loses because their system will not be reliable. So the control loop accuracy really matters. It is a big deal.

Reading the specs

Be careful with manufacturer specifications. Each manufacturer uses their own structure when specifying accuracy. The control loop accuracy will be made up of multiple components:

- Voltage Difference Amplifier offset and gain

- Voltage Reference for ADC

- ADC offset and gain

- Contributions from external components such as resistor dividers

Sometimes a datasheet specifies these separately or omits some of them from the specification, or does not directly specify the accuracy of the output at all. The LTC3880 specifies the Total Error so that it is clear what the real world accuracy is. When comparing devices, always calculate the total error if it is not given in the datasheet. Otherwise, you might regret your selection if you have problems late in the design process, or worse yet, in mass production.

Summary

We looked at an FPGA specification and did an error budget. We discovered that there are other components to the error budget including: ripple, control loop accuracy, supervisor accuracy, and margin accuracy. Directly comparing the FPGA specification and a POL specification does not tell the whole story. The POL must be significantly more accurate than the FPGA datasheet to guarantee that operation remains within spec, and to guarantee both reliability over the specification range, while maintaining high yield in production.