AN-2615: GMSL2升级至GMSL3

摘要

本文详细介绍了将现有GMSL2™设计升级为GMSL3™设计时的考量因素。在具体示例中,使用了一对GMSL2传感器(MAX96717和MAX96716A)及一对引脚兼容的GMSL3传感器(MAX96793和MAX96792A)。本文讨论了GMSL3的优势,并解释了从GMSL2升级到GMSL3时的设计考量因素。

引言

GMSL™技术的主要优势之一在于实现了同一代器件之间的跨代兼容。GMSL2向后兼容GMSL1™,GMSL3向后兼容GMSL2;通过数据手册,可验证器件的兼容性。这种灵活性还意味着,可以通过保留相同的引脚和封装去复用现有的兼容器件设计,从而节省开发时间。

GMSL3概述

GMSL3的主要不同之处是链路上的GMSL数据速率翻倍,达到12Gbps。GMSL2通常足以应对大多数应用,但传感器和显示器的带宽仍在不断提高。GMSL3旨在实现更高的数据速率,同时保留GMSL的所有优势,包括自适应均衡(AEQ)、ASIL-B功能安全性和强大的错误监控诊断。

GMSL2 使用非归零(NRZ)调制,其奈奎斯特频率为传输数据速率的一半。因此,对于6Gbps链路,该频率为3GHz(或对于3Gbps链路,该频率为1.5GHz)。在仍然使用NRZ调制的情况下,数据速率翻倍意味着对于12Gbps链路,奈奎斯特频率为6GHz。然而,使用更高频率会带来一些问题,例如线缆、连接器和PCB的插入损耗增加,导致应用中线缆的总长度必须缩短。

为了避免在数据速率翻倍的情况下使用更高频率,GMSL3采用脉冲幅度调制4级(PAM4),以保持与GMSL2 相同的奈奎斯特频率。较低的通道工作频率会给系统带来许多好处:

- GMSL2和GMSL3使用相同的时钟链路速率,支持原理图和布局复用,工作在FR-4 PCB上。

- 线缆和连接器的插入损耗更低。

- 通过翻倍带宽并保持相同的链路速率,可以获得更高的频谱效率。

GMSL3 同时支持6Gbps (NRZ)和12Gbps (PAM4)。

设计考量因素

这里以CSI-2至GMSL3串行器MAX96793和GMSL3至CSI-2解串器MAX96792A为例进行说明。一般来说,升级所需的改动很少,但针对每一个具体的系统应用仍然需要进行评估。

引脚兼容性

GMSL2代和GMSL3代的GMSL器件被设计为引脚兼容,以支持设计复用。串行器封装为5mm x 5mm TQFN。图1详细展示了MAX96717和MAX96793的引脚排列:

在这些器件上使用反向信道参考时钟(RoR)功能时,应将一个20nF±10%的电容连接在VREF引脚(引脚7)和接地端之间。为了保持最优反向链路裕量,此连接对使用RoR的GMSL3模式是必须的,但对GMSL2模式并非强制要求。

如果在GMSL3上不使用RoR,则不需要此电容。

解串器封装为7mm x 7mm TQFN。图2详细展示了MAX96716A和MAX96792A的引脚配置:

功耗

这些器件的功耗是在物理层接口满负荷运行状态下进行测定的,运行条件在表1的配置列详细列出。

| 器件 | 配置 | IDD18 | IDD (VDD = 1.2V) | PTOTAL |

| MAX96717 | 6Gbps前向链路速率 (GMSL2模式) RGB888彩条图案 4通道CSI-2 DPHY输入 每通道1.3Gbps |

46mA (25°C) 53mA (105°C) |

98mA (25°C) 232mA (105°C) |

~210mW (25°C) ~393mW (105°C) |

| MAX96793 | 12Gbps前向链路速率 (GMSL3模式) RGB888彩条图案 4通道CSI-2 DPHY输入 每通道2.5Gbps |

46mA (25°C) 53mA (105°C) |

170mA (25°C) 340mA (105°C) |

~301mW (25°C) ~529mW (105°C) |

这两款器件使用相同的电源输入电压,以简化电源拓扑要求。MAX96717和MAX96793 GMSL器件系列的 VDD18轨使用相同的电源。VDD核心轨的最大电流仅有轻微增加,幅度约为70mA (25°C)或110mA (105°C)。检查电源,确保供电轨上有足够的裕量以适应电流增加。

如前所述,这些器件的特点是其配置旨在充分发挥物理层接口能力,即解串器同时支持双GMSL输入和双MIPI-CSI2输出。这些器件可以仅使用单个GMSL输入和/或单个MIPI-CSI2输出,以降低总功耗。

此外,摄像头解串器具有MIPI-CSI2供电轨 VTERM,用于MIPI-CSI2 PHY。

| 器件 | 配置 | IDD18 | IDD (VDD = 1.2V) | ITERM | PTOTAL |

| MAX96716A | 6Gbps前向链路速率 (GMSL2模式) 2x 6Gbps输入 2x 4通道CSI-2 DPHY 输入 每通道1.3Gbps |

196mA (25°C) 245mA (105°C) |

197mA (25°C) 460mA (105°C) |

27mA (25°C) 40mA (105°C) |

~654mW (25°C) ~1095mW (105°C) |

| MAX96792A | 12Gbps前向链路速 率(GMSL3模式) 2x 12Gbps输入 2x 4通道CSI-2 DPHY 输入 每通道2.5Gbps |

210mA (25°C) 250mA (105°C) |

365mA (25°C) 850mA (105°C) |

31mA (25°C) 40mA (105°C) |

~898mW (25°C) ~1596mW (105°C) |

这两款器件使用相同的电源输入电压,以简化电源拓扑要求。MAX96716A和MAX96792A GMSL器件系列的VDD18 轨使用大致相同的电源。VDD核心轨的最大电流有所增加,幅度增加约为160mA (25°C)或390mA (105°C)。检查电源,确保供电轨上有足够的裕量以适应电流增加。

此外,两款器件的静态电流消耗和最大电源噪声容差相同,以使这两个系列遵循一致的系统要求。

配置引脚设置

这些器件的配置引脚差异很小。务必根据器件数据手册确认配置引脚值,这将决定器件每次启动时的配置状态。

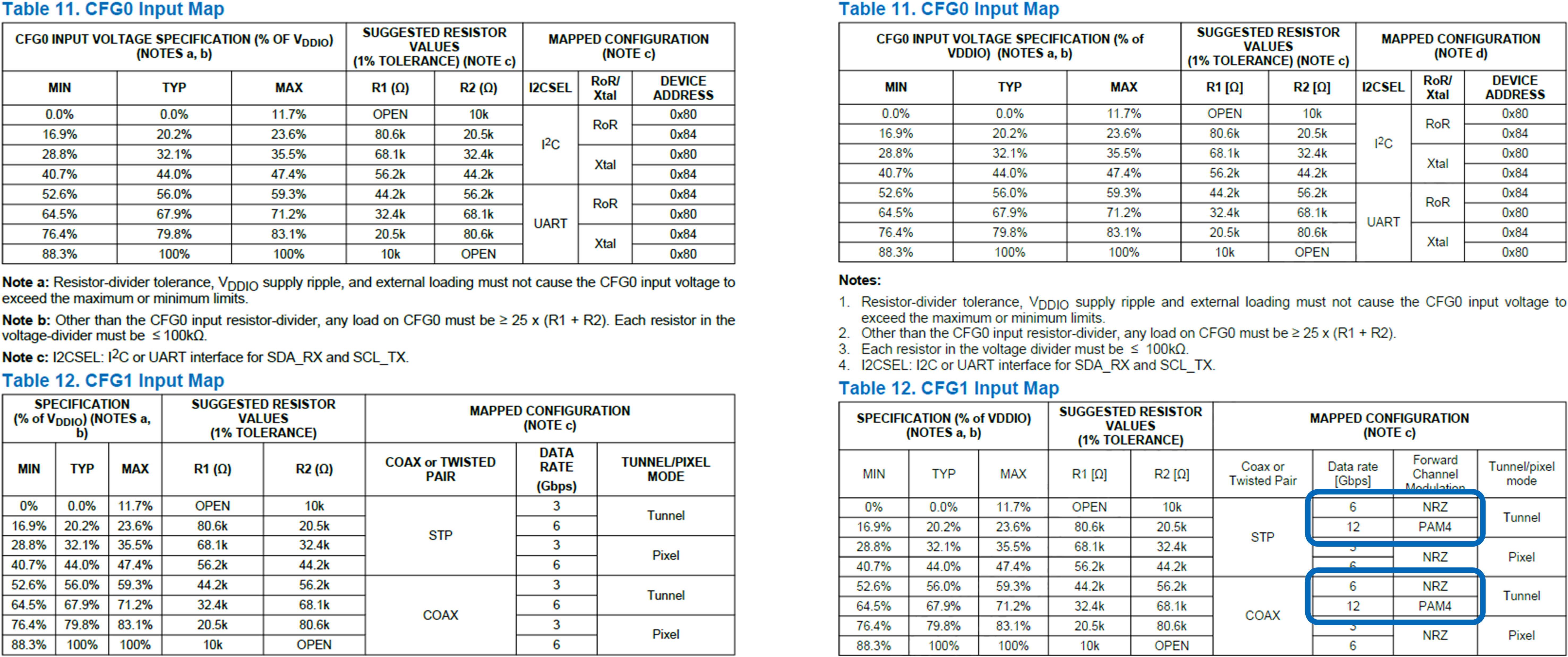

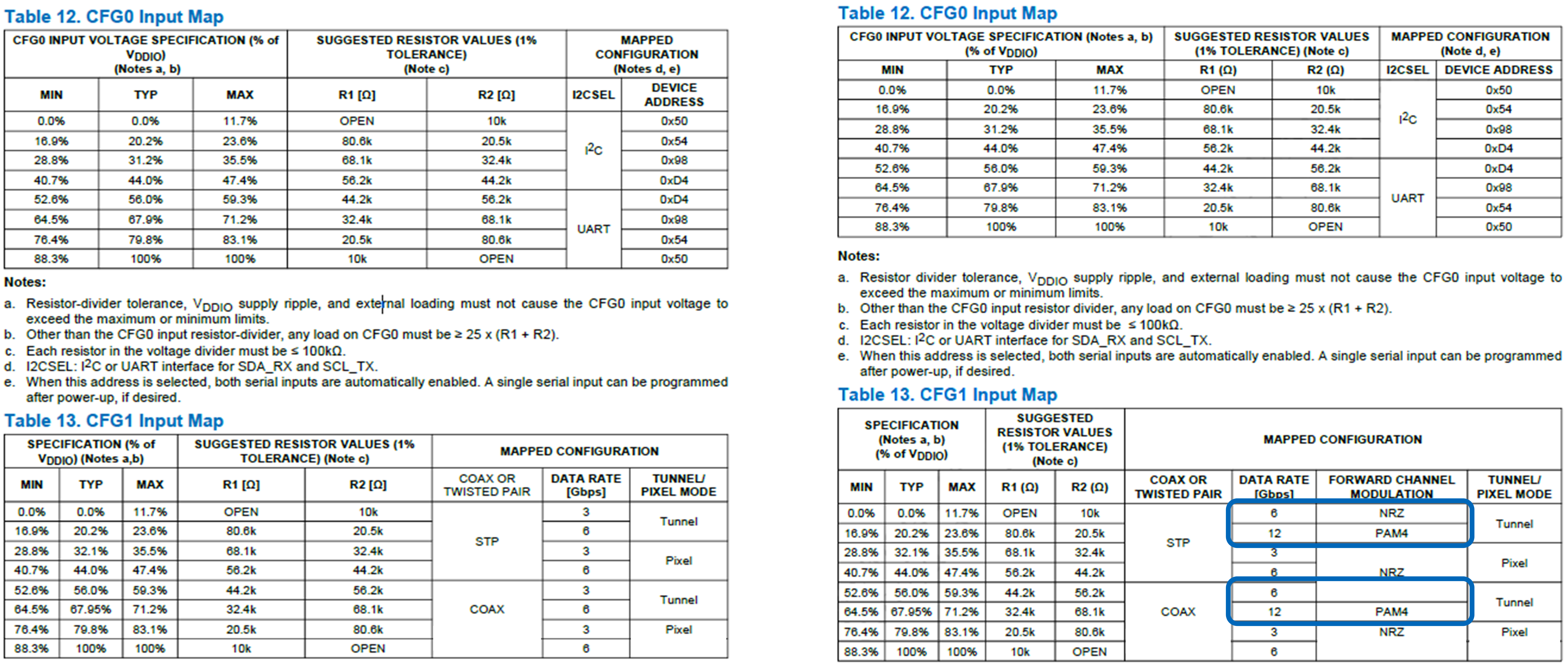

图3和图4展示了配置引脚的详细信息,这里以MAX96717和MAX96793为例进行说明。所有配置引脚的设置都取决于具体器件,详细信息请参考各自的数据手册。

配置0引脚(CFG0)用于配置UART和 I2C之间的信道接口,选择使用RoR还是晶振,以及器件地址。

配置1引脚(CFG1)用于配置线缆类型(STP还是同轴线缆)、GMSL数据速率,以及选择隧道模式还是像素模式。CFG1在设置GMSL数据速率方面有细微差异。这些器件的像素模式数据速率相同。隧道工作模式支持GMSL3的6Gbps和12Gbps,以及GMSL2的3Gbps和6Gbps。

PAM4调制方案

PAM4是GMSL针对严苛的汽车环境所采用的一种成熟调制方案。NRZ使用两个电压电平表示1位符号,而PAM4使用四个电压电平表示2位符号,使得GMSL3能够以与GMSL2相同的波特率运行,同时将所传输数据的比特率翻倍。

然而,数据速率翻倍并非没有代价:PAM4的眼图开度较小,约为NRZ眼图开度的1/3。

图5中,“A”被定义为NRZ眼图开度,这意味着如果NRZ以A的SNR每个周期传输1位(1/T),则PAM4以A/3的SNR每个周期传输2位(2/T)。

前向纠错

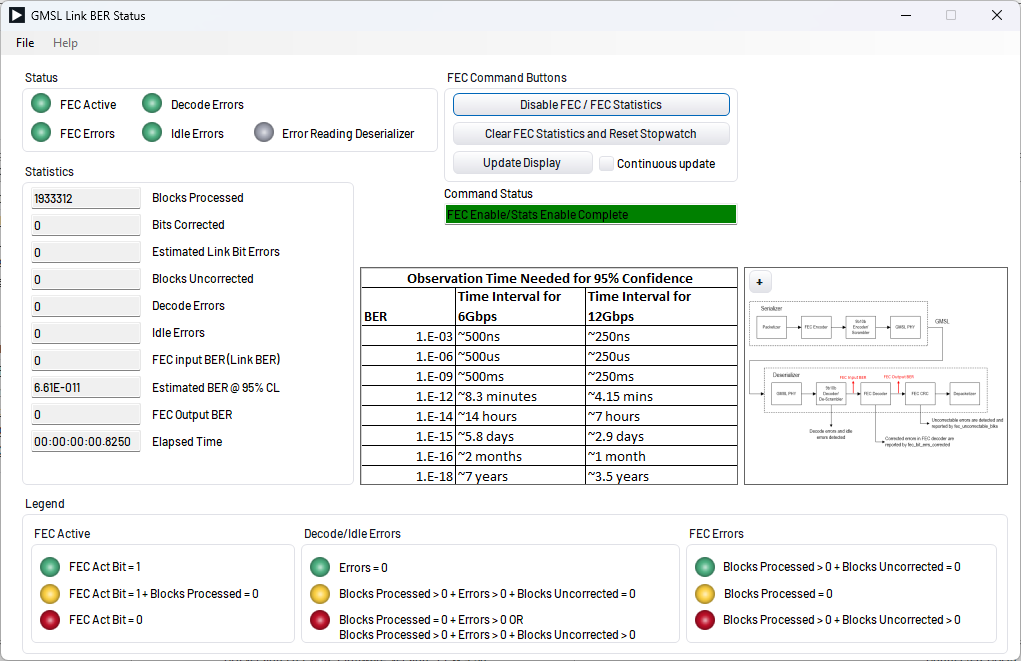

为了克服 PAM4 固有的噪声敏感性,GMSL3 具备前向纠错(FEC)功能,可为链路增加数据冗余和纠错能力。FEC 可以显著降低SNR要求,并有助于降低链路的误码率(BER),使得GMSL链路在整个生命周期内只有一个位错误。

GMSL FEC采用Reed-Solomon 编码,这种编码广泛用于CD、二维码,甚至旅行者航天器[1]。此外,FEC信息可通过寄存器实时监控,或在GMSL GUI中方便地监控。

FEC 是GMSL3的强制要求,因此在确认用例是否具有足够的带宽时,需要考虑FEC对带宽的影响。为了增强BER鲁棒性,在GMSL链路上使用FEC会产生6.67% (128/120)的额外开销。GMSL GUI中的GMSL带宽计算器在计算中包括了这一开销。此开销使得GMSL3链路的实际可用带宽大约为9.7Gbps。

错误报告

在GMSL3链路上使用FEC时,需要根据系统监控要求,调整错误监控策略。FEC可以检测并纠正链路上发生的错误,器件会报告纠正情况,这称为“FEC可纠正位”。“FEC不可纠正位”是不被允许的,因为它意味着GMSL3器件无法修复链路上发生的错误。

因此,需要根据错误的定义,调整错误监控策略。对于GMSL2 模式,解码和空闲错误用于报告链路上发生的错误。对于GMSL3模式,FEC不可纠正错误用于报告链路上的错误;FEC纠正的位也会被报告。

默认情况下,FEC错误标志用于检查可纠正和不可纠正的位,并报告给ERRB引脚。可纠正位的FEC阈值必须根据系统要求进行调整。有关错误监控变更的详细信息,请参阅软件差异部分。

通道规格

GMSL2 和 GMSL3 之间的一个显著区别是GMSL通道规格。请勿认为符合规范的GMSL2系统与GMSL3通道规范兼容,因为后者的预算限制更严格。请参考www.analog.com/cn上提供的最新GMSL2通道规范和GMSL3通道规范。

复用设计时,务必重新评估PCB布局和布线需求。

GMSL3 (12Gbps)和 GMSL2 (6Gbps)均以 3GHz 链路基频运行。

GMSL3 的插入损耗要求额外规定了长通道(高损耗)和短通道(低损耗)两种情况。短通道的插入损耗(IL) 更严格,但回波损耗(RL)较宽松。

GMSL3 的回波损耗要求也额外规定了长通道(高损耗)和短通道(低损耗)两种情况。短通道的RL较宽松,但IL更严格。

S-参数数据在与 GMSL3 IL 和 RL 限值进行比较之前,必须进行滤波。在全部范围内对S-参数应用100MHz滤波器。从最低捕获频率到50MHz,应用未滤波的数据。超过50MHz时,使用经滤波的数据与限值进行 比较。

寄存器设置差异

在软件方面,这些器件之间有两大差异:GMSL3工作模式和错误监控。

对于GMSL3模式,表3和表4中详细列出的以下所有更改都通过CFG引脚处理。这些引脚用于正确配置器 件的发送和接收速度,以及PAM4调制。表3和表4列出了当软件对CFG引脚进行编程或覆写操作时需使 用的寄存器,但此类操作通常不建议采用。

注:如果使用CFG引脚配置GMSL模式,则表3和表4中显示的以下更改不是必需的。

编程步骤需要按照特定顺序进行。先从远程器件开始,然后再处理本地器件。“远程”和“本地”指的是 I2C控制器的位置。对本地器件进行编程时,会阻止其与远程器件的通信。在此示例中,MAX96793是远程器件,而MAX96792A(连接到 I2C控制器)是本地器件。

| 步骤 | 位置 | 器件 | 说明 | 寄存器 | 值 |

| 1 | 远程 | MAX96793 | 将Tx速率更改为12Gbps | 0x0001 | REG1[3:2] = 0b11 |

| 2 | 远程 | MAX96793 | 使能FEC | 0x0028 | TX0[1] = 0b1 |

| 3 | 远程 | MAX96793 | 禁用GMSL2模式并使能GMSL3模式 | 0x0006 | REG6[7] = 0b0 |

| 4 | 本地 | MAX96792A | 使GMSL链路保持RESET(复位)状态 | 0x0010 | CTRL0[6] = 0b1 |

| 5 | 本地 | MAX96792A | 将Rx速率更改为12Gbps | 0x0001 | REG1[1:0] = 0b11 |

| 6 | 本地 | MAX96792A | 使能FEC | 0x0028 | TX0[1] = 0b1 |

| 7 | 本地 | MAX96792A | 禁用GMSL2模式并使能GMSL3模式 | 0x0004 | REG4[7:6] = 0b11* |

| 8 | 本地 | MAX96792A | 使GMSL链路离开RESET(复位)状态 | 0x0010 | CTRL0[6] = 0b0 |

| *这会将两个链路都设置为GMSL3。每个链路可以单独配置。 | |||||

| 步骤 | 位置 | 器件 | 说明 | 寄存器 | 值 |

| 1 | 远程 | MAX96793 | 将Tx速率更改为6Gbps | 0x0001 | REG1[3:2] = 0b10 |

| 2 | 远程 | MAX96793 | 禁用FEC | 0x0028 | TX0[1] = 0b0 |

| 3 | 远程 | MAX96793 | 使能GMSL2模式并禁用GMSL3模式 | 0x0006 | REG6[7] = 0b0 |

| 4 | 本地 | MAX96792A | 使GMSL链路保持RESET(复位)状态 | 0x0010 | CTRL0[6] = 0b1 |

| 5 | 本地 | MAX96792A | 将Rx速率更改为6Gbps | 0x0001 | REG1[1:0] = 0b10 |

| 6 | 本地 | MAX96792A | 禁用FEC | 0x0028 | TX0[1] = 0b0 |

| 7 | 本地 | MAX96792A | 使能GMSL2模式并禁用GMSL3模式 | 0x0004 | REG4[7:6] = 0b00* |

| 8 | 本地 | MAX96792A | 使GMSL链路离开RESET (复位)状态 | 0x0010 | CTRL0[6] = 0b0 |

| *这会将两个链路都设置为GMSL3。每个链路可以单独配置。 | |||||

如错误报告部分所述,错误监控策略需要根据FEC报告进行更改。

| MAX96793 | MAX96792A | |||

| 位名称 | 寄存器 | 值 | 寄存器 | 值 |

| DEC_ERR_OEN_A | 0x001A | INTR2[0] = 0b1 | 0x001A | INTR2[0] = 0b1 |

| DEC_ERR_OEN_B | — | — | 0x001A | INTR2[1] = 0b1 |

| IDLE_ERR_OEN | 0x001A | INTR2[2] = 0b1 | 0x001A | INTR2[2] = 0b1 |

| IDLE_ERR_OEN_B | — | — | 0x5010 | INTR10[6] = 0b1 |

| FEC_RX_ERR_OEN | — | — | 0x001C | INTR4[5] = 0b0* |

| FEC_RX_ERR_OEN_B | — | — | 0x5010 | INTR10[5] = 0b0* |

| *每个链路可以单独配置。 | ||||

| MAX96793 | MAX96792A | |||

| 位名称 | 寄存器 | 值 | 寄存器 | 值 |

| DEC_ERR_OEN_A | 0x001A | INTR2[0] = 0b0 | 0x001A | INTR2[0] = 0b0 |

| DEC_ERR_OEN_B | — | — | 0x001A | INTR2[1] = 0b0 |

| IDLE_ERR_OEN | 0x001A | INTR2[2] = 0b0 | 0x001A | INTR2[2] = 0b0 |

| IDLE_ERR_OEN_B | — | — | 0x5010 | INTR10[6] = 0b0 |

| FEC_RX_ERR_OEN | — | — | 0x001C | INTR4[5] = 0b1* |

| FEC_RX_ERR_OEN_B | — | — | 0x5010 | INTR10[5] = 0b1* |

| *每个链路可以单独配置。 | ||||

使能FEC后,FEC统计信息可以根据应用要求单独配置。MAX96792A拥有许多寄存器,寄存器块地址从0x2000开始,支持读取统计信息及设置两个链路的错误阈值。

例如,应用可能允许在触发报警之前存在一定数量的可纠正位错误,则可以将CORRECTED_THRESHOLD_ 0/1/2/3 设置为允许的纠正位数量。不可纠正位错误更令人担忧,表明系统存在更大的问题。

凭借丰富的统计信息,用户可全面了解GMSL链路的健康状态。

结论

GMSL2 和GMSL3器件系列能够随设计同步扩展,文中所述细节说明了升级系统时需要考虑的变更。一般来说,GMSL2和GMSL3器件尽可能保持一致,以减轻升级时的设计负担。尽管本文详细介绍了两款特定器件的升级方法,但在进行其他GMSL2和GMSL3设备升级时,您必须查阅对应的设计文档。然而,无论是何种 GMSL器件,GMSL带宽的计算和GMSL通道的规格均遵循统一标准。

参考文献

[1] Canterbury, “QR codes - Coding - Error control - Computer Science Field Guide,” Csfieldguide.org.nz, 2024. https://www.csfieldguide.org.nz/en/chapters/coding-error-control/qr-codes.