データシートの奥深さ— 絶対最大定格と熱抵抗

要約

絶対最大定格と熱抵抗に関してよくある質問にお答えします。

期待どおりに動作しないオペアンプは、ユーザーにとって非常に苛立たしいものです。思い通りの回路設計が出来ることも多くありますが、成り立たなくしてしまう要因の方がもっと多くあるのです。残念ながら、ユーザーが直面する問題、課題、不具合の90% は、データシートを慎重に読まなかったり、読み誤ることによるものです。ここでは、絶対最大定格と熱抵抗に関してよく受ける質問をいくつか紹介します。これらの質問の答えはわかりきっているように見えますが、誤解されることがよくあります。

絶対最大定格を少しだけ上回る数値でアンプを動作させても大丈夫ですか?

絶対にいけません! デバイスに恒久的な損傷を与えないようにするためには、データシートに記載されている絶対最大定格を超えないようにすることが不可欠です。絶対最大定格はデバイスが耐えられる限界値を示しており、この値で動作できるという意味ではありません。たとえば、絶対最大定格より高い入力電圧を使用すると、オペアンプの両入力にブレークダウンが発生し、過剰な電流が流れます。この結果、性能が劣化するだけでなく、金属マイグレーションが発生することにより、時間を経るとデバイスが恒久的に破壊されます。つまり、絶対最大定格の値に近づけないようにすることです。そうしなければ、デバイスが破壊される可能性が非常に高くなります。

絶対最大定格について、詳しく教えてください。

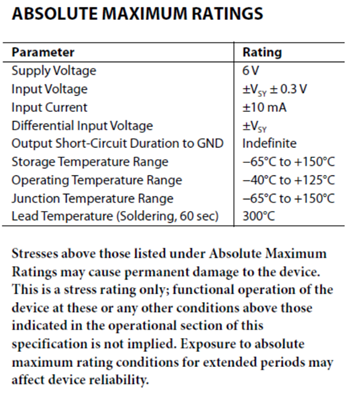

絶対最大定格表には、電圧、温度、許容される電流の限界値が記載されています。

図1. 絶対最大定格表の一例

オペアンプに印加できる最大電源電圧は製造プロセスによって決まります。これは瞬時値であり、平均値や最終値ではありません。アナログ・デバイセズの低電圧CMOS オペアンプでは通常6 V に制限されますが、高電圧バイポーラ・デバイスでは36 V に制限されます。

最大入力電圧はオペアンプの入力段のアーキテクチャと電源電圧に依存します。ほぼすべてのオペアンプがESD ダイオードによって保護されています。入力電圧が電源電圧をどれだけ超えることができるかは、入力ESD ダイオードによって決まります。通常、入力電圧は、電源レールよりダイオード1 個分の電圧降下(温度に応じて300 mV~700 mV)だけ高い電圧に制限されます。オペアンプの入力電圧が絶対最大定格の範囲内にあっても、入力電圧範囲を超えて動作させると、性能が劣化します。この場合、損傷は受けませんが、機能しなくなる恐れがあり、たとえば、位相反転が起きたり、入力バイアス電流や入力オフセット電圧が大幅に増加する可能性があります。入力電圧が絶対最大定格を超えると、オペアンプは恒久的な損傷を受けます。ユーザーは(電源シーケンシングにより)電源が供給されていないオペアンプの入力端子に電圧が印加されるという問題に直面することがよくあります。これによって絶対最大定格を超えてしまうことで、入力過電圧が生じ、デバイスが破壊される可能性があります。この問題を阻止する簡単な方法は、入力過電圧保護機能を備えたモノリシック・アンプを使用することです。ディスクリートのアナログ・ソリューションに代わる使いやすいデバイスとして、入力過電圧保護回路を搭載したデバイスが提供されています。このようなアンプの一例として、アナログ・デバイセズの過電圧保護(OVP) 付き高精度アンプADA4091-2 があります。このアンプは、損傷を受けることなく、電源電圧の上下最大25 V の入力電圧で使用できます。

最大差動入力電圧とは、過剰な電流を誘導することなく、入力端子間に印加することができる最大差動電圧のことです。オペアンプのなかには、入力段でベース・エミッタ間のブレークダウンを防止するためにバックto バック・ダイオードを内蔵しているものがあります( 図 2 参照) 。入力端子間に接続されたクランプ・ダイオードの数により、最大差動入力電圧が決まります。

図 2.差動入力電圧保護

絶対最大定格表には、入力端子に供給できる最大入力電流も記載されています。データシートに最大入力電流に関する情報が記載されていない場合は、経験則として、入力電流を常に5 mA 未満に制限します。入力電流が絶対最大定格を超えることが予測される場合は、入力に直列抵抗を挿入し(図2 参照) 、デバイスに流れ込む電流を制限します。ただし、これによってノイズが生じ、入力換算のオフセット電圧が増加するので注意が必要です。

デバイスが絶対最大定格を超えるとすぐに故障が発生しますか?

絶対最大定格を超えた時に発生する故障にはタイプがいくつかあります。

1 つめは、デバイスが絶対最大定格を超えると直ちに発生する故障です。異常に大きな電圧がアンプに印加(たとえば、耐圧6 V CMOS アンプに30 V の電源電圧が印加)されると、内部のトランジスタやジャンクションがほぼ瞬時にブレークダウンします。そしてデバイスは恒久的な損傷を受けます。

2 つめは、長時間にわたって絶対最大定格を超える状態が続くことによってデバイスに故障が発生するタイプです。デバイスが絶対最大定格を超える電圧または電流に曝されてもすぐには故障が発生しない場合がありますが、長期的に見ると結局損傷を受けることになります。たとえば、6 V アンプに7 V を印加しても、しばらくの間は耐えられます。しかし、デバイスに対して過度のストレスを与え続けると、ジャンクションが弱くなり、最終的にデバイスはブレークダウンします。この場合、デバイスの長期的な信頼性が大幅に低下します。

3 つめは、絶対最大定格を超えることによって、性能劣化とジャンクションの過熱が生じ、最終的に故障が発生するタイプです。過剰な入力電流によって性能が劣化し、金属マイグレーションが発生する可能性があります。温度が過度に上昇すると、ジャンクションの熱限界値を超えることもあります。たとえジャンクションの熱限界値を超えなくても、動作ジャンクション温度が高くなるとデバイスの寿命が大幅に短くなります。

したがって、アンプが損傷を受けないようにするためには、絶対最大定格を超えないようにすることが必要です。また、デバイス寿命を延ばすためには、絶対最大定格に対して十分な安全マージンを確保することをお勧めします。

保存温度、動作温度、ジャンクション温度、リードの半田処理温度の範囲の違いは?

保存温度は、電源が供給されていない状態でデバイスを安全に保存できる温度です。つまり、−65°C ~+150°C の温度範囲でデバイスを保存しておくことができ(図1 参照)、なおかつ、回路に使用する際には適正に機能できるということです。

動作温度は、デバイスに電源が供給されているときの周囲環境またはシステムの温度をいいます。一般に、アンプは電気的特性表に規定された動作温度範囲で機能することがテストされ規定されています。標準的な動作範囲には以下のものがあります。

商用温度範囲: 0°C ~70°C

工業用温度範囲: −40°C ~+85°C

拡張工業用温度範囲: −40°C ~+125°C

軍用温度範囲: −55°C ~+125°C

ジャンクション温度は、デバイスに電源が供給されているときのパッケージ内のシリコン・ダイの温度をいいます。ユーザーは最大定格を超えていないことを確認するために動作温度をモニタしますが、消費電力に伴って上昇する内部ジャンクション温度を考慮に入れ損なうことがよくあります。ジャンクション温度の計算については、この記事の後半で説明します。

リードの半田処理温度は、手作業で半田処理するときにパッケージの端子に加えることができる温度をいいます。図1 では、リードのハンダ処理温度の絶対最大定格である300°C が60 秒間続くと、デバイスが損傷を受ける可能性があることを示しています。ただし、信頼性の面で懸念があるため、手作業のハンダ処理は推奨しません。

アナログ・デバイセズでは、Sn-Pb 有鉛リードと無鉛リードの2 種類のパッケージ・リードを使用しています(アナログ・デバイセズはRoHS 対応に移行しているため、新製品はすべて無鉛材質のみ)。リフロー時のピーク・ハンダ処理温度は種類によって異なり、Sn-Pb 有鉛リードでは220°C、無鉛リードでは260°C です。詳細については、IPC/JEDEC standard,IPC/JEDEC J-STD-020 に記載されています。

繰返しになりますが、デバイスは必ずその動作温度限界値と最大設計温度限界値を超えないように注意してください。

熱抵抗とは何ですか?

熱抵抗は、1 つの構造体(たとえば、デバイスのジャンクション)から別の構造体(たとえば、周囲の空気)へと熱が移動する際に生じる、熱流に対する抵抗を表します。熱抵抗は、1W の熱流を放出するために必要な温度差(単位: °C/W)で表されます。熱抵抗を表すには一般に記号θ が使用されます。データシートの熱抵抗定格は、異なるパッケージのデバイス間の熱性能比較の基準になります。アナログ・デバイセズでは、熱抵抗はJEDEC 試験規格に基づいて規定されており、テスト条件はデータシートに記載されています。(JEDEC 規格はJEDEC のウェブサイトから無償でダウンロードできます)。オペアンプのジャンクション‐周囲間の熱抵抗が120°C/Wであることは、1W の電力を消費したときにデバイスのジャンクションと周囲空気の間で測定された温度差が120°C であることを示します。

なぜθJA とθJC が大事なのですか?

θJA と θJC のデータを含む、熱抵抗表の一例を図3 に示します。

図 3. 熱抵抗表の一例

θJC(ジャンクション‐ケース間の熱抵抗値)は、熱がシリコン・ダイのジャンクションとケース(パッケージの上面または底面)の間を移動するときに熱流が受ける抵抗を示します。θJC は、ダイの厚さ、表面面積、熱流経路にあるデバイス材料の熱伝導率によって決まります。JEDEC 試験規格では、θJC はすべての熱がパッケージの上面を通ってヒートシンクに流れると仮定して定義されています。この定義によれば、パッケージの側面や底面には熱は流れません。したがって、θJC が有効なのは、パッケージがヒートシンクに直接実装されているときだけです。θJC が小さいほど、熱がヒートシンクへ流れやすくなります。

ここで、

TJ = ジャンクション温度

TC = ケース(パッケージ表面) 温度

PD = パッケージの消費電力

θJA(ジャンクション‐周囲空気間の熱抵抗値)は、熱がシリコン・ダイから周囲の(静止した) 空気へ移動するときに熱流が受ける抵抗を示します。また、あらゆる経路を介したジャンクションから周囲の空気への熱流の状態も示します。ほとんどの場合、主な熱流経路は端子から基板となります。よって、θJAは、外部ヒートシンクなしで使用されるパッケージに適用されます。実際には、θJA は周囲環境と取付け方法の影響を受けます。空気の循環やソケットの使用方法が悪いと、熱抵抗が大幅に増加する可能性があります。ファンを使ってエアフローを生成したり、幅広い基板パターンにデバイスをハンダ付けすることで、放熱を増やすことができます。これは、ジャンクション‐周囲間の熱抵抗を減らすのに役立つので、ジャンクション温度を低下させます。

ここで TA = 周囲温度。

θJA はほとんどの場合パッケージ定格内に使用され、システムの熱性能の予測に使用するべきではない、ということに注意してください。これは、同じ環境でテストされる異なるパッケージ間の熱性能の比較の基準になります。θJA の値が小さくなることは、デバイスの熱性能が向上し、過熱しにくくなることを示します。パッケージが大きくなり、表面面積が大きくなると、より効率的に放熱できるので、通常、熱抵抗は小さくなります。

周囲温度と消費電力がわかっている場合、θJA を使ってダイのジャンクション温度を計算することもよくあります。ただし、θJA が有用な情報となるのは、システムの環境がJEDEC で定義されたテスト環境とほぼ同一であるときだけです。θJA は基板設計(内層の数、存在する他の加熱要因、銅パターンの量など)やテスト環境条件に大きく依存します。

一言アドバイス:温度計算では、θJA は十分に注意して使用しなければなりません。通常、θJA を使うと、実際の環境とテスト環境との違いによって熱計算が不正確になります。

絶対最大定格を超えないようにするには、ジャンクション温度をどのように概算したらよいですか?

熱試験規格と全く同じテスト条件を使用したと仮定すると、ダイのジャンクション温度は次式を使って計算できます。

TA は既知の値で、θJA は与えられた値です。パッケージの消費電力は次式で求められます。

ここで、

ISY × VSY は静止時の消費電力を指します。

ILOAD × (VSY − VOUT)は出力段トランジスタの消費電力です。

たとえば、図4 のように構成されたデュアルAD8622(SOIC パッケージ)の両チャンネルの消費電力は合計で66 mWになります。

図 4.ユニティ・ゲインの電圧フォロワー

周囲温度が25°C の場合、TJ は次式で計算できます。(熱抵抗値については、図3 を参照してください)。

クワッドのAD8624 (TSSOP パッケージ) を使用した場合は、消費電力は倍の132 mWになり、ジャンクション温度は39.78°C に上昇します。

信頼性の高い設計を行うには、熱抵抗の低い銅のパターン面積を広くした放熱効果の高い基板回路を準備し、複数のビアを備えた多層を使ってパッケージから放熱しやすくします。また、熱抵抗の低いパッケージを選択するか、あるいは、負荷を小さくしたり電源電圧を下げることで消費電力を減らします。基板の局所的な消費電力を減らすために、デュアルよりシングル、クワッドよりもデュアルがよく選択されます。

最後に、パッケージに露出サーマル・パッドがついているのですが、これをどう取り扱えばよいでしょうか?

LFCSP パッケージ(図5 参照)は小型で、通常、(底面に)放熱のための露出パッドを備えています。露出パッドはヒートシンクの役割を担っており、周囲への熱伝導を良好にする基板の金属領域にハンダ付けする必要があります。露出サーマル・パッドをハンダ付けする場所(グラウンド、負電源ピン、正電源ピンのいずれか)は、データシートに規定されています。多くの場合、このような接続が行われていると仮定してθJA がテストされています。このような接続が行われないと熱抵抗が規定値よりも大きくなります。

図 5. 露出サーマル・パッドを備えたLFCSP パッケージ